简介:M序列,又称LFSR序列,广泛应用于数字通信、密码学等领域。本压缩包提供完整的m序列VERILOG源代码、工程文件和测试程序,旨在帮助开发者理解LFSR的工作原理并进行硬件验证。源代码使用VERILOG语言编写,定义了一个基于线性反馈函数的LFSR结构,通过时序逻辑实现序列的生成。工程文件包含编译脚本、仿真模型和约束文件,方便在不同环境中复现和测试设计。测试程序验证了生成的序列是否满足M序列的特性,如正确的周期和零自相关性。

1. M序列简介

M序列,也称为伪随机序列,是一种具有统计随机性质的确定性序列。它广泛应用于通信、密码学和雷达等领域。M序列的生成通常使用线性反馈移位寄存器(LFSR),它是一种具有反馈功能的时序逻辑电路。本篇文章将深入探讨M序列的特性、LFSR的结构和工作原理,以及如何使用VERILOG语言描述和设计M序列时序逻辑。

2. LFSR结构及工作原理

2.1 LFSR的结构

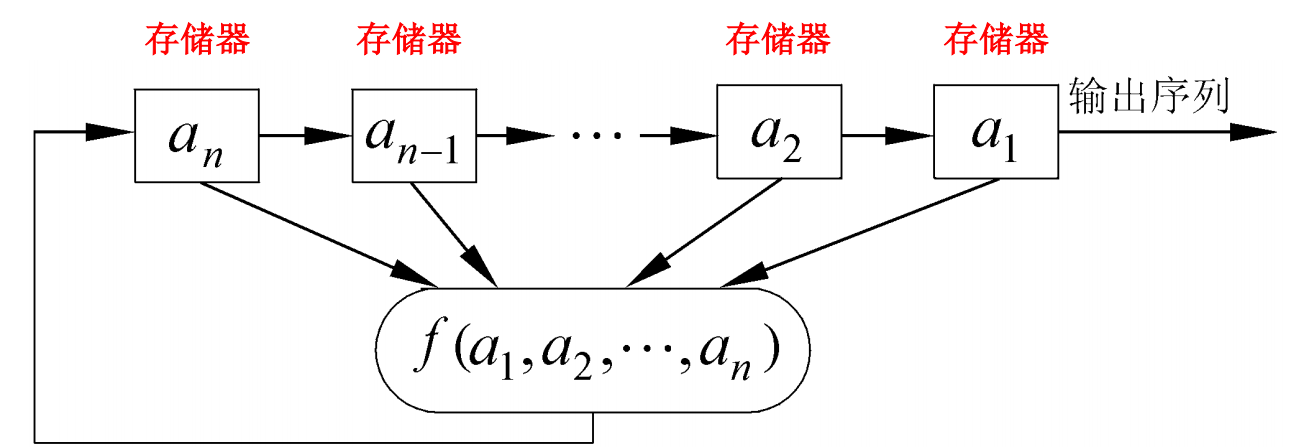

线性反馈移位寄存器(LFSR)是一种时序逻辑电路,由一系列串联的寄存器组成,寄存器中的数据通过反馈多项式进行移位和反馈。LFSR的结构如下图所示:

graph LR

subgraph LFSR

A[0] --> A[1]

A[1] --> A[2]

A[2] --> A[3]

A[3] --> A[4]

A[4] --> XOR

XOR --> A[0]

end

LFSR由以下部分组成:

- 寄存器阵列: 一组串联的寄存器,用于存储LFSR的状态。

- 反馈多项式: 一个二进制多项式,用于确定寄存器之间的反馈连接。

- XOR门: 一个异或门,用于将反馈多项式中的某些寄存器输出进行异或运算,并将其反馈到第一个寄存器。

2.2 LFSR的工作原理

LFSR的工作原理如下:

- 初始化: 将寄存器阵列中的所有寄存器初始化为特定值(通常为0或1)。

- 移位: 在每个时钟周期,寄存器阵列中的所有寄存器都向右移一位。

- 反馈: 根据反馈多项式,将寄存器阵列中某些寄存器输出进行异或运算,并将其反馈到第一个寄存器。

LFSR的输出序列是寄存器阵列中第一个寄存器的值。这个输出序列是一个伪随机序列,具有特定的统计特性,称为M序列。

2.3 M序列的特性

M序列具有以下特性:

- 最大长度: M序列的长度等于寄存器阵列的长度减1。

- 平衡性: M序列中0和1出现的次数相等。

- 伪随机性: M序列看起来是随机的,但实际上是由确定的反馈多项式生成的。

- 自相关性: M序列与自身的移位版本相关,除了零移位外,所有其他移位的相关性都为0。

- 周期性: M序列的周期等于其最大长度。

3. VERILOG语言描述时序逻辑

3.1 VERILOG语言概述

VERILOG语言是一种硬件描述语言(HDL),专门用于描述数字系统的设计和实现。它是一种基于文本的语言,具有以下特点:

- 层次化描述: VERILOG允许使用模块和实例来创建层次化的设计。

- 时序建模: VERILOG提供了对时序行为的建模支持,包括时钟、复位和数据流。

- 并发执行: VERILOG代码中的语句是并行执行的,这使得它非常适合描述数字电路的并行行为。

3.2 时序逻辑描述方法

时序逻辑是描述数字系统中随时间变化的行为的一种方法。在VERILOG中,时序逻辑可以使用以下方法描述:

- 连续赋值语句: 连续赋值语句用于描述组合逻辑,即输出值仅取决于当前输入值。

- 过程块: 过程块用于描述时序逻辑,即输出值不仅取决于当前输入值,还取决于以前的状态。

3.3 M序列时序逻辑设计

M序列是一种伪随机序列,具有许多有用的特性,例如良好的自相关和低交叉相关。在VERILOG中,可以使用过程块来设计M序列时序逻辑。

以下是一个使用VERILOG描述M序列时序逻辑的示例代码:

module m_sequence(

input clk,

input reset,

output reg [7:0] m_sequence

);

// 寄存器和反馈多项式

reg [7:0] shift_register;

parameter feedback_polynomial = 8'b11001001;

// 时钟和复位信号

always @(posedge clk or negedge reset) begin

if (reset) begin

shift_register <= 8'b0;

end else begin

// 移位寄存器

shift_register <= {shift_register[6:0], shift_register[7] ^ feedback_polynomial[0]};

// 输出M序列

m_sequence <= shift_register;

end

end

endmodule

代码逻辑分析:

- 时钟和复位信号:

always @(posedge clk or negedge reset)语句表示该过程块在时钟上升沿或复位信号下降沿触发。 - 复位: 如果

reset为真,则将shift_register复位为全0。 - 移位寄存器:

shift_register <= {shift_register[6:0], shift_register[7] ^ feedback_polynomial[0]}语句表示将shift_register向右移一位,并将最高位与反馈多项式的最低位进行异或运算。 - 输出M序列:

m_sequence <= shift_register语句表示将shift_register的值输出到m_sequence。

4. M序列VERILOG源代码设计

4.1 M序列VERILOG源代码结构

M序列VERILOG源代码主要由以下部分组成:

- 头文件包含:包含必要的VERILOG库和宏定义。

- 实体声明:定义模块的接口和端口。

- 寄存器和反馈多项式声明:声明M序列生成器中使用的寄存器和反馈多项式。

- 时钟和复位信号声明:声明时钟和复位信号。

- 时序逻辑实现:使用VERILOG的always块实现M序列生成逻辑。

- 测试模块:用于验证M序列生成器的功能。

4.2 寄存器和反馈多项式设计

M序列生成器的核心是移位寄存器和反馈多项式。寄存器用于存储M序列的当前状态,而反馈多项式用于确定寄存器中每个位的更新方式。

寄存器设计

寄存器使用VERILOG的reg数据类型声明,如下所示:

reg [n-1:0] register;

其中, n 是寄存器的位宽。

反馈多项式设计

反馈多项式使用VERILOG的parameter关键字声明,如下所示:

parameter feedback_polynomial = 32'h12345678;

其中, feedback_polynomial 是反馈多项式的值。

4.3 时钟和复位信号设计

时钟和复位信号是M序列生成器正常工作所必需的。时钟用于驱动寄存器的更新,而复位信号用于将寄存器重置为初始状态。

时钟设计

时钟使用VERILOG的input关键字声明,如下所示:

input clock;

复位信号设计

复位信号使用VERILOG的input关键字声明,如下所示:

input reset;

4.4 M序列生成模块测试

为了验证M序列生成器的功能,可以使用VERILOG的testbench进行测试。testbench是一个单独的模块,用于生成测试激励并检查输出结果。

测试激励生成

测试激励通常使用VERILOG的initial块生成,如下所示:

initial begin

// 时钟和复位信号激励

clock = 0;

reset = 1;

#10;

reset = 0;

end

输出结果检查

输出结果检查可以使用VERILOG的assert语句进行,如下所示:

assert (output_sequence == expected_sequence);

其中, output_sequence 是M序列生成器的输出序列, expected_sequence 是预期的输出序列。

5. VERILOG工程文件配置

5.1 工程文件概述

VERILOG工程文件是用来管理和配置VERILOG设计项目的,它包含了项目中所有相关文件的信息,如源文件、仿真配置、综合配置等。一个完整的VERILOG工程文件通常包括以下部分:

- 工程名称: 工程的名称,用于标识该工程。

- 源文件: 包含设计代码的VERILOG源文件。

- 仿真配置: 用于配置仿真器的仿真参数,如仿真时间、仿真模式等。

- 综合配置: 用于配置综合器的综合参数,如综合目标、优化级别等。

- 约束文件: 用于指定设计中的时序约束,如时钟频率、建立时间等。

- 测试文件: 用于验证设计功能的测试文件。

5.2 源文件配置

源文件配置主要用于指定工程中包含的VERILOG源文件。源文件可以是单个文件,也可以是多个文件。在工程文件中,源文件可以通过以下方式配置:

source <file_name>;

其中, <file_name> 为源文件的文件名。例如:

source "m_sequence.v";

source "register.v";

source "clock.v";

5.3 仿真配置

仿真配置用于配置仿真器的仿真参数。常用的仿真配置参数包括:

- 仿真时间: 指定仿真运行的时间,单位为秒。

- 仿真模式: 指定仿真模式,如功能仿真、时序仿真等。

- 仿真库: 指定仿真时使用的库文件。

- 仿真参数: 指定其他仿真参数,如仿真精度、仿真日志等。

在工程文件中,仿真配置可以通过以下方式配置:

simulator <simulator_name> {

<config_parameter> = <config_value>;

...

}

其中, <simulator_name> 为仿真器的名称, <config_parameter> 为仿真配置参数, <config_value> 为仿真配置参数的值。例如:

simulator icarus {

timescale = 1ns/1ps;

simulation_time = 100us;

simulation_mode = functional;

}

5.4 综合配置

综合配置用于配置综合器的综合参数。常用的综合配置参数包括:

- 综合目标: 指定综合的目标,如面积优化、速度优化等。

- 优化级别: 指定综合的优化级别,如无优化、低优化、高优化等。

- 约束文件: 指定时序约束文件。

- 综合参数: 指定其他综合参数,如综合算法、综合库等。

在工程文件中,综合配置可以通过以下方式配置:

synthesizer <synthesizer_name> {

<config_parameter> = <config_value>;

...

}

其中, <synthesizer_name> 为综合器的名称, <config_parameter> 为综合配置参数, <config_value> 为综合配置参数的值。例如:

synthesizer synopsys {

target = area;

optimization_level = high;

constraint_file = "timing.sdc";

}

6. M序列测试程序验证

6.1 测试程序设计

为了验证M序列生成模块的正确性,需要编写一个测试程序。测试程序的主要目的是生成一个已知序列,然后将其与M序列生成模块产生的序列进行比较。

module m_sequence_test;

// 定义测试参数

parameter N = 10; // 序列长度

parameter P = 3; // 反馈多项式阶数

parameter poly = 3'b110; // 反馈多项式

// 声明信号

reg clk;

reg rst;

wire [N-1:0] m_sequence;

// 实例化M序列生成模块

m_sequence_generator #(

.N(N),

.P(P),

.poly(poly)

) m_sequence_generator_inst (

.clk(clk),

.rst(rst),

.m_sequence(m_sequence)

);

// 测试程序

initial begin

// 初始化

clk = 0;

rst = 1;

#10;

rst = 0;

// 生成已知序列

reg [N-1:0] expected_sequence;

for (integer i = 0; i < N; i++) begin

expected_sequence[i] = (i == 0) ? 1 : expected_sequence[i-1] ^ (expected_sequence[i-P] & poly[P-1]);

end

// 比较序列

for (integer i = 0; i < N; i++) begin

if (m_sequence[i] != expected_sequence[i]) begin

$display("Error: Sequence mismatch at index %d", i);

$finish;

end

end

// 测试通过

$display("Test passed");

$finish;

end

endmodule

6.2 测试结果分析

运行测试程序后,如果控制台输出“Test passed”,则表示M序列生成模块通过了测试。

6.3 M序列验证

通过测试程序验证M序列生成模块的正确性后,就可以将其用于实际应用中。M序列具有广泛的应用,包括:

- 通信系统中的扩频通信

- 伪随机数生成

- 密码学

- 序列分析

简介:M序列,又称LFSR序列,广泛应用于数字通信、密码学等领域。本压缩包提供完整的m序列VERILOG源代码、工程文件和测试程序,旨在帮助开发者理解LFSR的工作原理并进行硬件验证。源代码使用VERILOG语言编写,定义了一个基于线性反馈函数的LFSR结构,通过时序逻辑实现序列的生成。工程文件包含编译脚本、仿真模型和约束文件,方便在不同环境中复现和测试设计。测试程序验证了生成的序列是否满足M序列的特性,如正确的周期和零自相关性。

3735

3735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?