名称:m序列发生器VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

m序列发生器

1、采用VHDL语言设计m序列发生器

2、本代码也包含Verilog语言的m序列发生器

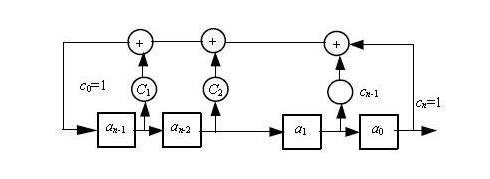

1. 原理框图

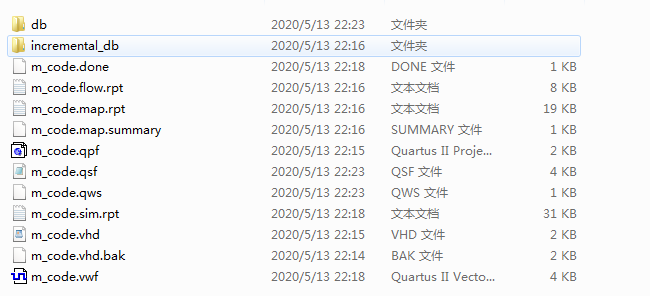

2. 工程文件

3. 程序文件

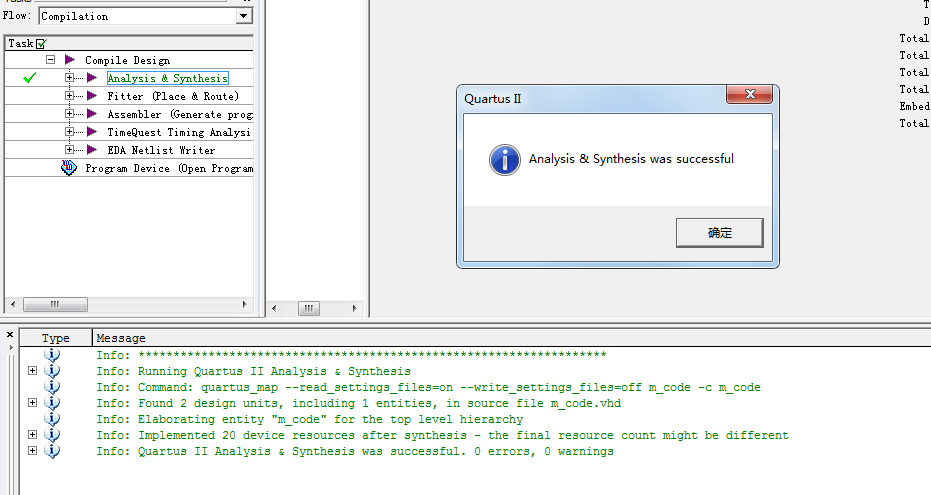

4. 程序编译

5. RTL图

6. 仿真文件

7. 仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY m_code IS PORT ( clk : IN STD_LOGIC;--时钟 rst : IN STD_LOGIC;--复位 ctrl_1 : IN STD_LOGIC;--控制端1 ctrl_2 : IN STD_LOGIC;--控制端2 dout : OUT STD_LOGIC--输出随机序列(m序列) ); END m_code; ARCHITECTURE trans OF m_code IS SIGNAL ctrl : STD_LOGIC_VECTOR(1 DOWNTO 0); SIGNAL ddout_set : STD_LOGIC_VECTOR(7 DOWNTO 0) := "10001001"; SIGNAL ddout : STD_LOGIC_VECTOR(7 DOWNTO 0) := "10001001"; BEGIN ctrl <= (ctrl_1 & ctrl_2);--2位控制端拼接为2bit PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN CASE ctrl IS WHEN "00" => ddout_set <= "10001001";--初值1 WHEN "01" => ddout_set <= "00011001";--初值2 WHEN "10" => ddout_set <= "00100111";--初值3 WHEN "11" => ddout_set <= "01000101";--初值4 WHEN OTHERS => END CASE; END IF; END PROCESS; PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN IF (rst = '1') THEN ddout <= ddout_set;--复位,获取初始值 ELSE

源代码

扫描文章末尾的公众号二维码

本文详细介绍了使用VHDL设计的m序列发生器,包括原理框图、工程和程序文件,以及在Quartus中的编译和仿真过程。代码展示了如何通过控制端生成不同初值的随机序列。

本文详细介绍了使用VHDL设计的m序列发生器,包括原理框图、工程和程序文件,以及在Quartus中的编译和仿真过程。代码展示了如何通过控制端生成不同初值的随机序列。

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?