基础概念

IIC是一种串行通信总线,也称为I2C(Inter-Integrated Circuit)总线。IIC支持多主多从,当总线上有多个主机同时启用总线时,IIC具备冲突检测和仲裁的功能来防止错误产生。每个连接到IIC总线上的器件都有唯一的地址(7bit),并且每个器件都可以作为主机和从机。

协议原理

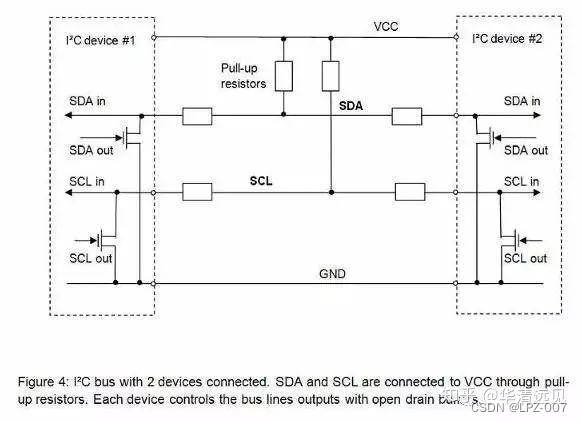

拓扑示例

IIC支持多主多从,通过SDA(serial data)、SCL(serial clk)双线来进行通信。典型结构如下:

协议规定:

- 每个IIC设备有唯一的7位设备地址,因而理论最多可支持2^7=128个设备,从机最多127,主机不限;

- 数据部分8比特,以及启动,停止,确认,读写控部分。

速率模式

- 标准模式(Standard):速率为100kbps,适用于低速或对数据可靠性要求较高的场景,如EEPROM存储器等。

- 快速模式(Fast):速率为400kbps,适用于需要较高数据传输速率且对数据可靠性要求适中的场景,如音频处理等。

- 快速模式+(Fast-Plus):速率为1Mbps,适用于需要高速数据传输的场景,如实时图像传输等。

- 高速模式(High-speed):速率为3.4Mbps,适用于需要非常高速数据传输的场景,如实时音频处理等。

- 超快模式(Ultra-Fast):速率为5Mbps(单向传输),适用于需要非常高速且数据传输量较大的场景,如实时视频处理等。

其中,标准模式及快速模式是应用最广的。

数据读写

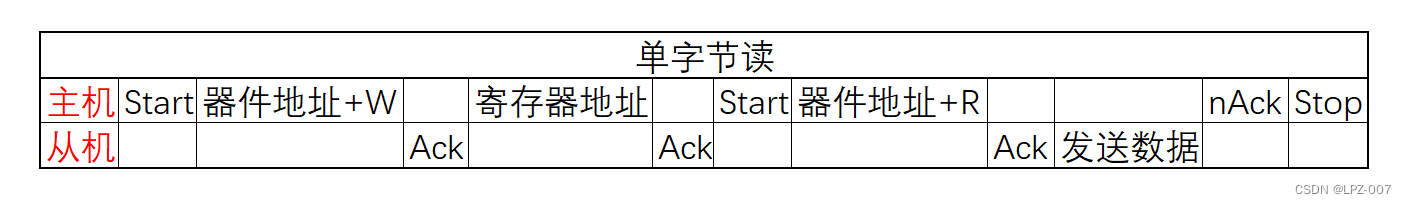

读时序

读时序的过程如下:

- 主机发送启动位、目标从机地址及写信号

- 从机回复ACK

- 主机发送寄存器地址

- 从机回复ACK

- 机发送启动位、目标从机地址及读信号

- 从机回复ACK

- 从机发送对应数据

- 主机不响应

- 主机发送停止位

写时序

写时序的过程如下:

- 主机发送启动位、目标从机地址及写信号

- 从机回复ACK

- 主机一次发送写的寄存器地

- 从机回复ACK

- 主机发送对应数据

- 从机回复ACK

- 第5步和第6步可以重复多次,即顺序写多个寄存器

- 主机发送停止位

说明:可能连续写

硬件结构

PIN口的输入输出转换通过开漏实现,fpga可使用inout口,三态门来控制。

参考链接

https://blog.csdn.net/helloworld573/article/details/105629235

https://blog.csdn.net/qq_30624591/article/details/85255871

https://zhuanlan.zhihu.com/p/161710767

https://zhuanlan.zhihu.com/p/678229227

1739

1739

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?