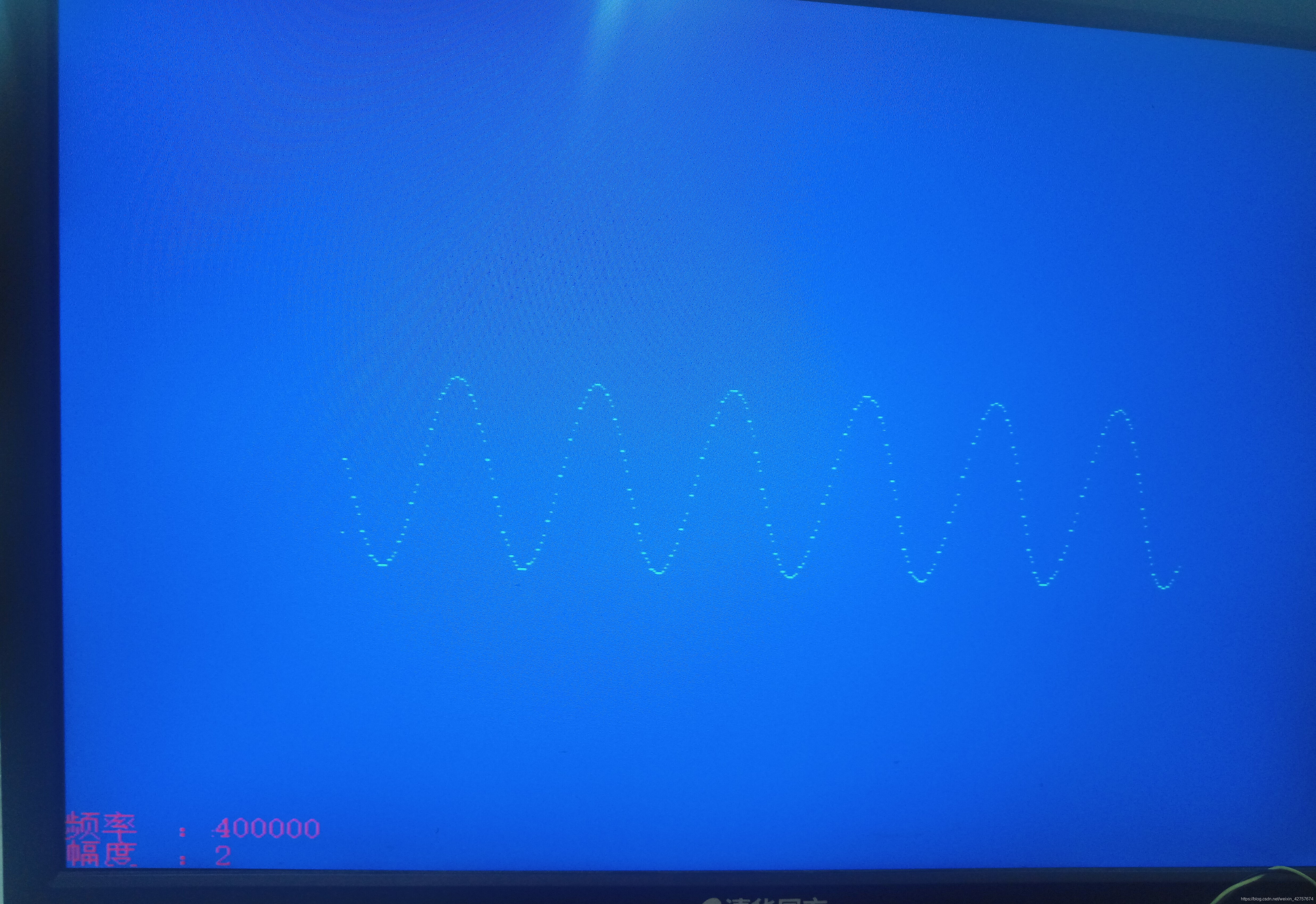

我使用的是VGA显示,VGA显示屏有自适应,在像素允许范围内,都会显示在整个屏幕。当分辨率很低时,显示的像素点就很离散,VGA需要的时钟频率较低。

我就采用的640480的分辨率,我尝试过采用更高分辨率,但是时序不能约束,只好放弃。如果有性能比较好的FPGA可以采用更好分辨率。

我就采用的640480的分辨率,我尝试过采用更高分辨率,但是时序不能约束,只好放弃。如果有性能比较好的FPGA可以采用更好分辨率。

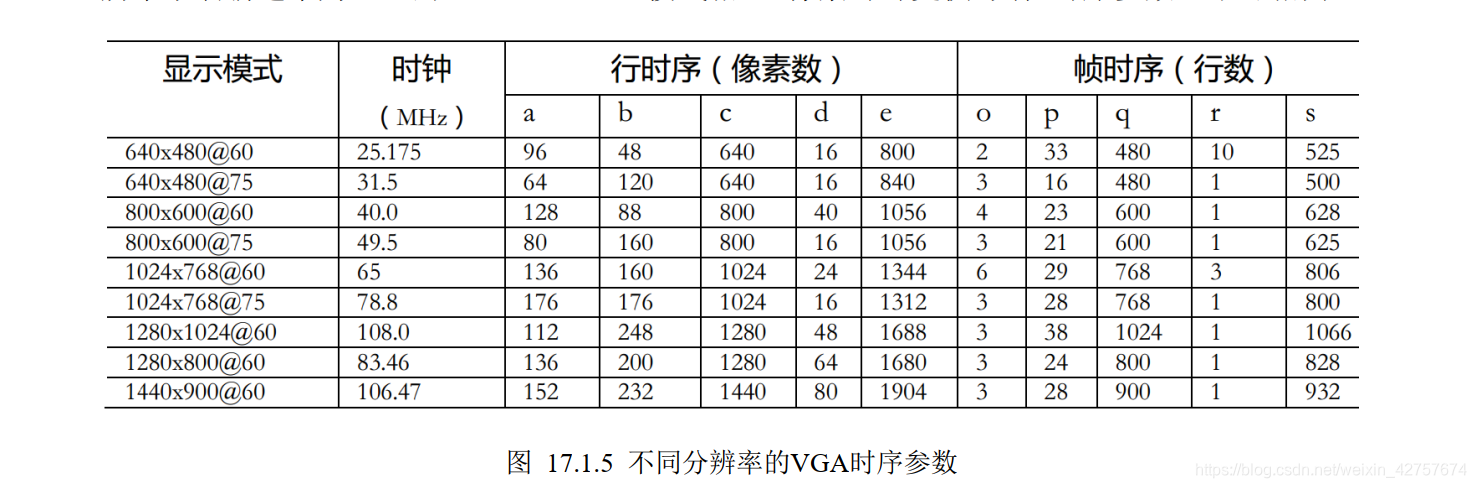

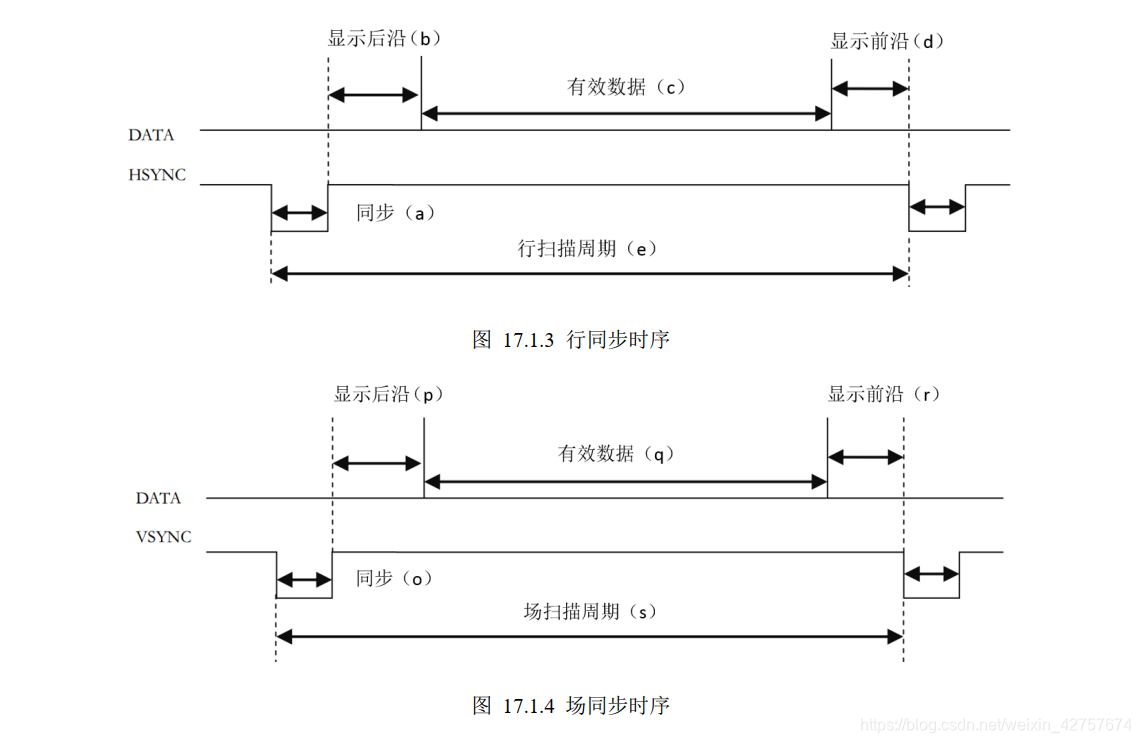

下面是VGA时序 a,b,c,d,e和o,p,q,r,s就是上图时序参数对应的值。只不过,需要注意的是,行同步时序的单位是一个时钟周期,而场同步时序的单位是一个行周期,简单理解就是一行对应一列中的一个坐标。其中时钟不一定等于标准值,例如25.175MHZ,采用PLL IP核不能产生25.175MHZ的时钟,那么我就使用最接近的25MHZ。106.47MHZ,使用105MHZ。

a,b,c,d,e和o,p,q,r,s就是上图时序参数对应的值。只不过,需要注意的是,行同步时序的单位是一个时钟周期,而场同步时序的单位是一个行周期,简单理解就是一行对应一列中的一个坐标。其中时钟不一定等于标准值,例如25.175MHZ,采用PLL IP核不能产生25.175MHZ的时钟,那么我就使用最接近的25MHZ。106.47MHZ,使用105MHZ。

我这里有一个自己写的VGA测试程序,采用的1440900,完全没有问题,和640*480比起来,普清和蓝光的区别。

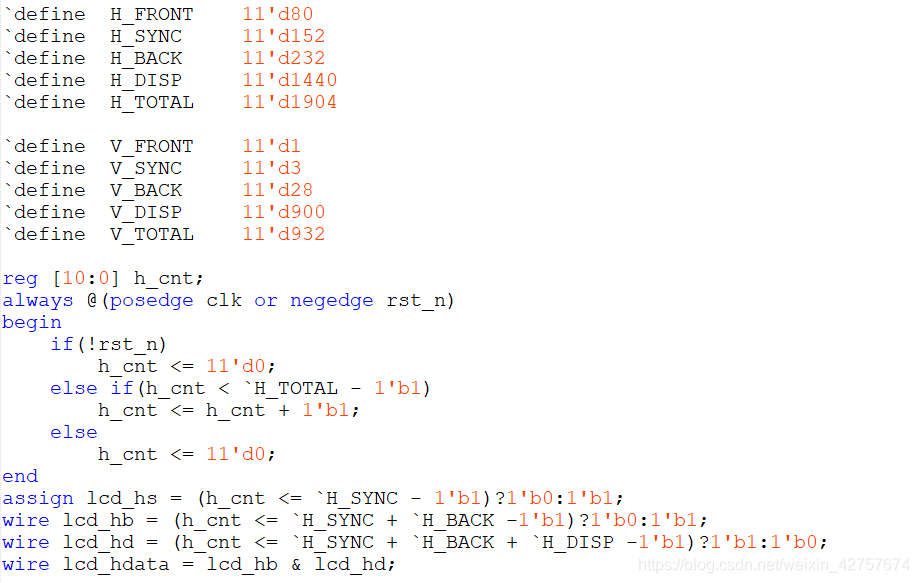

行同步代码

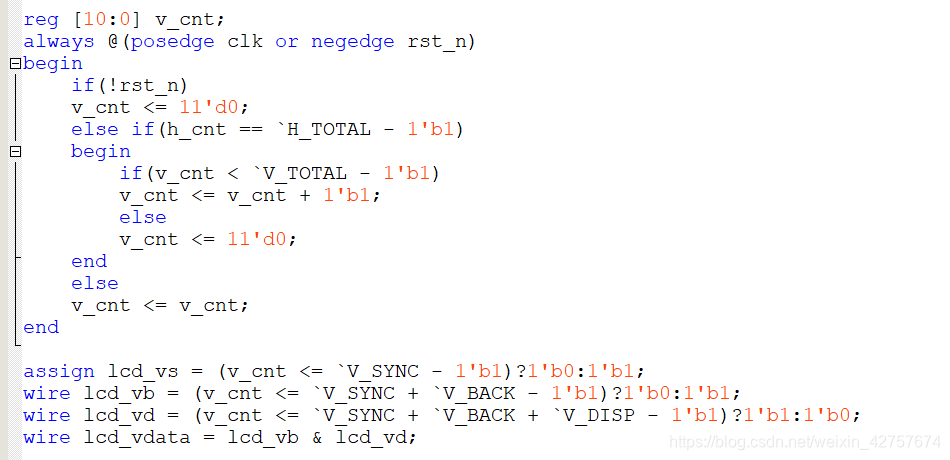

场同步代码

上传了一份,但是下载要积分。所以,有需要的找我,免费。企鹅号:1757334763

基于FPGA数字示波器显示部分

最新推荐文章于 2023-10-07 20:29:52 发布

本文介绍了使用FPGA实现640x480分辨率的VGA显示,探讨了高分辨率时序约束问题以及如何选择接近标准的时钟频率。作者还分享了一个能成功运行1440x900分辨率的VGA测试程序,并提供了帮助获取代码的方式。

本文介绍了使用FPGA实现640x480分辨率的VGA显示,探讨了高分辨率时序约束问题以及如何选择接近标准的时钟频率。作者还分享了一个能成功运行1440x900分辨率的VGA测试程序,并提供了帮助获取代码的方式。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2885

2885

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?