$countones这个函数跟约束搭配使用,或者用于assertion中都不错,

这个函数是计算一组bus信号里面1的个数

约束sig_A只能随机一bit 1出来

std::randomize(sig_A) with {$countones(sig_A)==1;};

检测sig_A是one hot信号,

assert($countones(sig_A)==1);

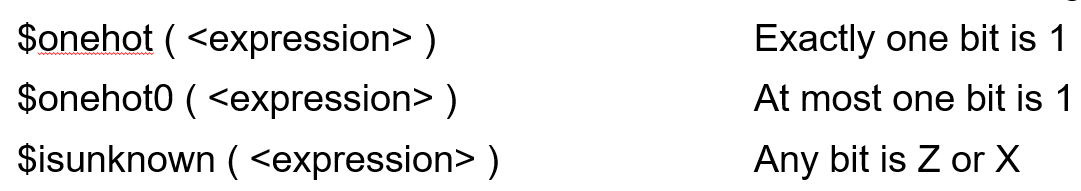

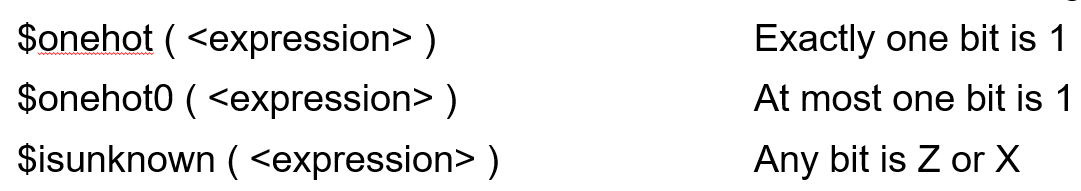

另外sva还有一个专门的函数$onehot(sig_A);

$countones这个函数跟约束搭配使用,或者用于assertion中都不错,

这个函数是计算一组bus信号里面1的个数

约束sig_A只能随机一bit 1出来

std::randomize(sig_A) with {$countones(sig_A)==1;};

检测sig_A是one hot信号,

assert($countones(sig_A)==1);

另外sva还有一个专门的函数$onehot(sig_A);

1468

1468

770

770

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?