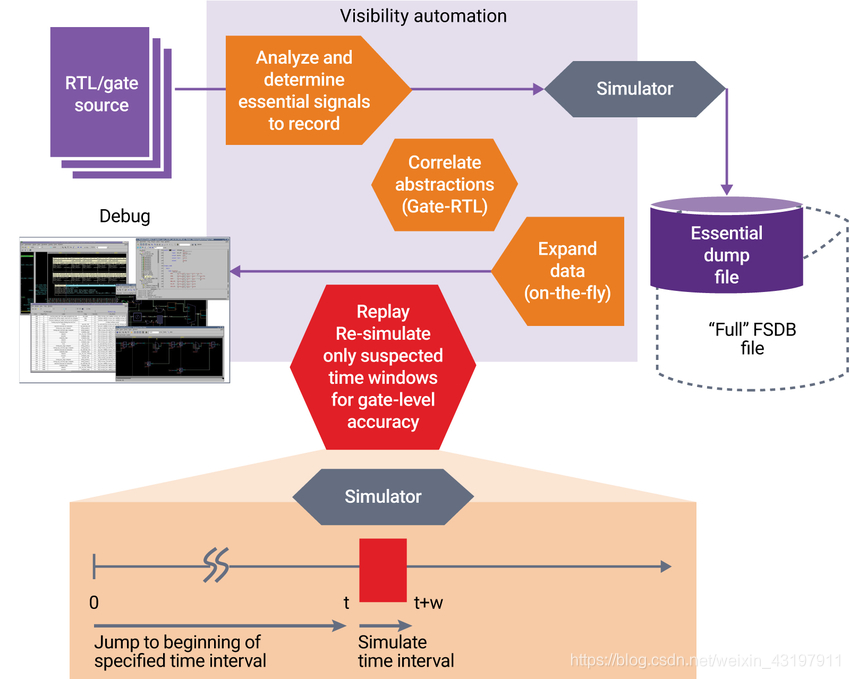

The Siloti™ Visibility Automation System transforms your verification methodology by eliminating the overhead associated with recording data for all the signals in a design. Unique automation technology in the Siloti system provides full visibility of internal signals for complex IC and SoC designs by:

- Identifying the minimal set of signals that must be recorded

- Generating “on-demand” the rest of the signal data Correlating

- gate-level results to the RTL source code

VCS uses VCS compiler scripts to compile the Knowledge Database (KDB) for Verdi. When you specify the -kdb option, VCS creates the Verdi KDB and dumps the design into the libraries specified in the synopsys_sim.setup file.

You can generate the Verdi KDB using the VCS -kdb option either in the VCS two-step flow or three-step flow.

To determine which databases are to be generated, specify one of the following arguments with the -kdb option:

-kdb=only

Generates only the Verdi KDB that is needed for both post-process and interactive simulation debug with Verdi.

In VCS two-step flow, this option does not generate the VCS compile data/executable, and does not disturb the existing VCS compile data/executables.

For example,

% vcs -kdb=only <compile_options> <source files> -lca

In VCS three-step flow, this option dumps the minimum data required at analysis stage, and does not disturb the existing VCS compile data/executables.

% vlogan –kdb=only <vlogan_options> <source files>

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?