文章目录

自动布局布线(Animate Preview)

1. 面积估算结果

标准单元库

1. 标准单元库导入

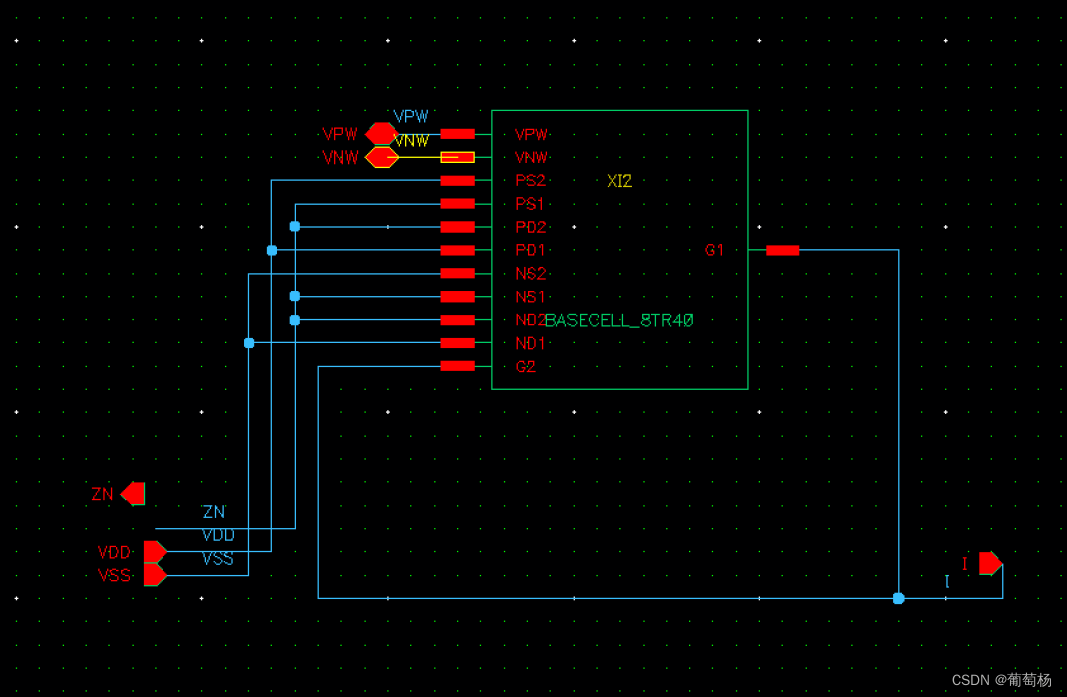

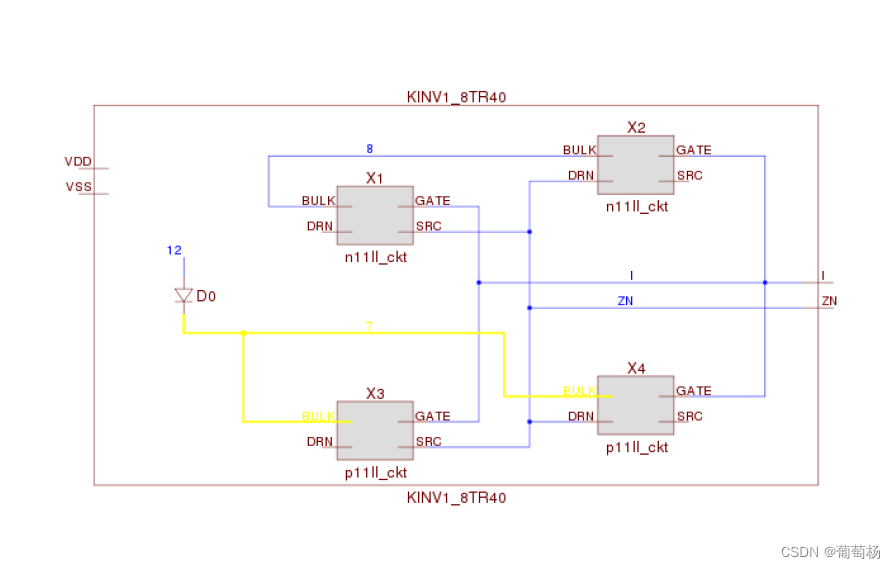

- gds和cdl文件导入之后,原理图的输入与输出的端口方向相反,输入电口I变为输出,输出端口ZN变为输入。(需要手动修改?)

- 由于PMOS的Body 在原理图中label为VNW,NMOS的Body在原理图中的Label为VPW,理论上原理图仿真时VNW需要连接VDD,VPW需要连接VSS。但在逻辑门的原理图中没有VNW和VPW的pin,手动加入pin之后,由于版图中没有VNW和VPW的pin所以会导致LVS失败。怎么处理这个问题?( 直接忽略VPW和VNW浮空的问题)

- 导入symbol:在virtuoso的cds.lib中Import->Verilog ,导入symbol时,VDD变为VDD!,VSS变为VSS!。(此处手动画symbol?)

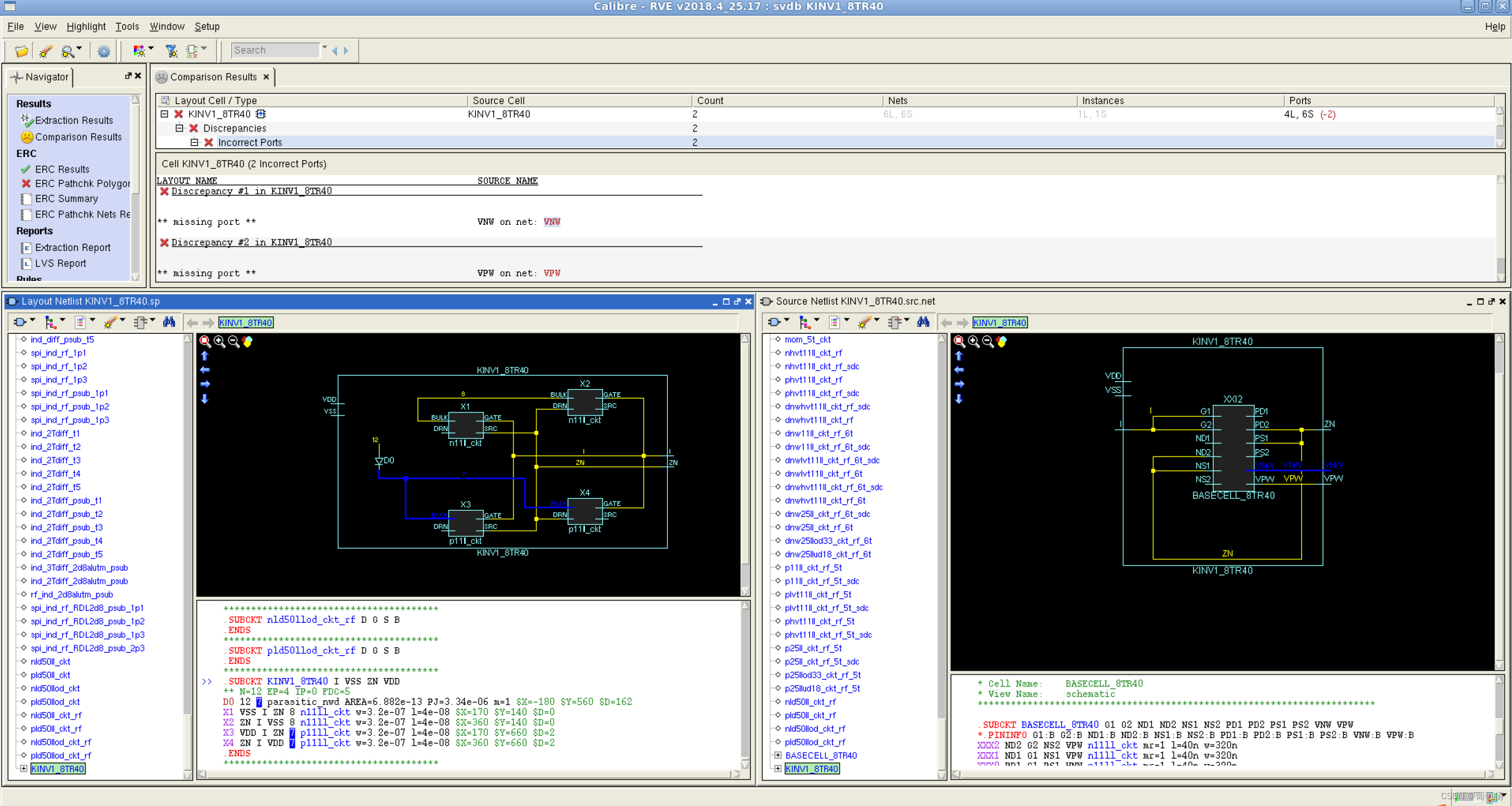

2. 标准单元库LVS

- LVS结果

- 原理图

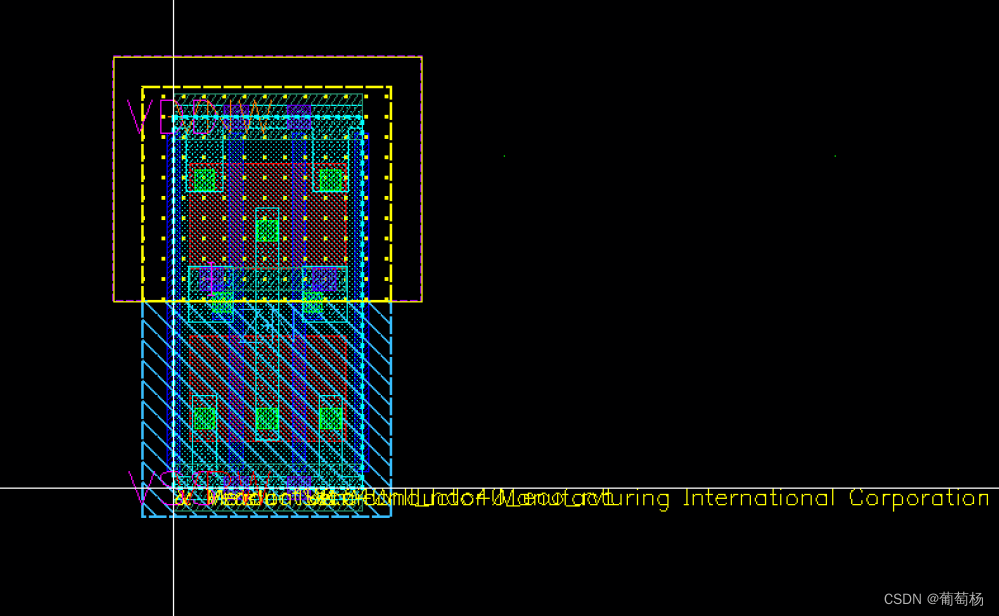

- gds导入的版图

- gds 版图提取的结果,并没有VNW和VPW

版图规则

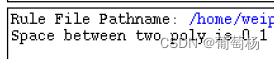

1. 多晶硅之间间距大于0.1

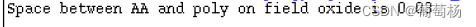

2. AA和Poly之间间距为0.03

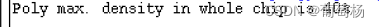

3. 密度问题

4. 通孔

5. 其他问题

-

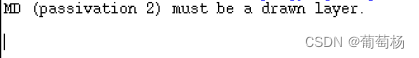

MD?

-

NW

2.1 NW之间相距0.6

2.2 NW最小宽度0.33

-

GT

-

AA

-

M1 最小包围0.2

-

NW

-

CT

版图软件使用

1. ctrl + F和shift + F可以切换不同的显示。

2. t 之后点击一处可以查看显示层次

LVS问题

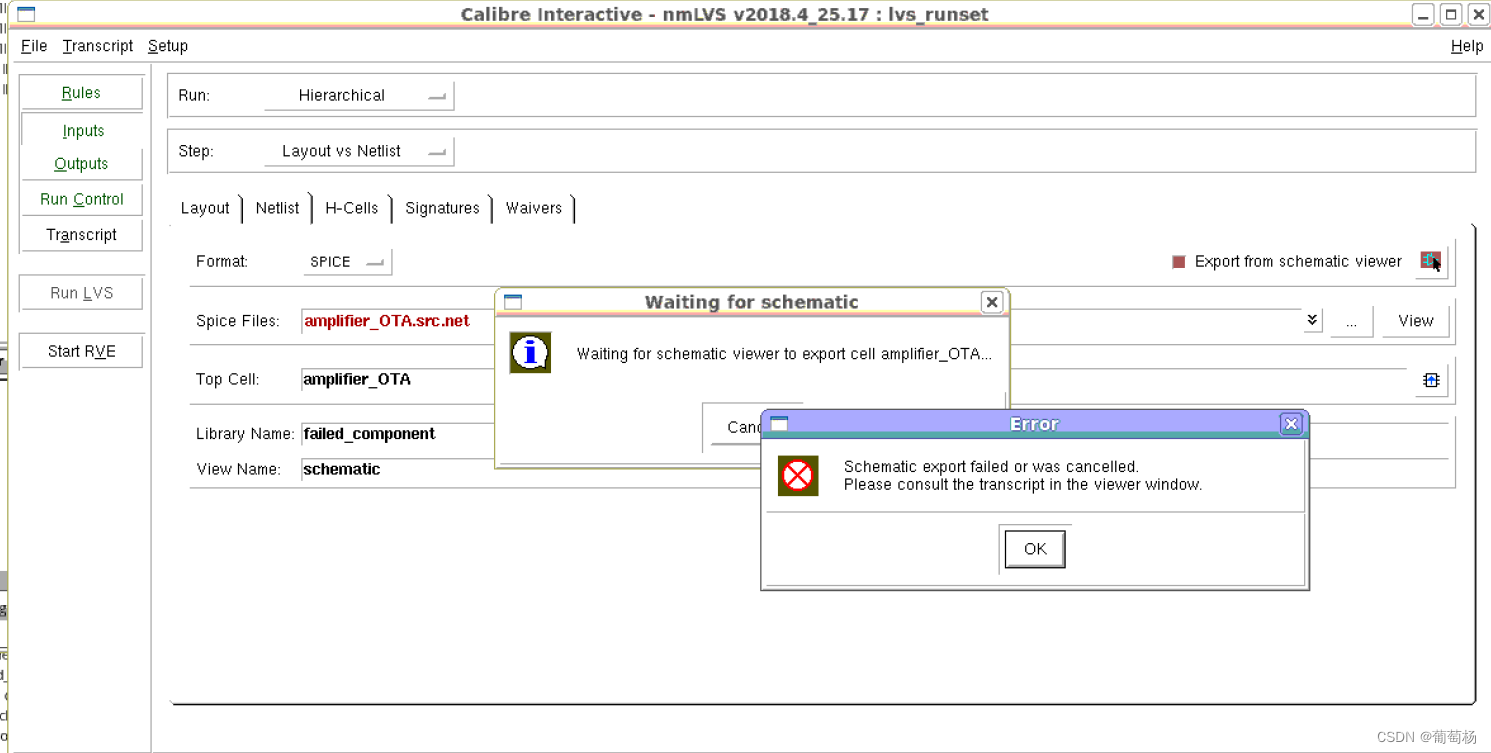

1. 原理图导出错误与解决

-

shematic export failed

-

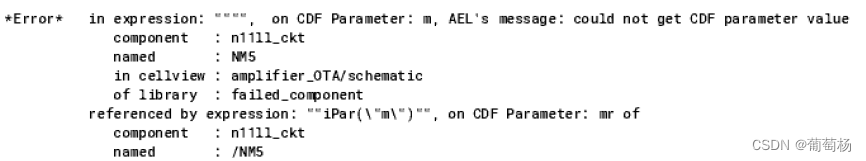

关闭virtuoso,删除 .cdslck文件;export CDS_Netlisting_Mode = Analog

-

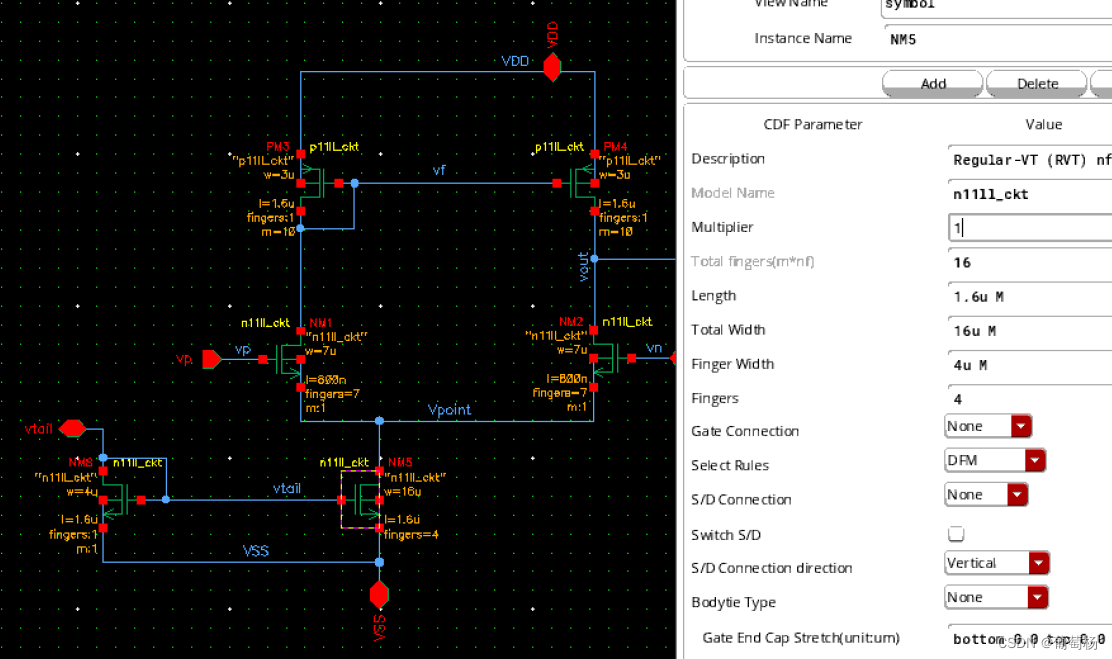

后来观察CDS.log,报错是因为尾电流管没有写m=1

748

748

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?