一。做LVS的过程中,一些关键的注意事项:

LVS规则文件中的层次设置,区分大小写

版图的Merge,打Label

H-Cell文件的正确性

LVS网表的修改、Include子网表(std cell的、IO的、macro的...)、声明电源地端口

特别注意的一点,在LVS(-Herarchical mode下) 时, 软件提取版图也会自己生成一个.sp网表,v2lvs生成的.sp文件的名字一定不能和它冲突,否则从版图提取的.sp文件会替换v2lvs生成的网表,这样就变成了版图和自己提取出来的网表进行LVS,这样的结果肯定是通过的,但是没有任何意义

二。Tapless工艺如何做LVS

Q:Tapless的工艺VNW VPW在网表中要怎么处理?

在Tapcell工艺中要用ICC插入Tap cell用于形成衬底接触和阱接触。std cell的cdl里定义有VDD VSS VNW VPW等电源,但是ICC输出的网表不带VNW VPW,不对网表进行处理直接跑LVS的话会有VNW VPW VDD VSS的错误。

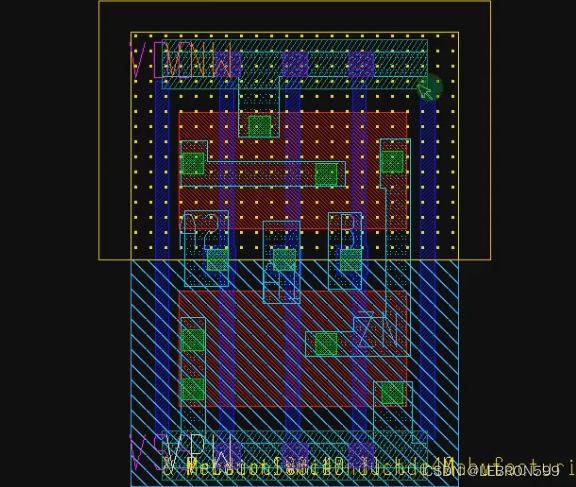

如下图是Tapless工艺的,没有单独做N阱和衬底的接触,而是作为一个Cell来提供阱和衬底的接触。在比较老的“.18”工艺以及更老的工艺中,会单独给每个std cell做N阱和衬底的接触,比如会对每个N阱做N注入然后连接到VDD上,然后对P衬底做P注入,并连接到VSS上面。但是这样的Tap工艺的缺点是:非常占面积。对一个Design来说,里面的std cell很多,若每个std cell都是Tap工艺,那么整个Design的面积将会非常非常大。最新的“,18”工艺中,就不会对每个std cell做N阱和衬底的接触,而是将N注入和衬底接触给拎出来,单独作为一个Cell来放置,每隔一段区域放置一个,这样只要保证在规定的范围内至少有一个Tapcell就可以,若超过了范围(距离)的要求,就会产生闩锁效应。用棋盘式的摆放放在std cell中,就会节省很多的面积,这就是引入Tapless工艺的原因。

在上图中还会看到VNW和VPW,这是给N阱和P衬底打的Label,在最后的Layout里面我们会看到VNW会接到VDD上,VPW会接到VSS上(VNW和VPW都是通过Tapcell分别接上VDD和VSS的)。这样在Layout中就连接到一起了。

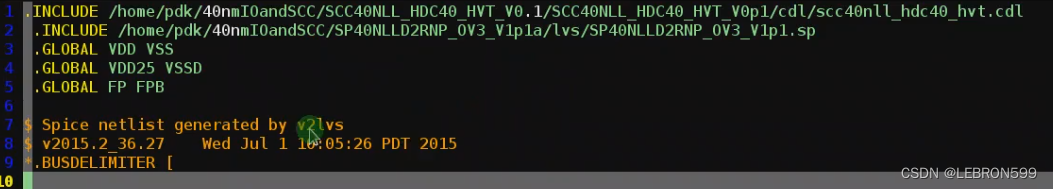

但是在netlist里面,在我们使用v2lvs后,VNW和VDD,VPW和VSS是没有连接到一起的。

如图所示:

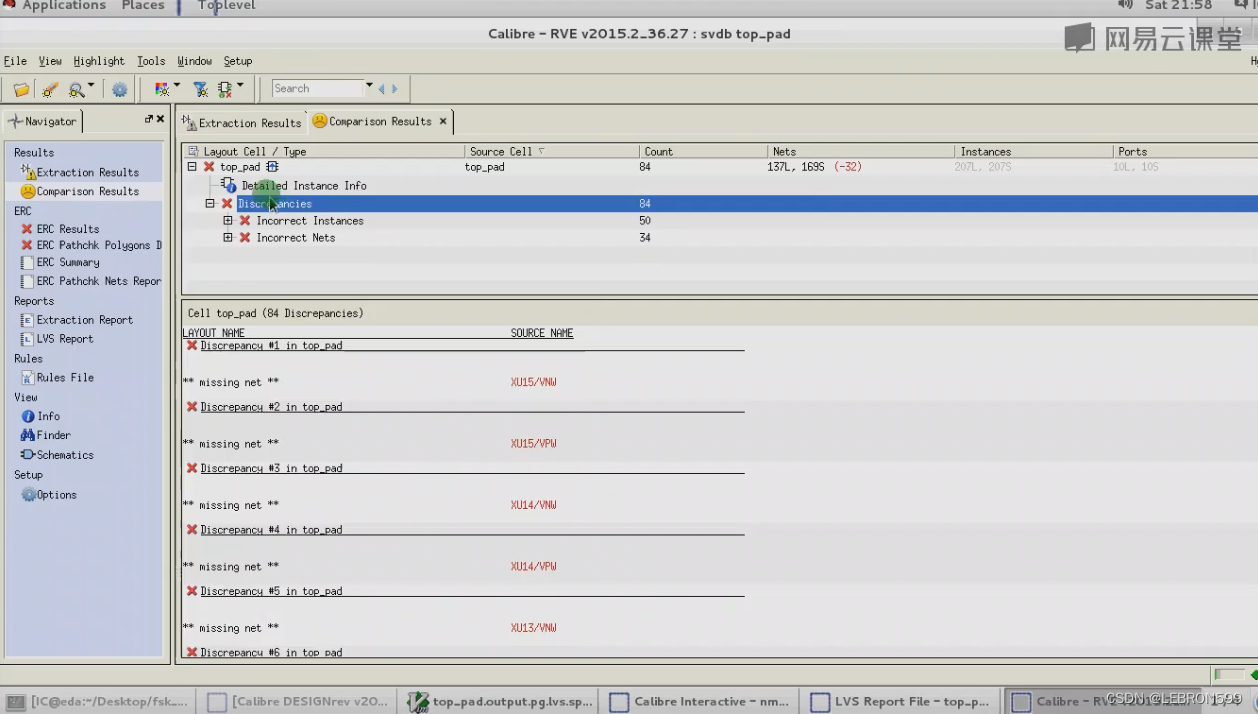

然后我们以此来跑LVS,可以看到LVS是不通过的,并且看到了是VNW和VPW的问题。

那么Tapless工艺下,在layout中我们把VNW和VDD,VPW和VSS连接到了一起。在netlist中却没有连接到一起,我们该怎么做呢?

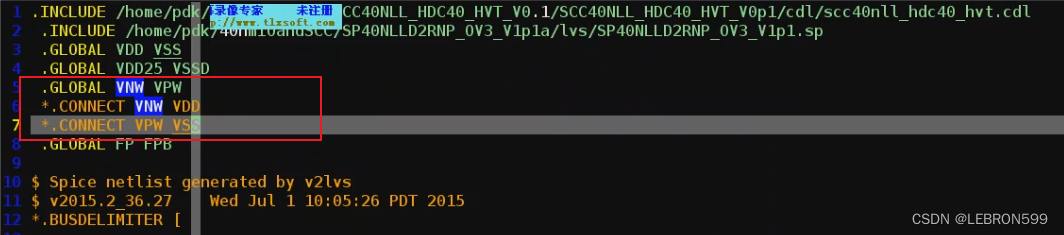

如图所示,使用.GLOBAL声明VNW和VPW,然后使用*.CONNECT进行连接。

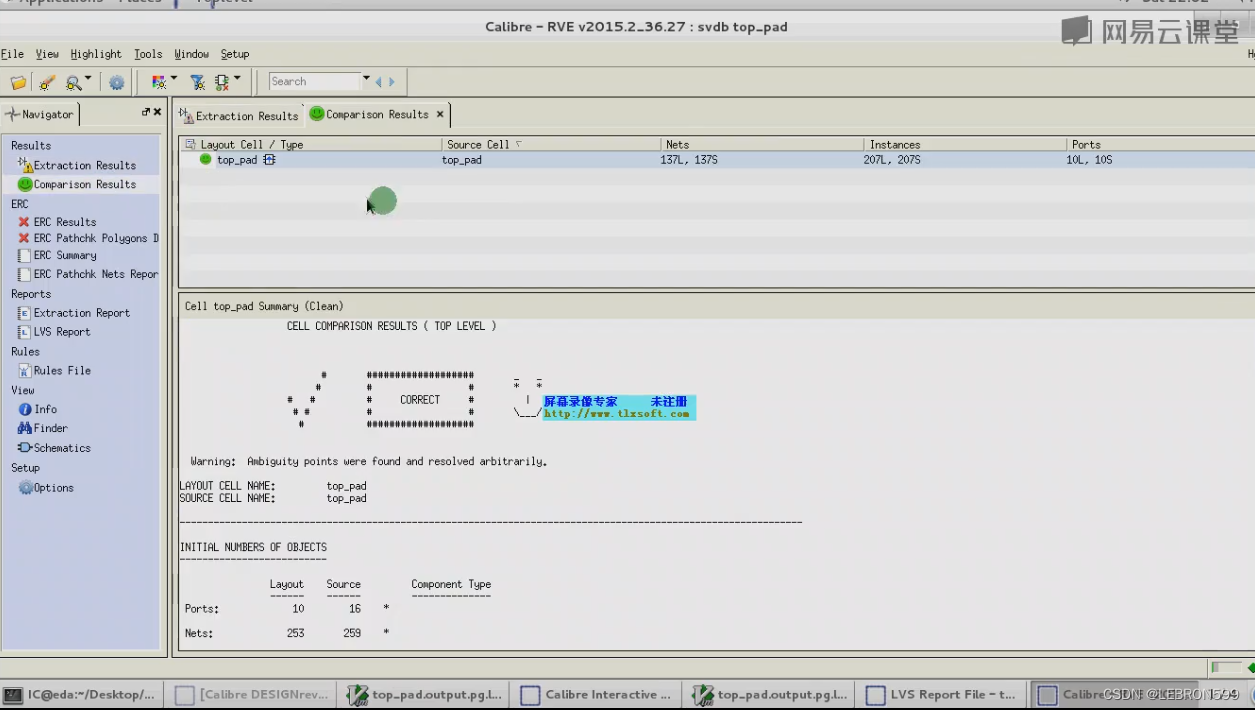

然后跑LVS,可见LVS通过:

总结:我们打开一个版图,看看里面有没有单独的N阱或衬底的接触,我们就知道是Tapless的工艺还是普通的工艺。然后就知道了该怎样对网表进行操作。

974

974

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?