文章目录

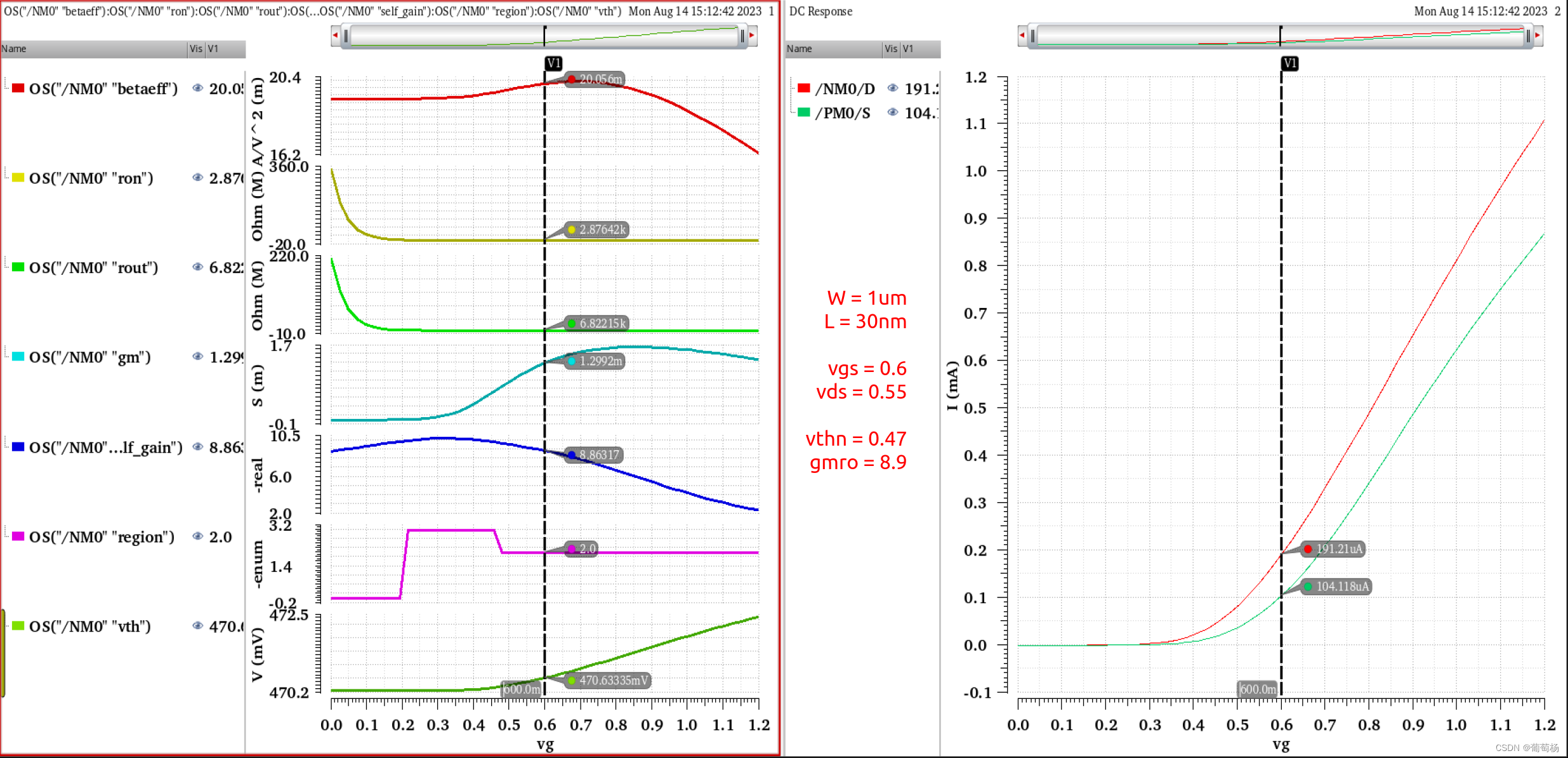

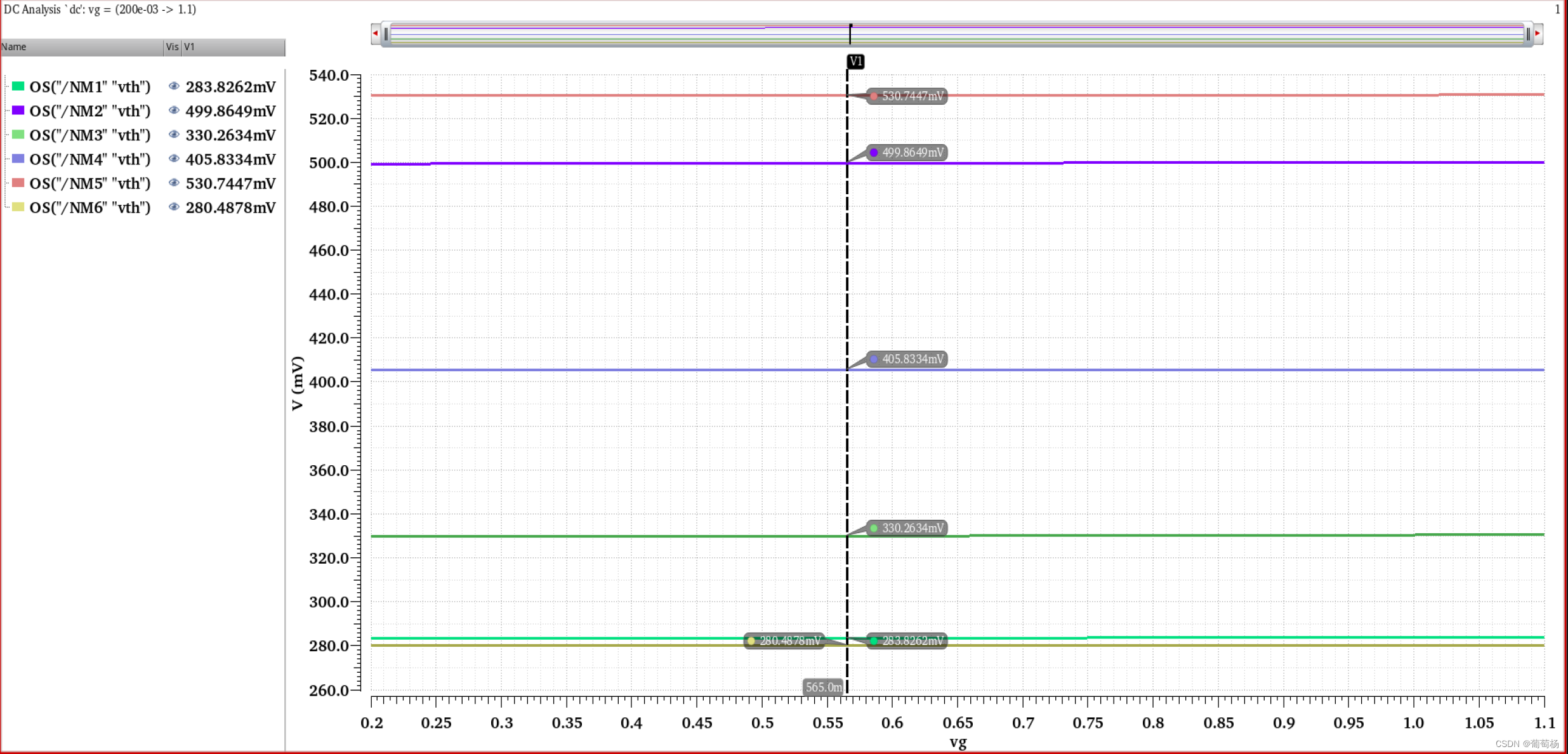

1. MOS管特性

结论:

-

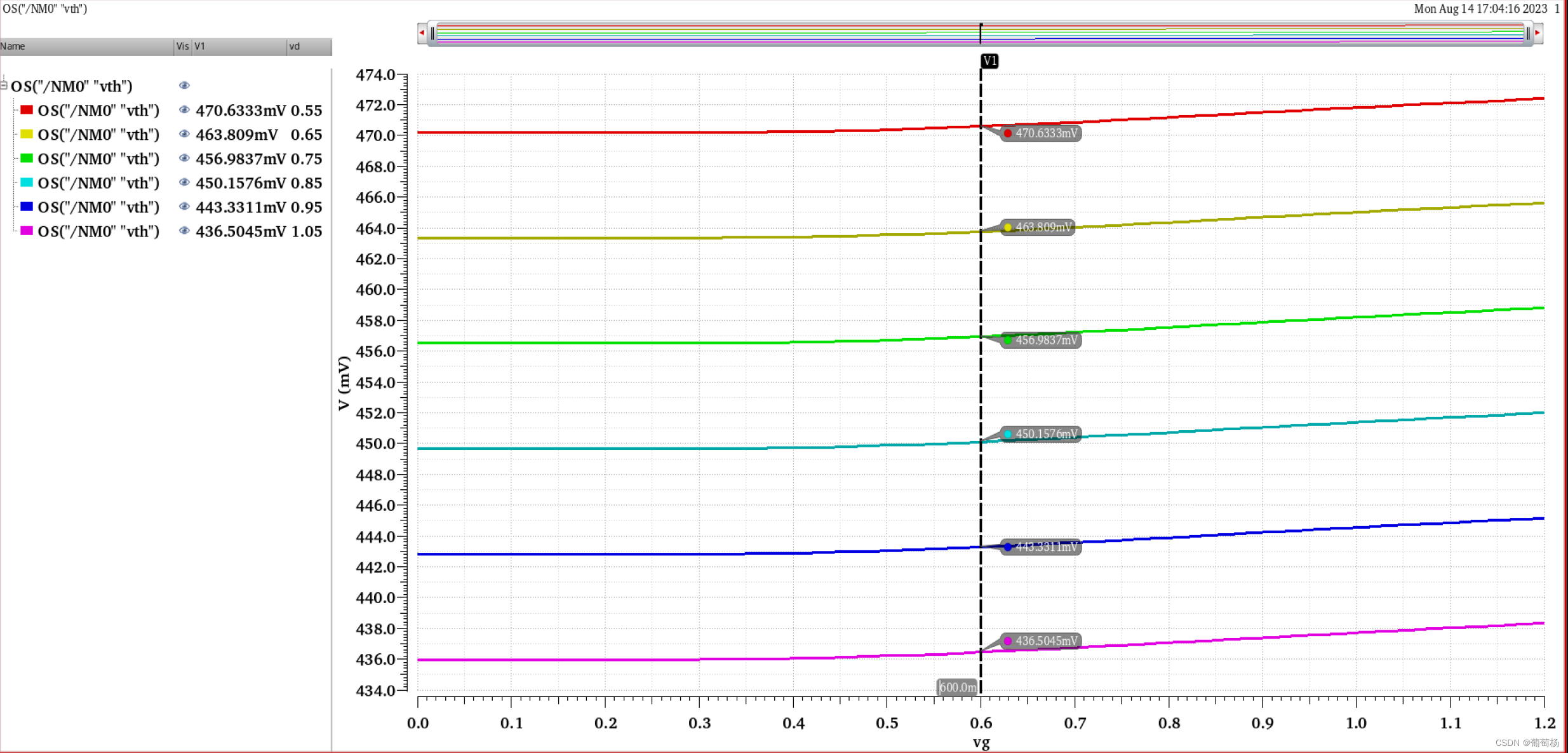

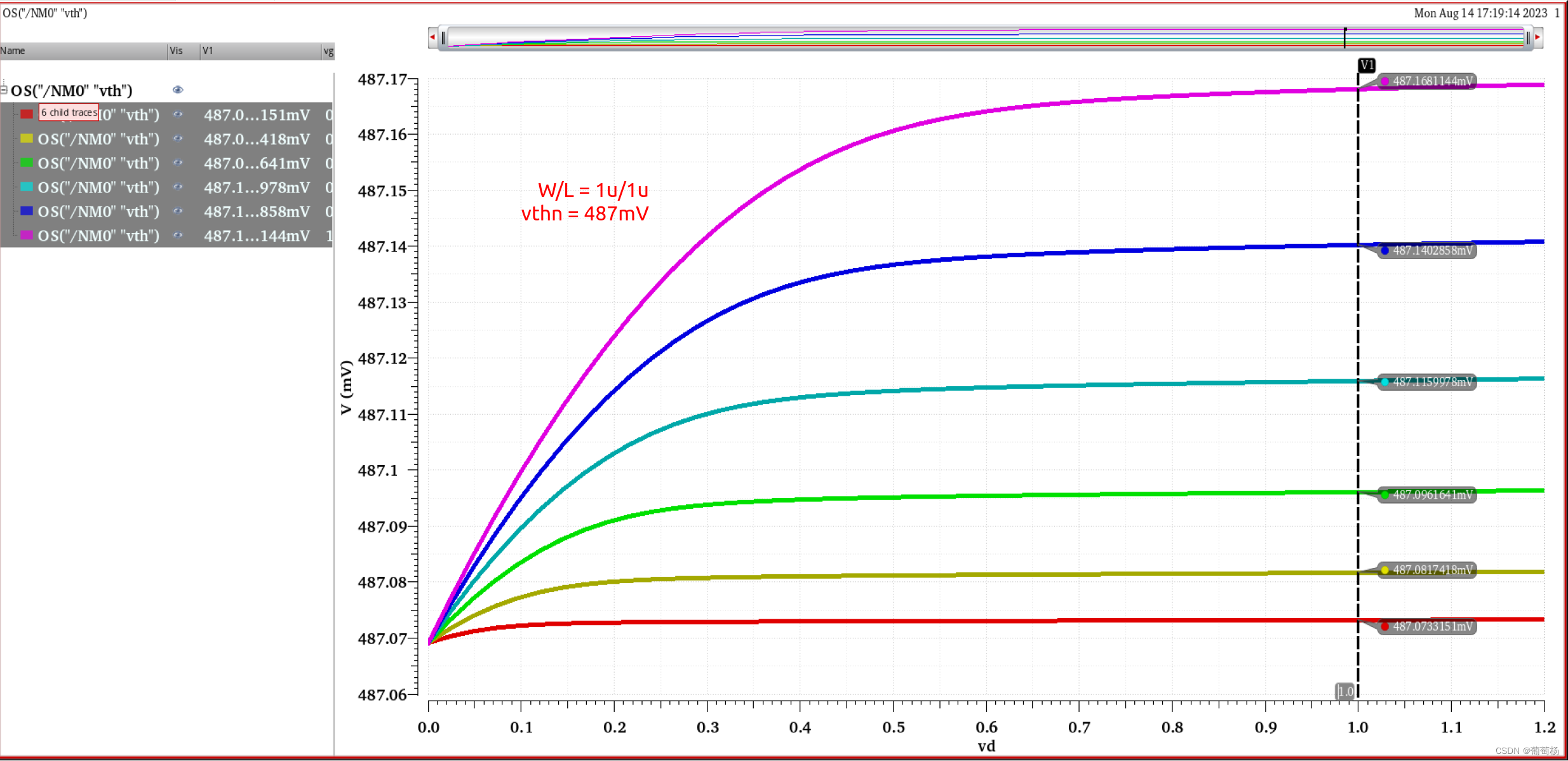

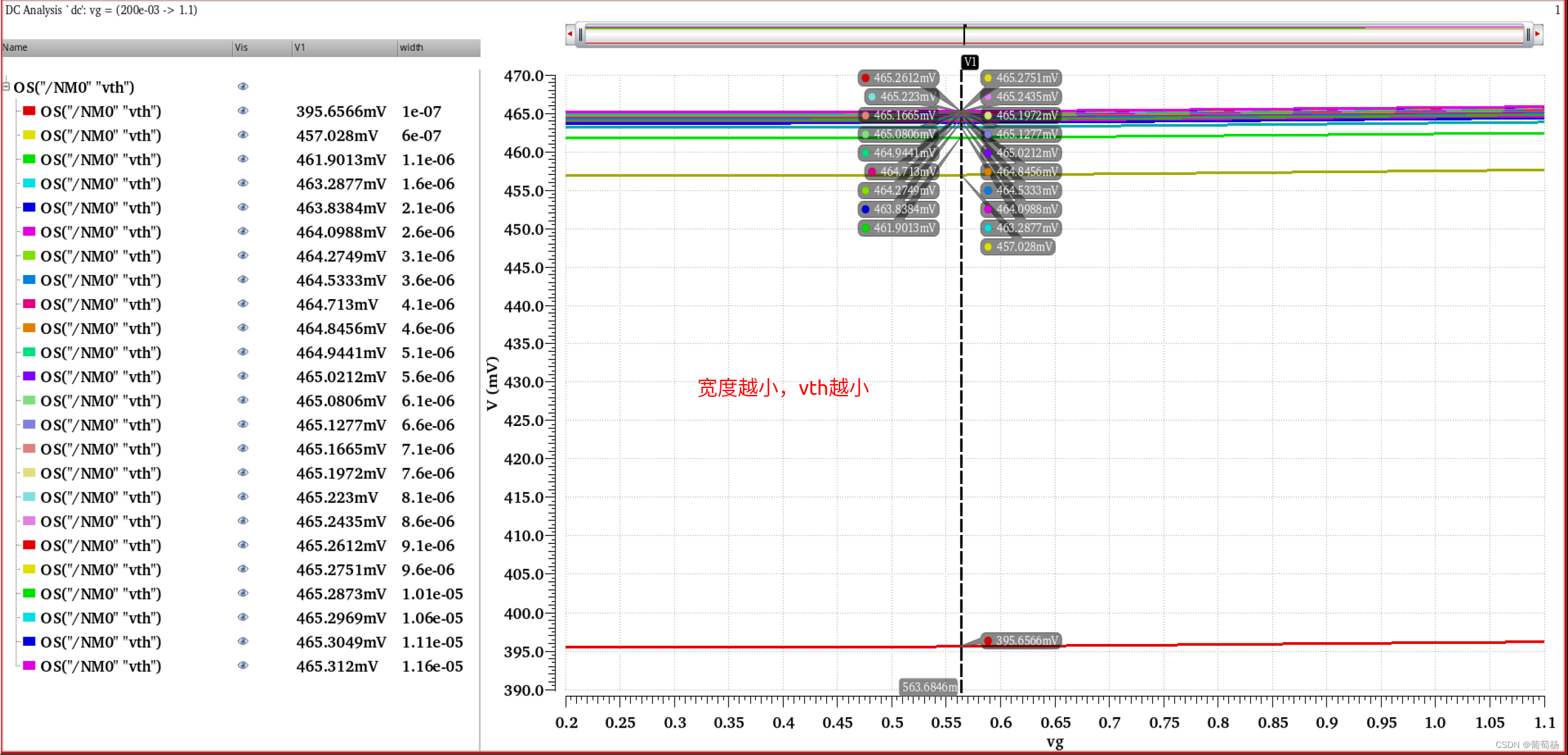

阈值电压随着随着Vgs的增加而增加,随着Vds的增加而降低;

相同条件下PMOS的阈值电压小于NMOS的阈值电压;

阈值电压在400mV ~ 500mV之间;

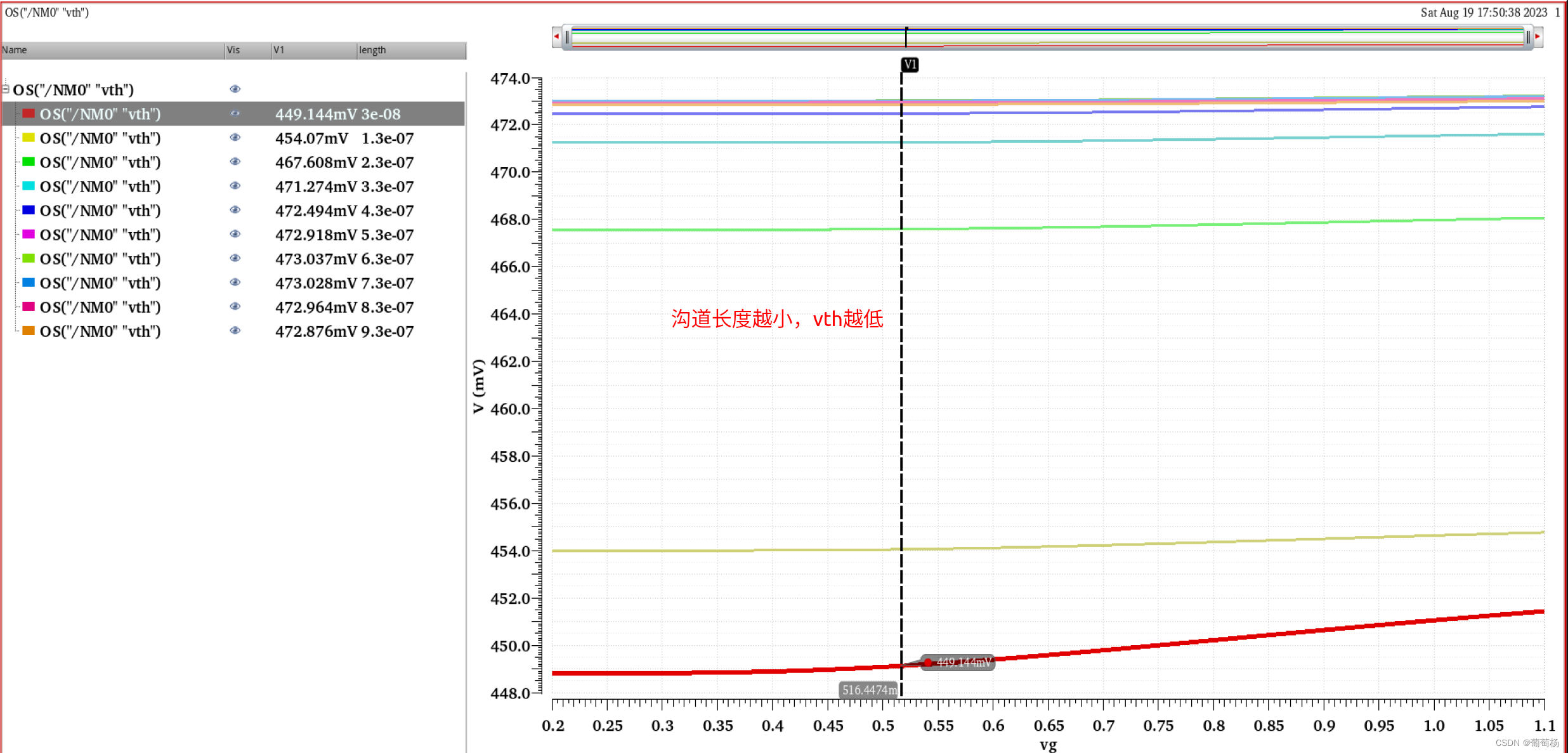

沟道长度越小,vth越低

宽度W越小,vth越低 -

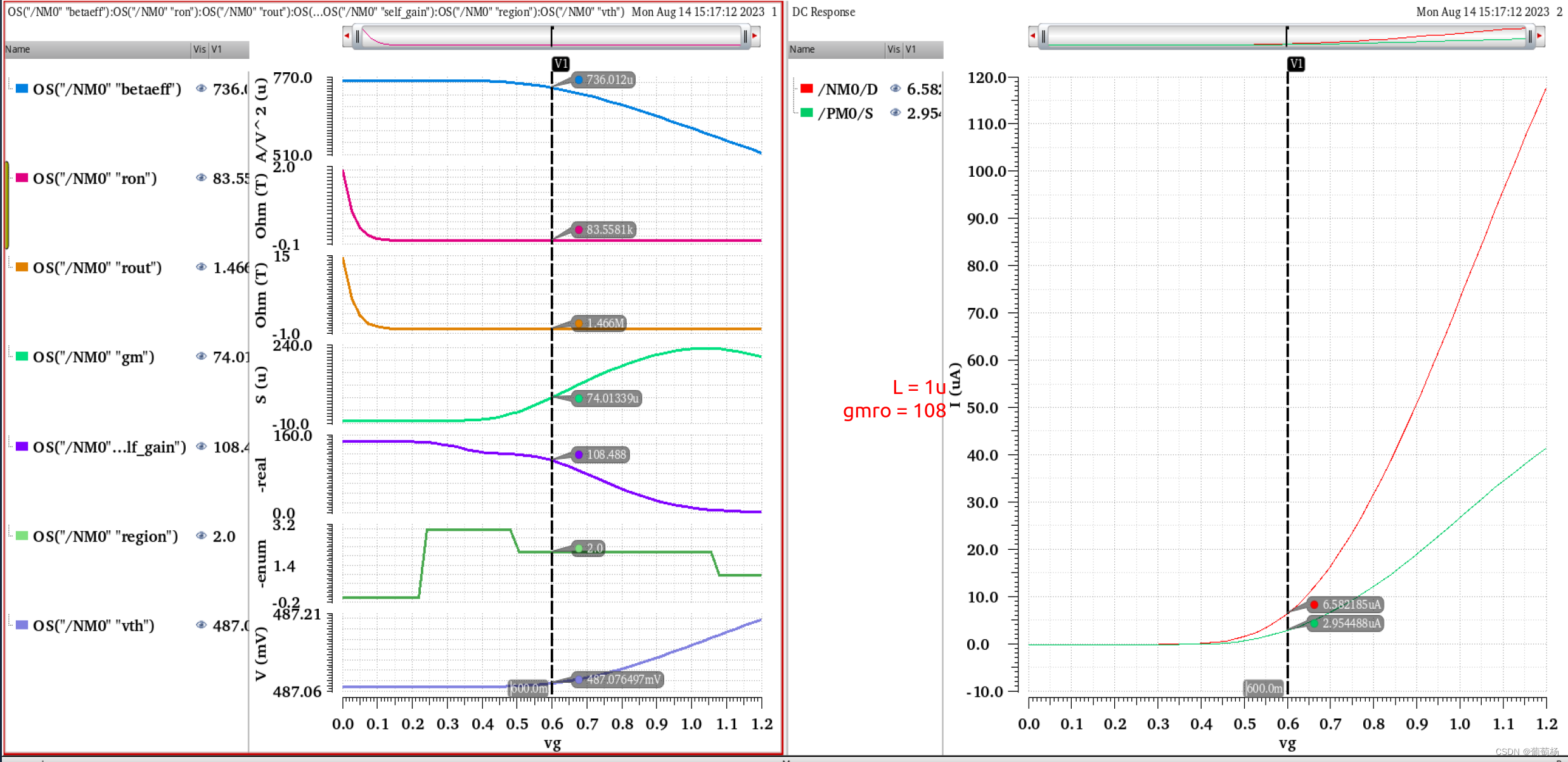

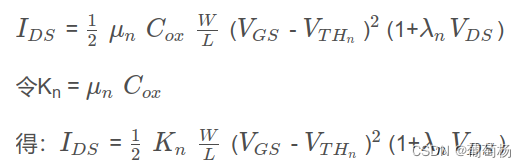

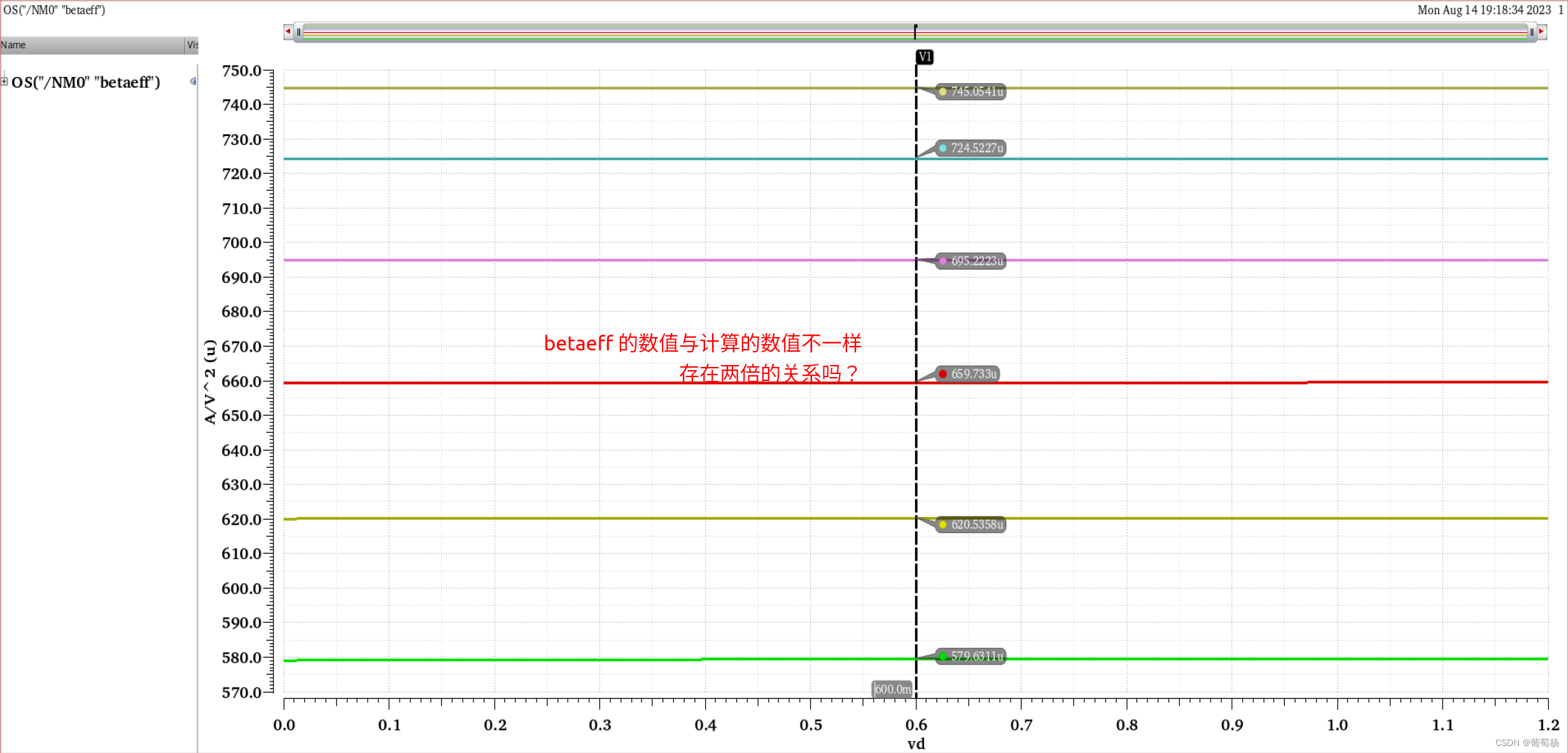

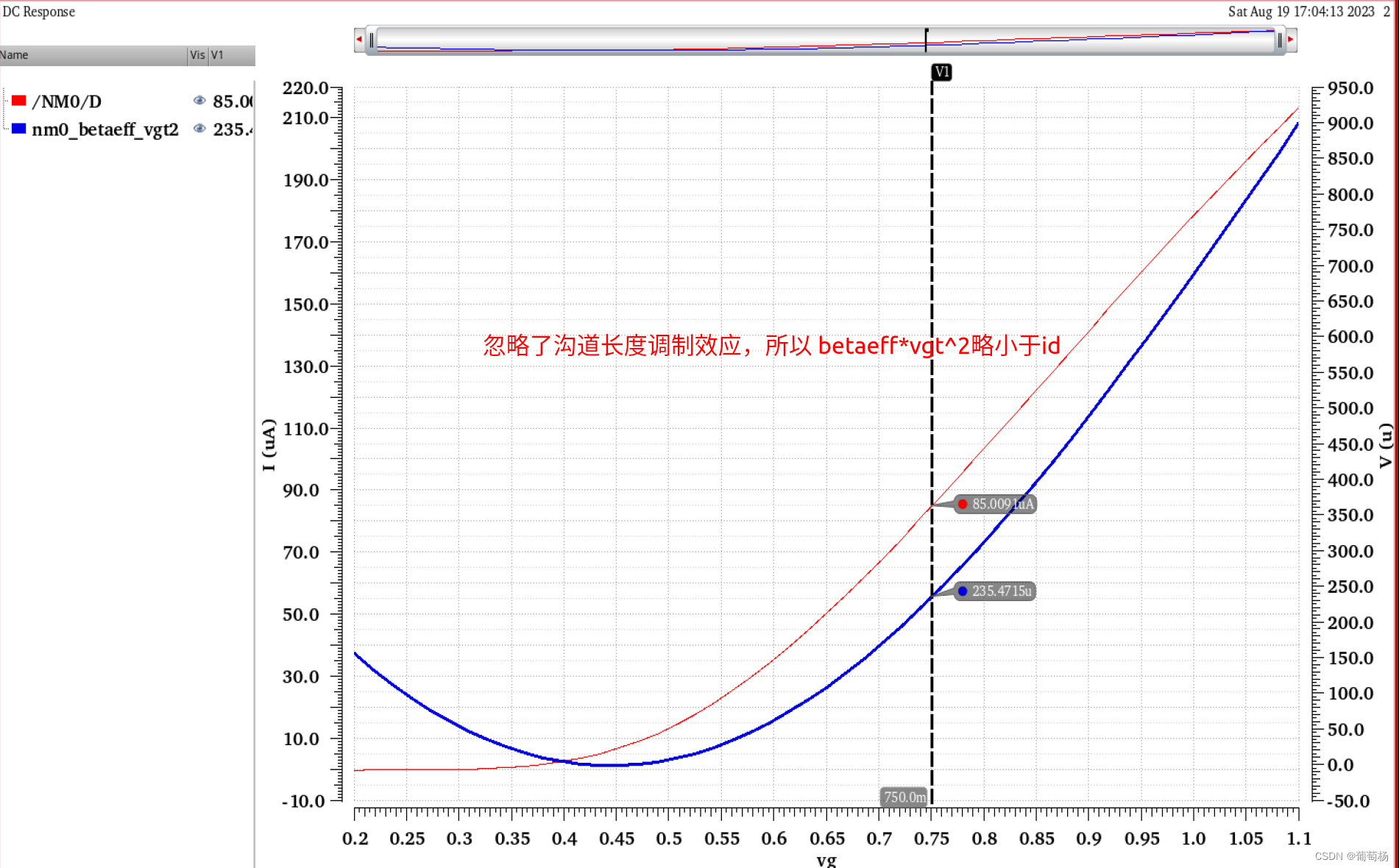

betaeff应该为 I d = 1 / 2 μ C o x W / L ( V g s − V t h ) 2 ( 1 + λ V d s ) I_{d} = 1/2 \mu C_{ox} W/L (Vgs - Vth)^2(1 + \lambda Vds) Id=1/2μCoxW/L(Vgs−Vth)2(1+λVds)中的 1 / 2 μ C o x W / L 1/2 \mu C_{ox} W/L 1/2μCoxW/L

-

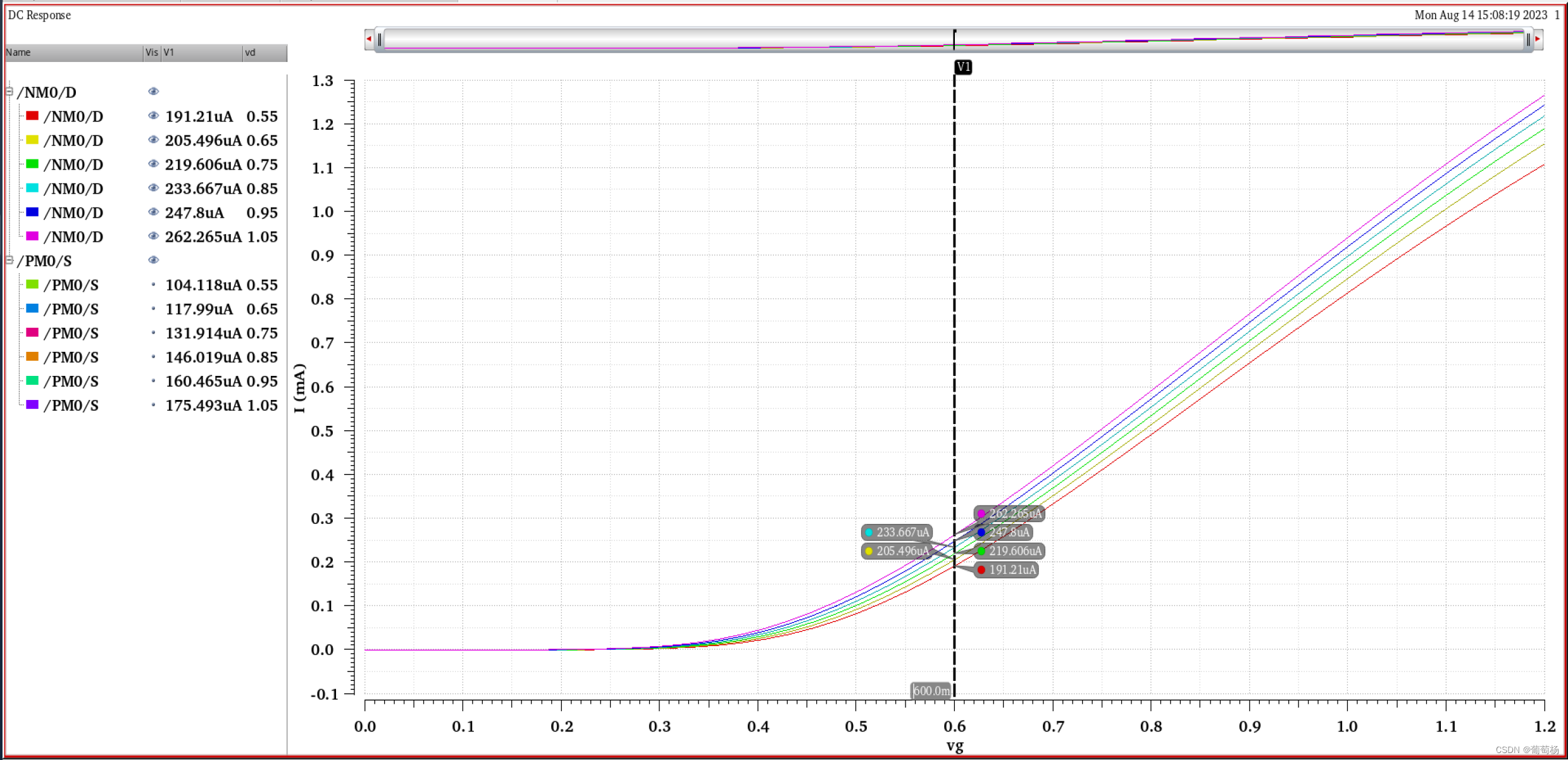

id ~ vgs :

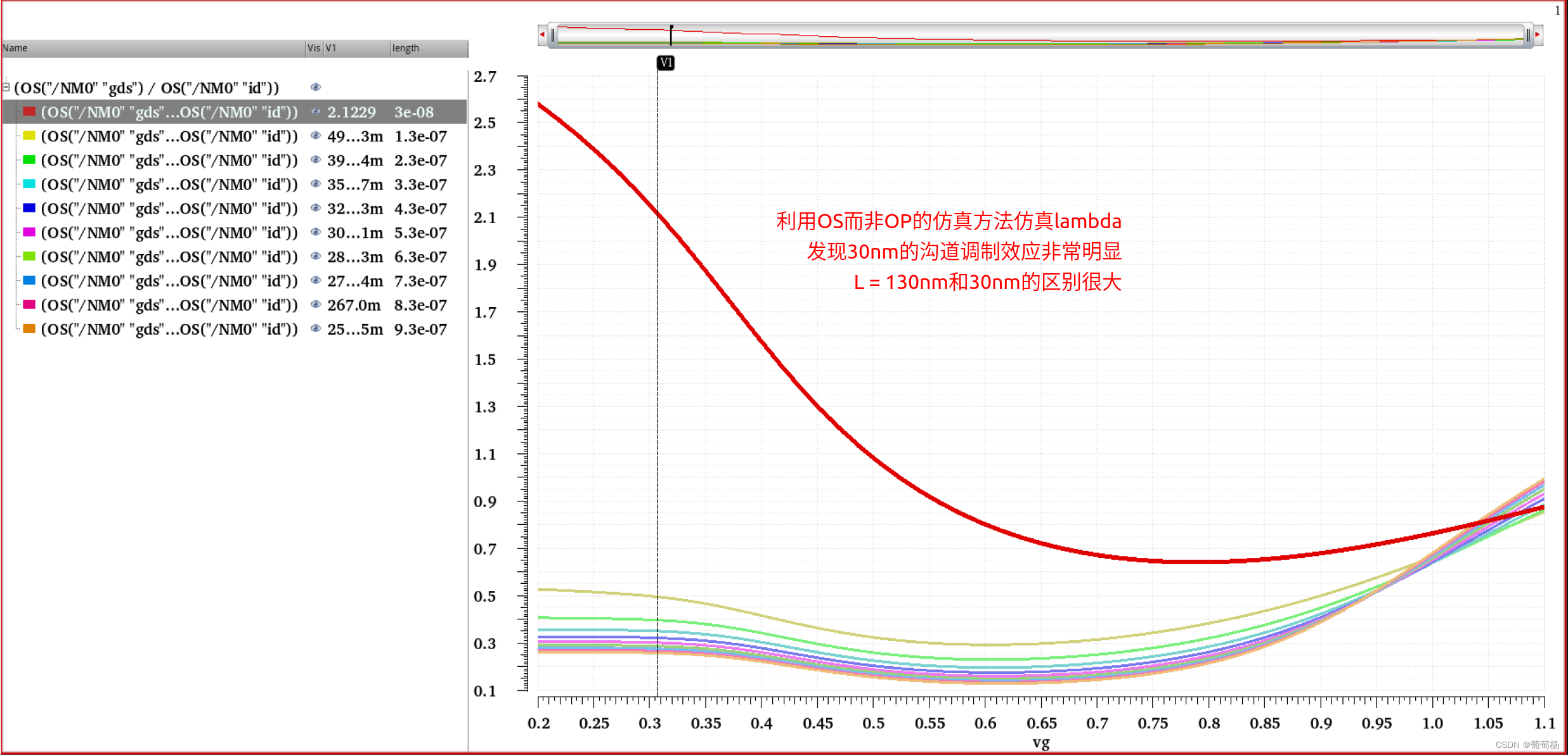

nmos本征增益很低

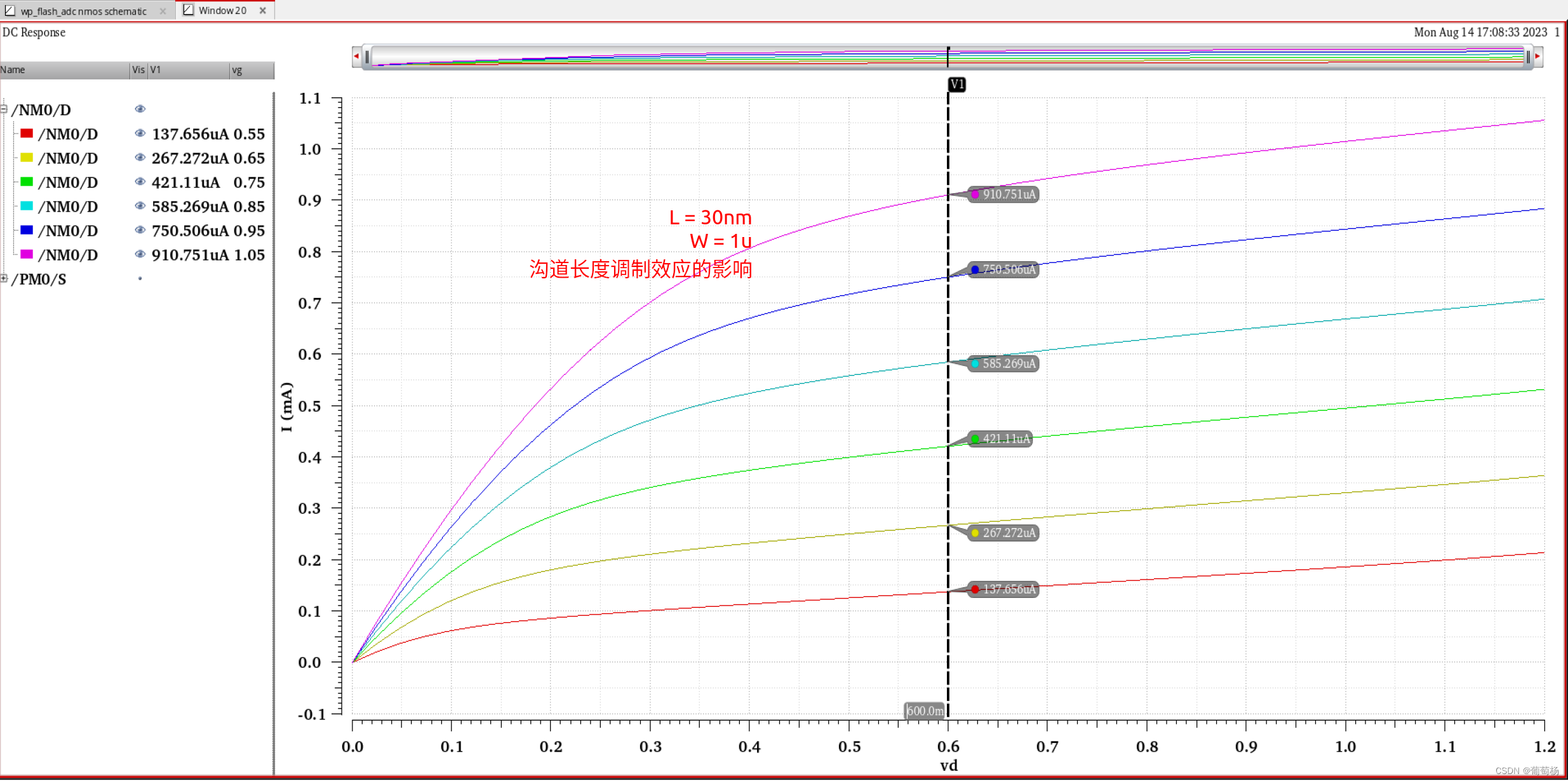

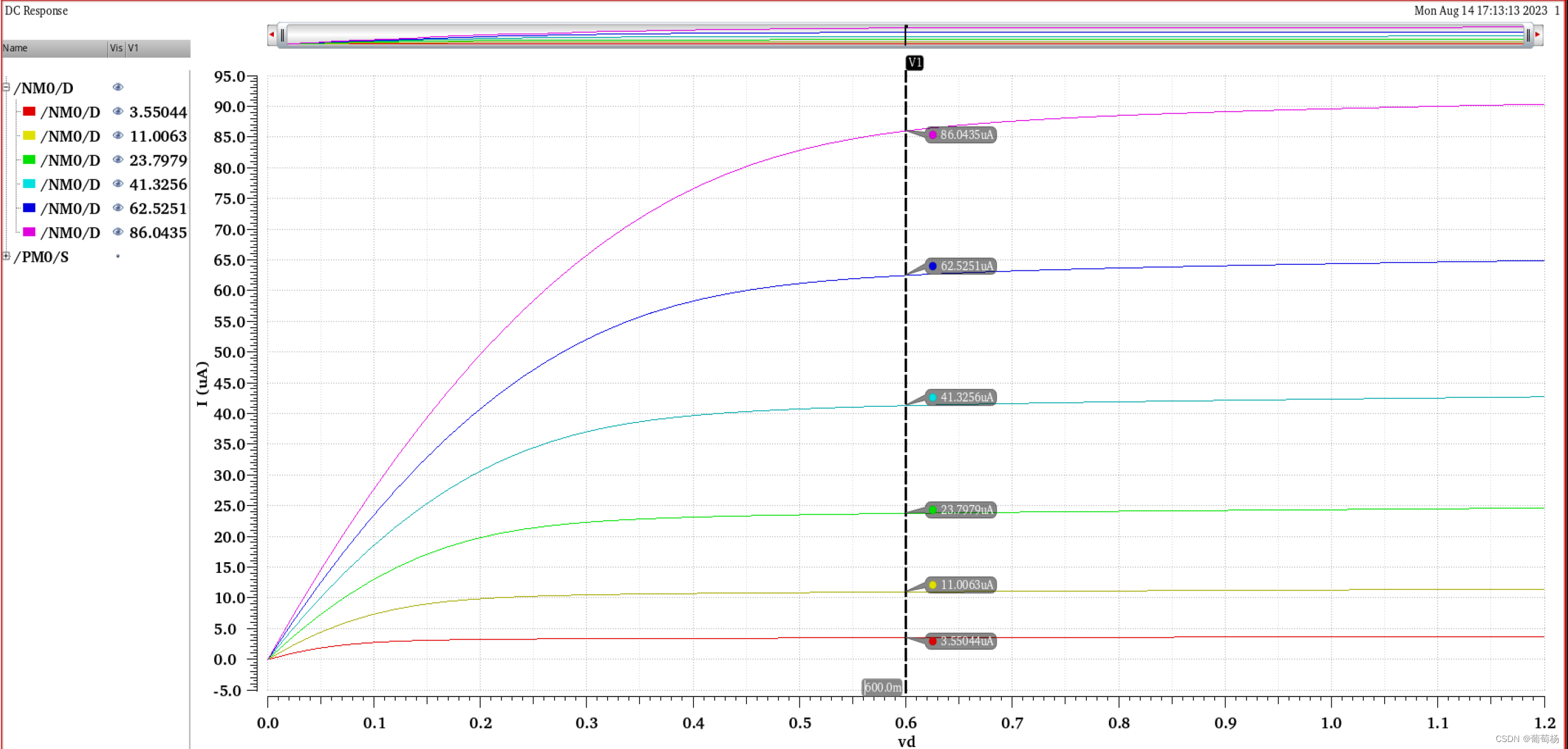

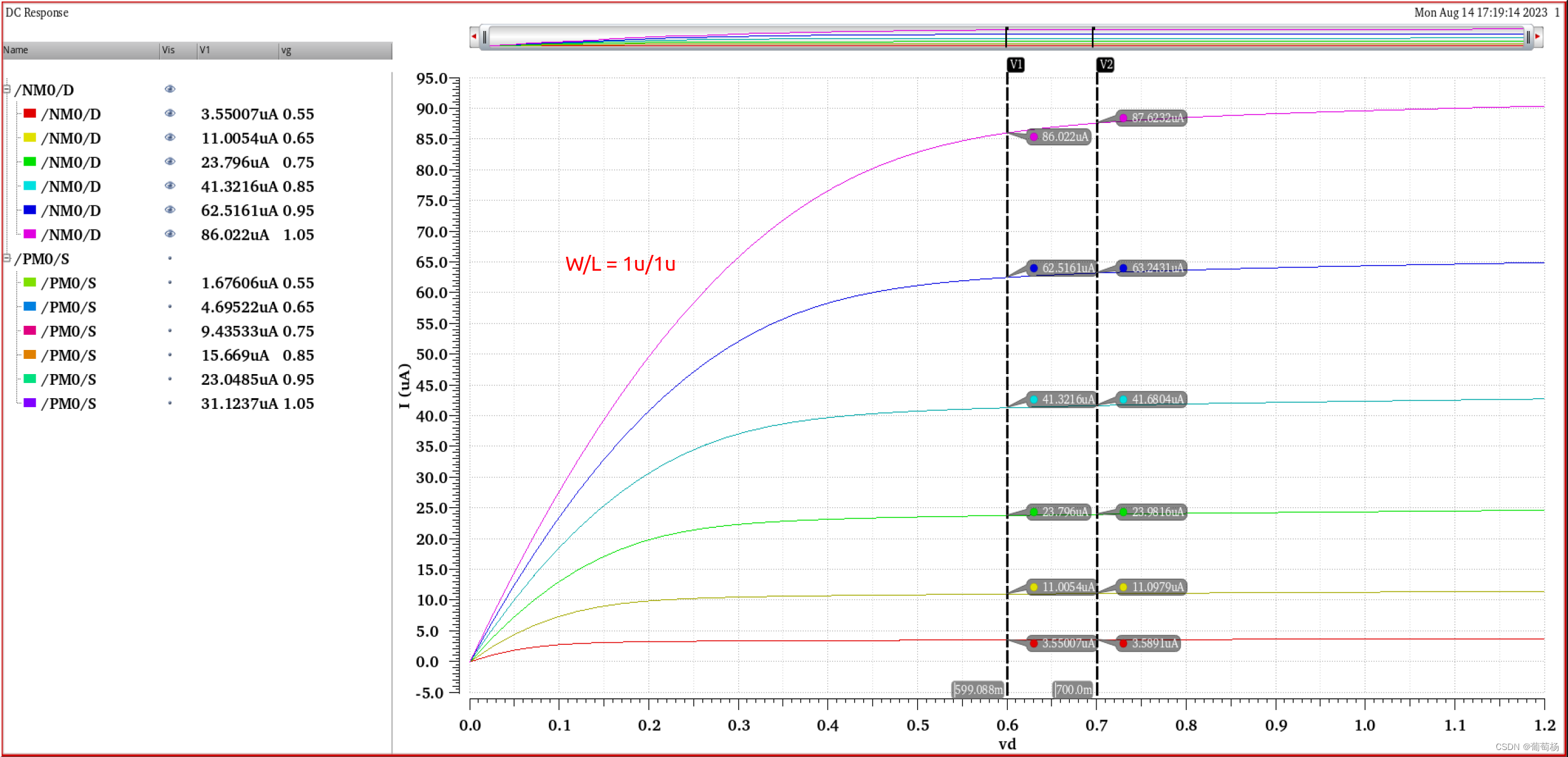

- id ~ vds

- id ~ vds L = 1um, 沟道长度调制效应明显下降

L = 1um, 沟道长度调制效应明显下降

L=30nm,改变vds:

-

vds 和vgs的变化使得阈值电压变化; 阈值电压随着随着Vgs的增加而增加,随着Vds的增加而降低;

pmos的vth小于nmos的vth

pmos的vth小于nmos的vth

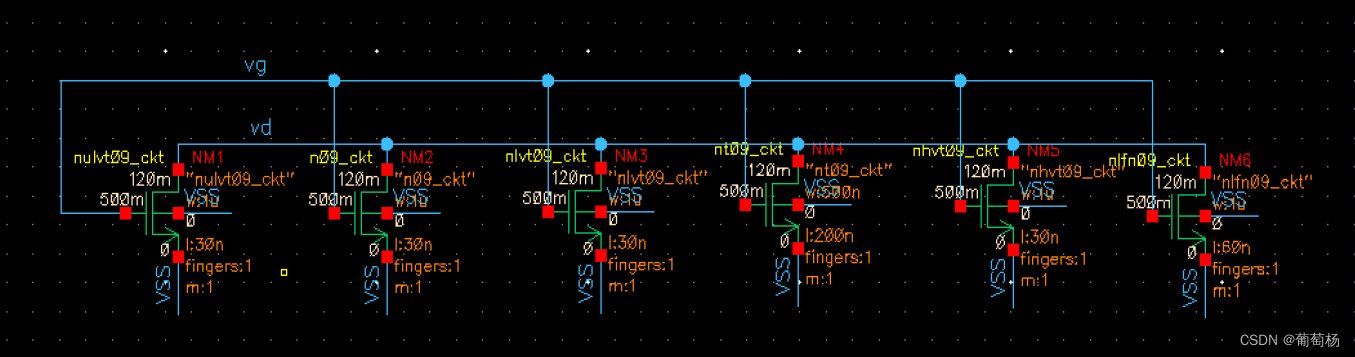

2 不同MOS管的阈值电压

nlfn09_ckt < nulv09_ckt < nlvt09_ckt < nt09_ckt < n09_ckt < nhvt09_ckt

3. 求lambda 和uCox

| vds | vgs | id | 说明 |

|---|---|---|---|

| 1 V | 0.85V | 42.394uA | 求解vth |

| 1 V | 1.05V | 89.648uA | 求解vth |

| 0.6V | 0.95V | 62.516uA | 求解 λ \lambda λ |

| 0.7V | 0.95V | 63.243uA | 求解 λ \lambda λ |

-

根据曲线计算

根据以上公式求解,dc扫描vds,参数扫描vgs

vgs 不变,W/L=1u/1u不变,找到vds ~ id的两组数据

vds = 0.6, vgs = 0.65, W/L = 1u/1u, idn1 = 11.0065uA

11.0054 u A = 1 2 K n ( 0.65 − v t h n ) 2 ( 1 + λ 0.6 ) 11.0054uA = \frac{1}{2} K_n (0.65 - vthn)^2 (1 + \lambda0.6) 11.0054uA=21Kn(0.65−vthn)2(1+λ0.6)

**************************************************************************//

vds = 0.7 vgs = 0.65, W/L = 1u/1u, idn2 = 11.0979uA

11.0979 u A = 1 2 K n ( 0.65 − v t h n ) 2 ( 1 + λ 0.7 ) 11.0979uA = \frac{1}{2} K_n (0.65 - vthn)^2 (1 + \lambda0.7) 11.0979uA=21Kn(0.65−vthn)2(1+λ0.7)

等式左右两侧相除,

11.0054 11.0979 = 1 + 0.6 λ 1 + 0.7 λ \frac{11.0054}{11.0979} = \frac{1+0.6 \lambda}{1+0.7\lambda} 11.097911.0054=1+0.7λ1+0.6λ

解答为 λ = 0.088 \lambda = 0.088 λ=0.088,

**************************************************************************//

换成vgs=0.95的数据进行计算

62.516 63.243 = 1 + 0.6 λ 1 + 0.7 λ \frac{62.516}{63.243} = \frac{1+0.6 \lambda}{1+0.7\lambda} 63.24362.516=1+0.7λ1+0.6λ

λ = 0.125 \lambda = 0.125 λ=0.125

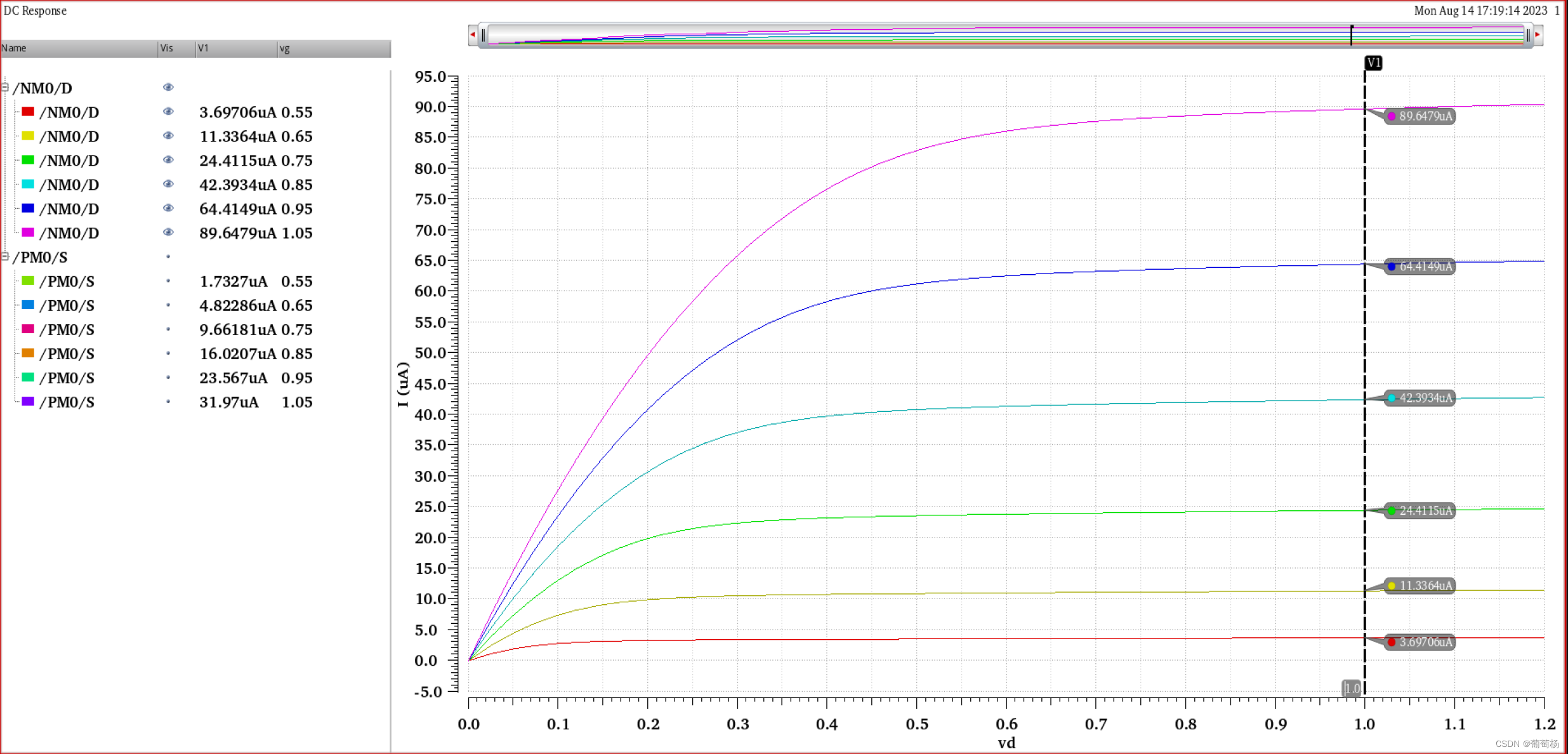

vds 不变,W/L不变,找到vgs ~ id的两组数据

vds 不变,W/L不变,找到vgs ~ id的两组数据

vds = 1, W/L = 1u/1u

vgs = 0.85, id = 42.394uA

vgs = 1.05, id = 89.648uA

42.394 u A = 1 2 K n ( 0.85 − v t h n ) 2 ( 1 + λ × 1 ) 42.394uA = \frac{1}{2} K_n (0.85 - vthn)^2 (1 + \lambda \times 1) 42.394uA=21Kn(0.85−vthn)2(1+λ×1)

89.648 u A = 1 2 K n ( 1.05 − v t h n ) 2 ( 1 + λ × 1 ) 89.648uA= \frac{1}{2} K_n (1.05 - vthn)^2 (1 + \lambda \times 1) 89.648uA=21Kn(1.05−vthn)2(1+λ×1)

此处等式左右两侧同时相除得到vthn

vthn = 0.4096V = 410mV

而实际的NMOS阈值电压约等于487mV

将阈值电压vthn的值和带入公式可以得出 Kn

λ = 0.125 \lambda = 0.125 λ=0.125,vthn = 0.41V,带入 62.516 u A = 1 2 K n ( 0.95 − v t h n ) 2 ( 1 + λ 0.6 ) 62.516uA = \frac{1}{2} K_n (0.95 - vthn)^2 (1 + \lambda0.6) 62.516uA=21Kn(0.95−vthn)2(1+λ0.6)

求得Kn = 398uA/v2

当仿真器给出的 beta eff 的数值却与实际不符

betaeff 指的是

1

/

2

μ

C

o

x

W

/

L

1/2 \mu Cox W/L

1/2μCoxW/L,下图可以验证,由于忽略了沟道调制效应,所以betaeff计算出来的电流略小于实际的id

betaeff 指的是

1

/

2

μ

C

o

x

W

/

L

1/2 \mu Cox W/L

1/2μCoxW/L,下图可以验证,由于忽略了沟道调制效应,所以betaeff计算出来的电流略小于实际的id

-

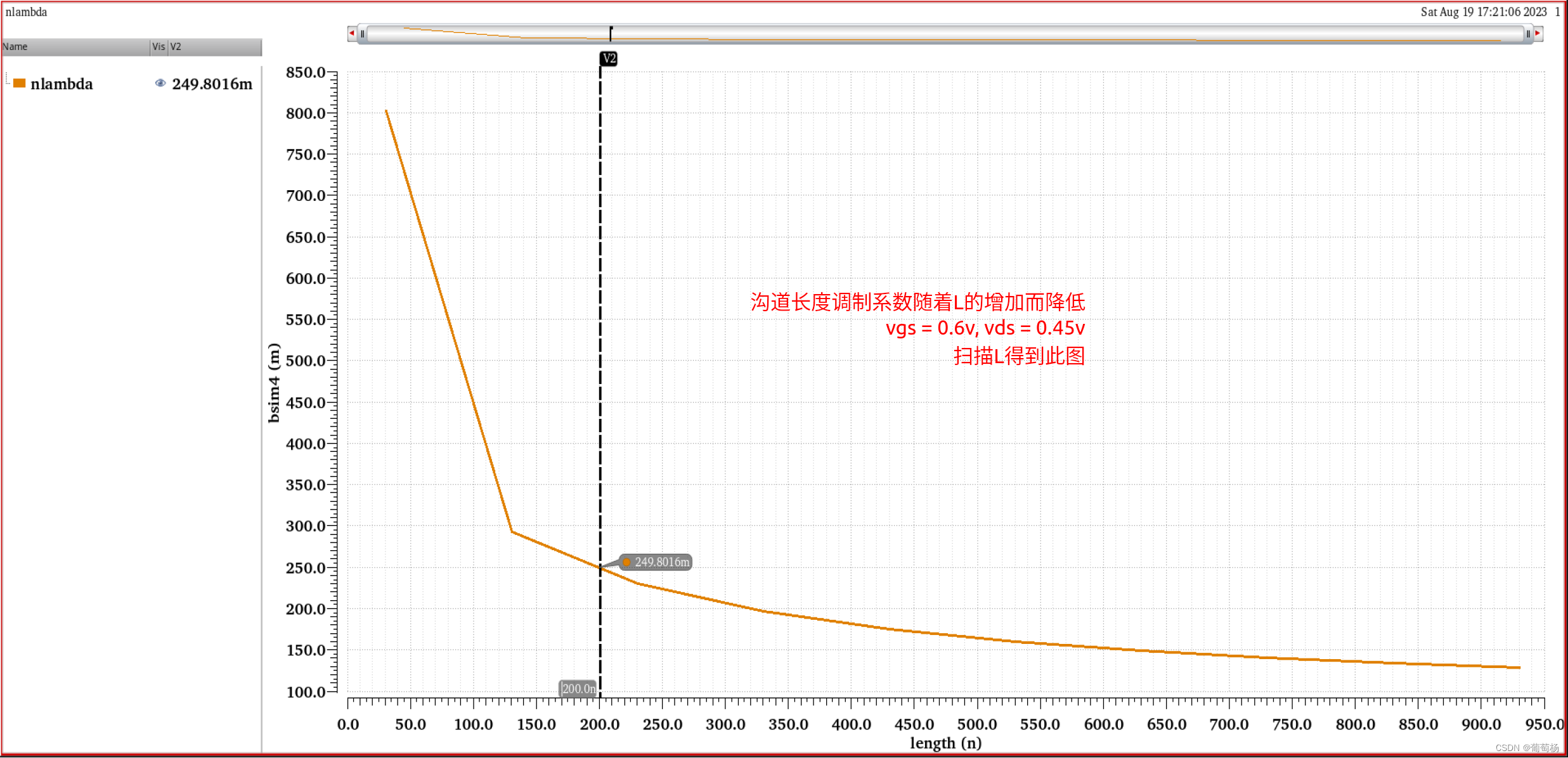

沟道长度调制系数

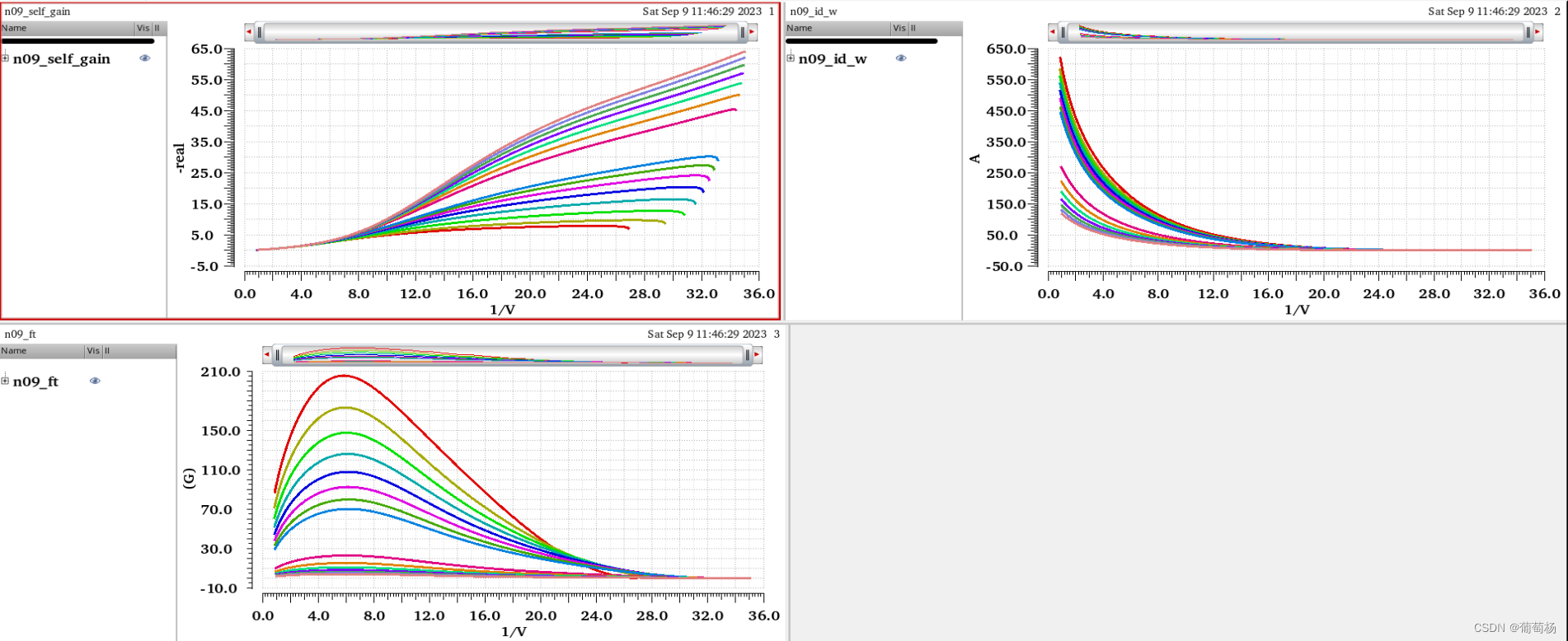

3. 1 gm over id的设计方法

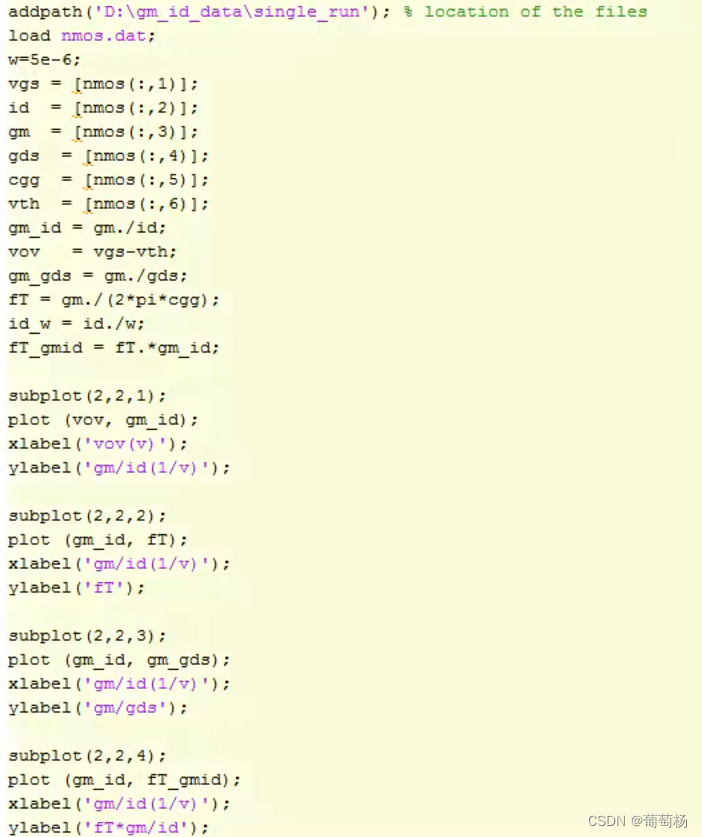

down :表示单调递减;up表示单调递增

- gm over id ~ vgs (down)

- ft ~ gm over id (down),频率

- gm/gds ~ gm over id,增益

- ft x gm over id ~ gm over id ,频率和增益的最优点

- id/w ~ gm over id (down),电流密度,根据gm_id和id可以求出w

- Vov ~ gm over id (down)

- 仿真数据可以仿真获取

印度人教程

https://www.bilibili.com/video/BV1z5411P7fm?p=4&vd_source=bcace3d35b0cb8317d1be57f5a838c27

-

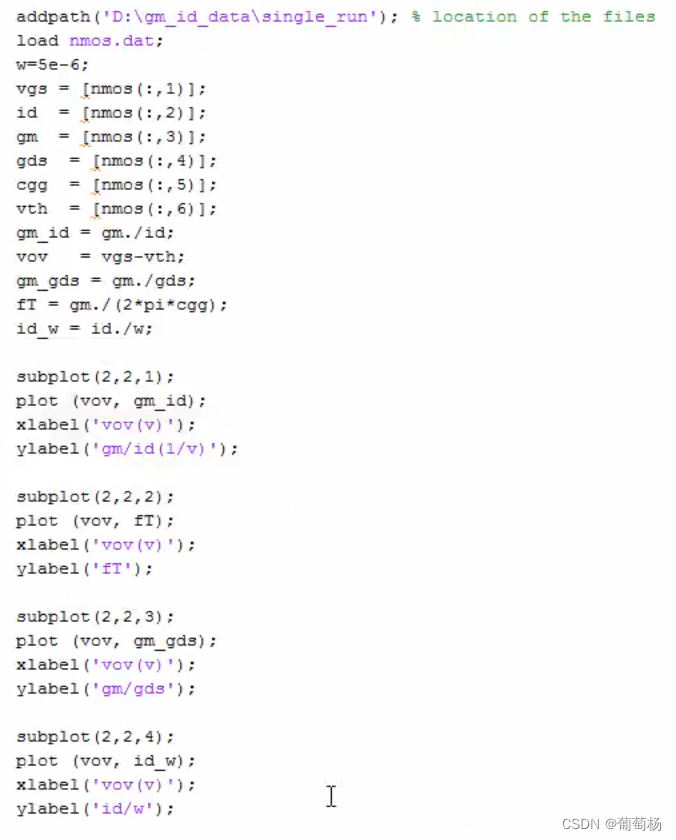

导出数据,matlab画出 各个指标随vgs - vth的变化曲线;

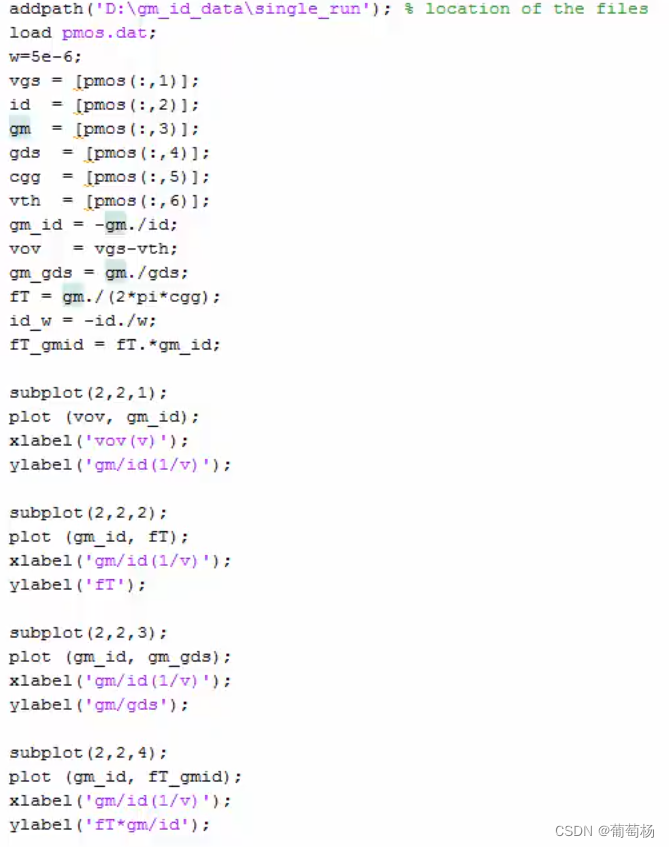

- 导出数据,matlab画出 各个指标随gm over id的变化曲线;

- 导出数据,matlab画出 各个指标随gm over id的变化曲线;

-

pmos 加上负号即可

-

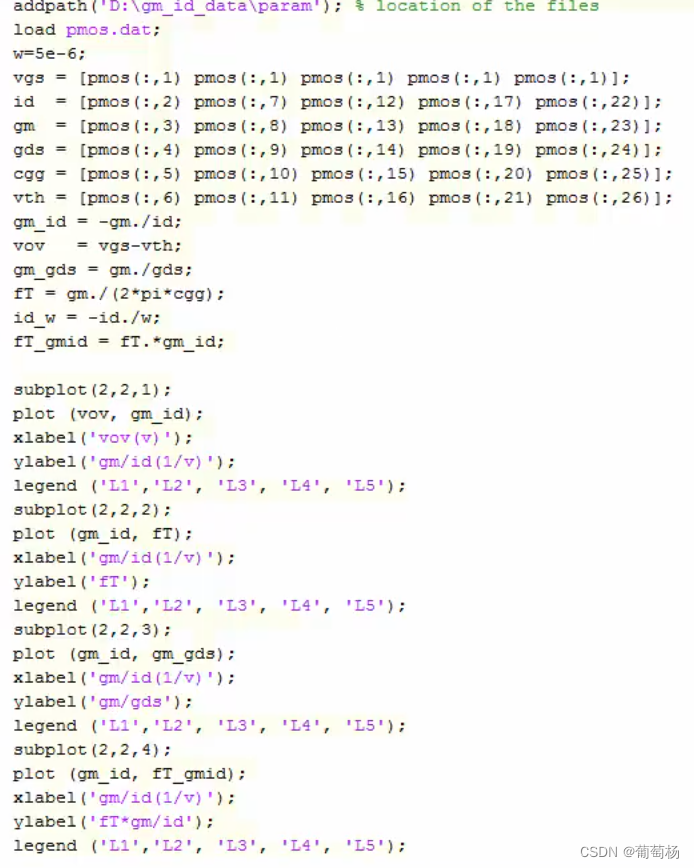

5种length的结果

subplot (m,n,p)

% 在一个图形窗口中创建一个m行n列的子图,并选中第p个子图。

在这里插入图片描述

4. 电路指标设计

-

输入电压的限制:最小值:Vgs1 + M5的过驱动电压(Vgs5-vthn5),最大值:Vdd - M3的过驱动电压(Vsg3-vthp3)。

-

输出电压限制:最小值:M7的过驱动电压(Vgs7 - vthn7)

-

失调电压: 对于差分输入,单端输出。输入失调电压定义为单端输出电压为𝑉𝐷𝐷 /2时的差分输入值。失调电压指直流失调。系统失调来源于电路结构即使电路中所有的匹配器件都相同也会存在;随机失调来自于应匹配器件的失配。

-

M3, M4, M6有相同的过驱动电压,即 I D W / L \frac{I_D}{W/L} W/LID要相等

-

从稳定性角度考虑,M6 要有大的跨导从而小的沟道长度;从低噪声和随机输入失调考虑,M3 和 M4 要有小的跨导从而大的沟道长度。

在纳米技术中,5管运放增益很难超过10。而带宽由负载电容决定。gm3 /CE是M3和M4之间的镜像极点。

- 指标

- vdd = 1.1 V

- 共模电压 0.55V,输入电压范围0.5V - 0.7V

- 相位裕度大于60

- 带宽 50Mhz

- 直流增益50dB

- 静态功耗大约10uW

- 负载电容2pf

- 摆率 50V/us

- 增益50dB(316)

设计过程

10.

G

B

W

=

g

m

2

C

c

GBW = \frac{gm2}{Cc}

GBW=Ccgm2(rad/s)

11. 零点大于10GBW,

z

=

g

m

6

C

c

>

10

g

m

2

C

c

z= \frac{gm6}{Cc} > 10 \frac{gm2}{Cc}

z=Ccgm6>10Ccgm2, gm6 > 10gm2

12. 根据相位裕度的要求

C

c

>

0.22

C

L

Cc > 0.22CL

Cc>0.22CL

13. M3, M4, M6的电流密度要一致

14. 根据摆率要求设计第一级尾电流,一般将运放的输入对偏置在接近亚阈值区,此时其 gm/Id 越大,即相同偏置电流下,可获得更高的跨导。将输入对 M1、M2 的过驱动电压设置为 0.1V

15. 输出电阻正比于

L

/

I

L/I

L/I

gm over id 图像

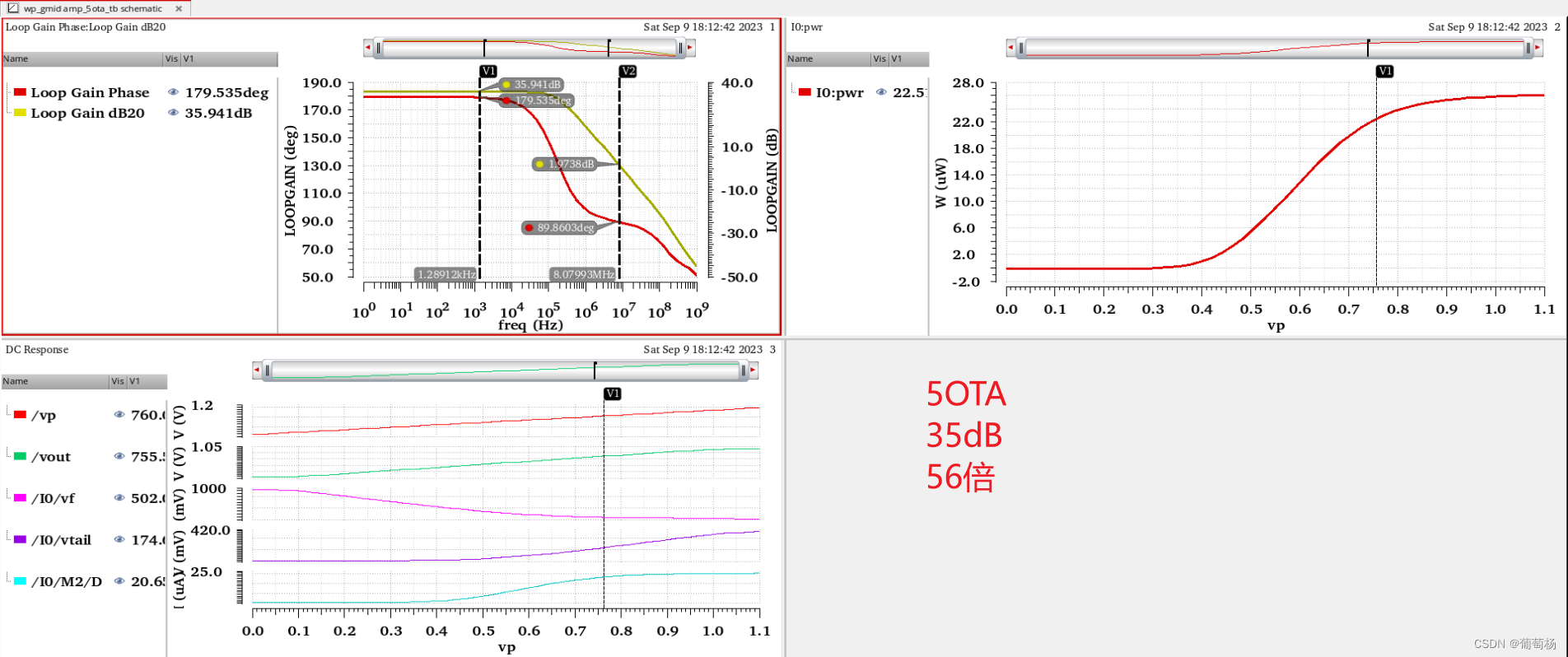

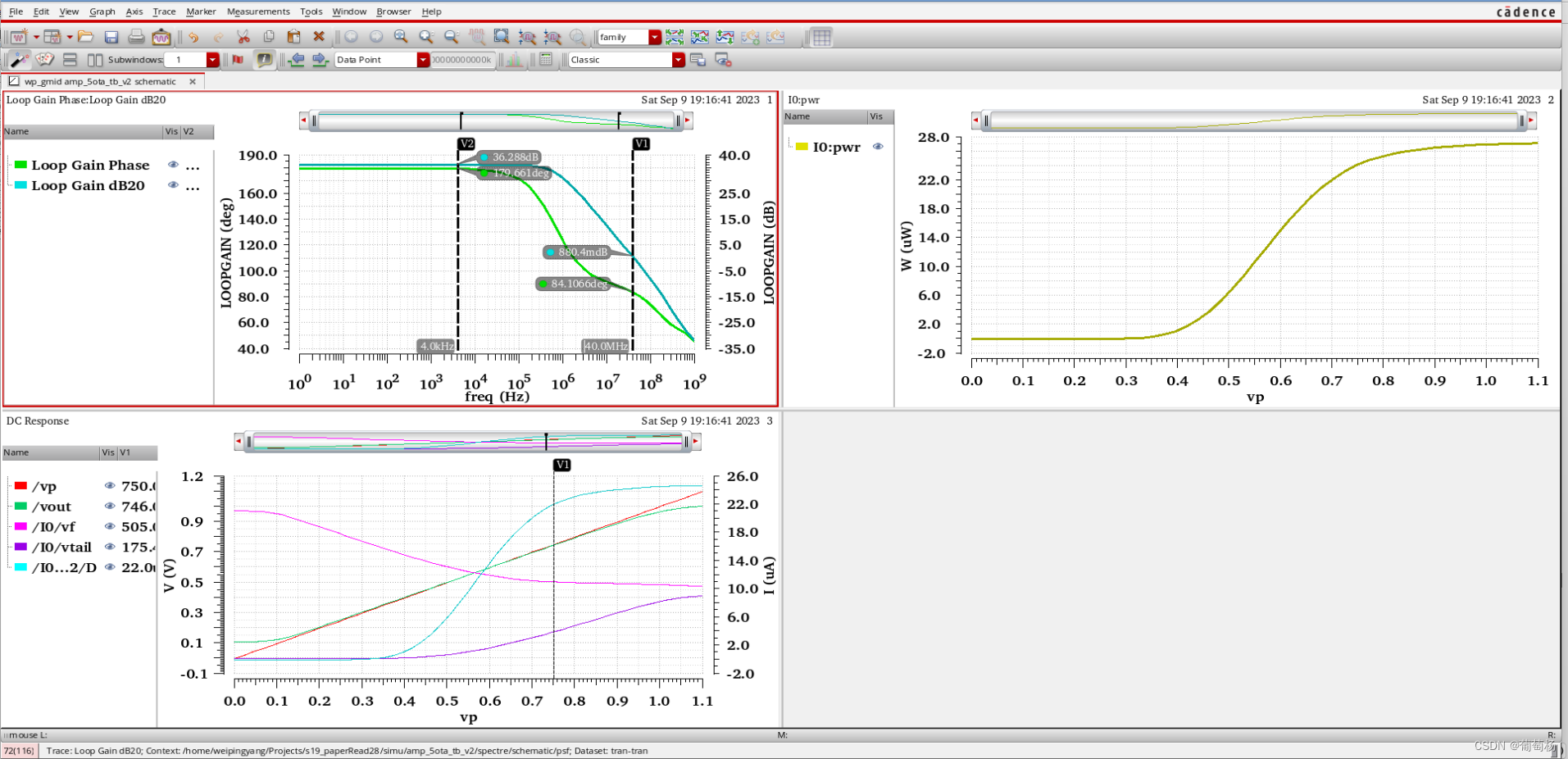

5. 运算放大器设计结果:

36dB:

其他设计笔记

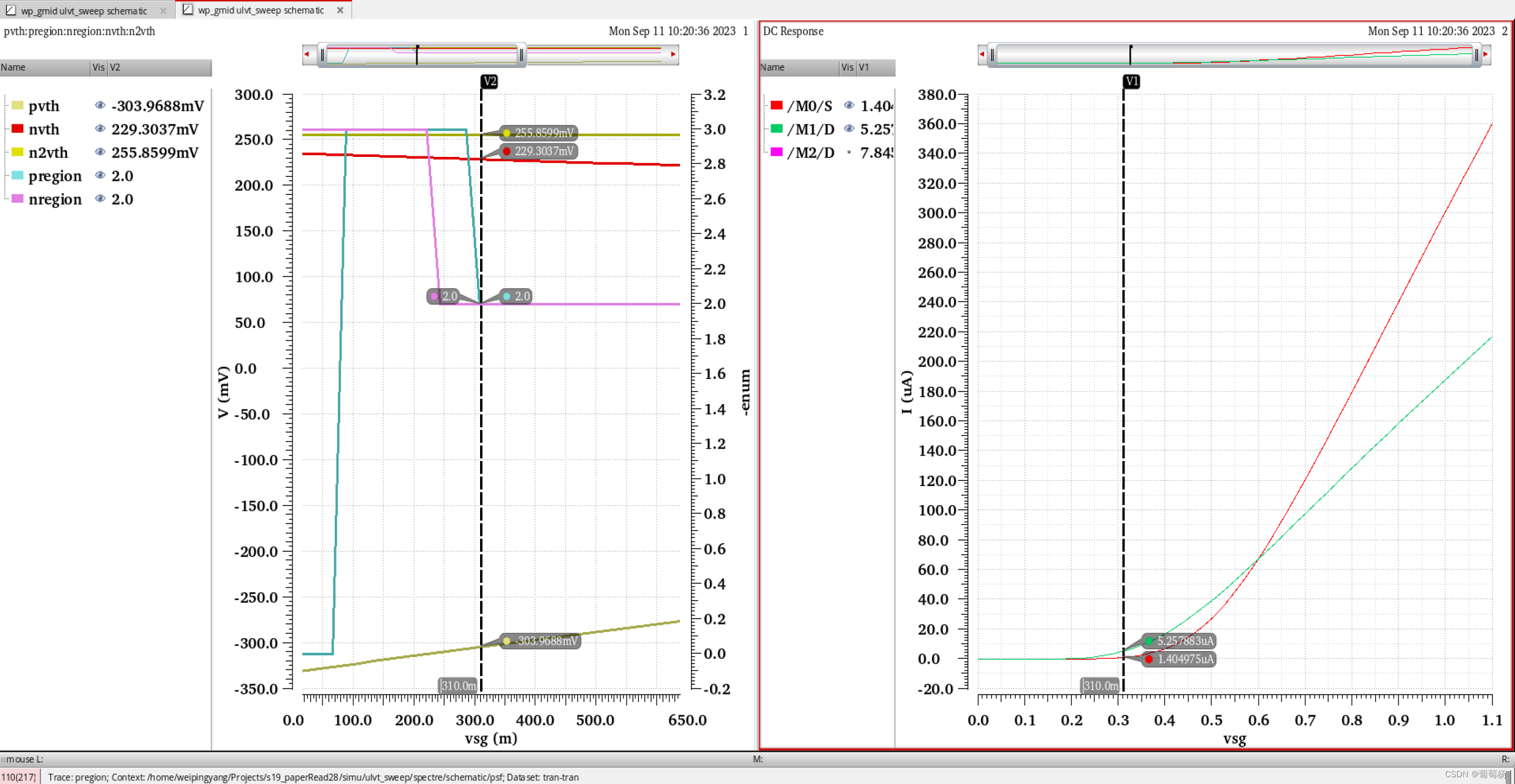

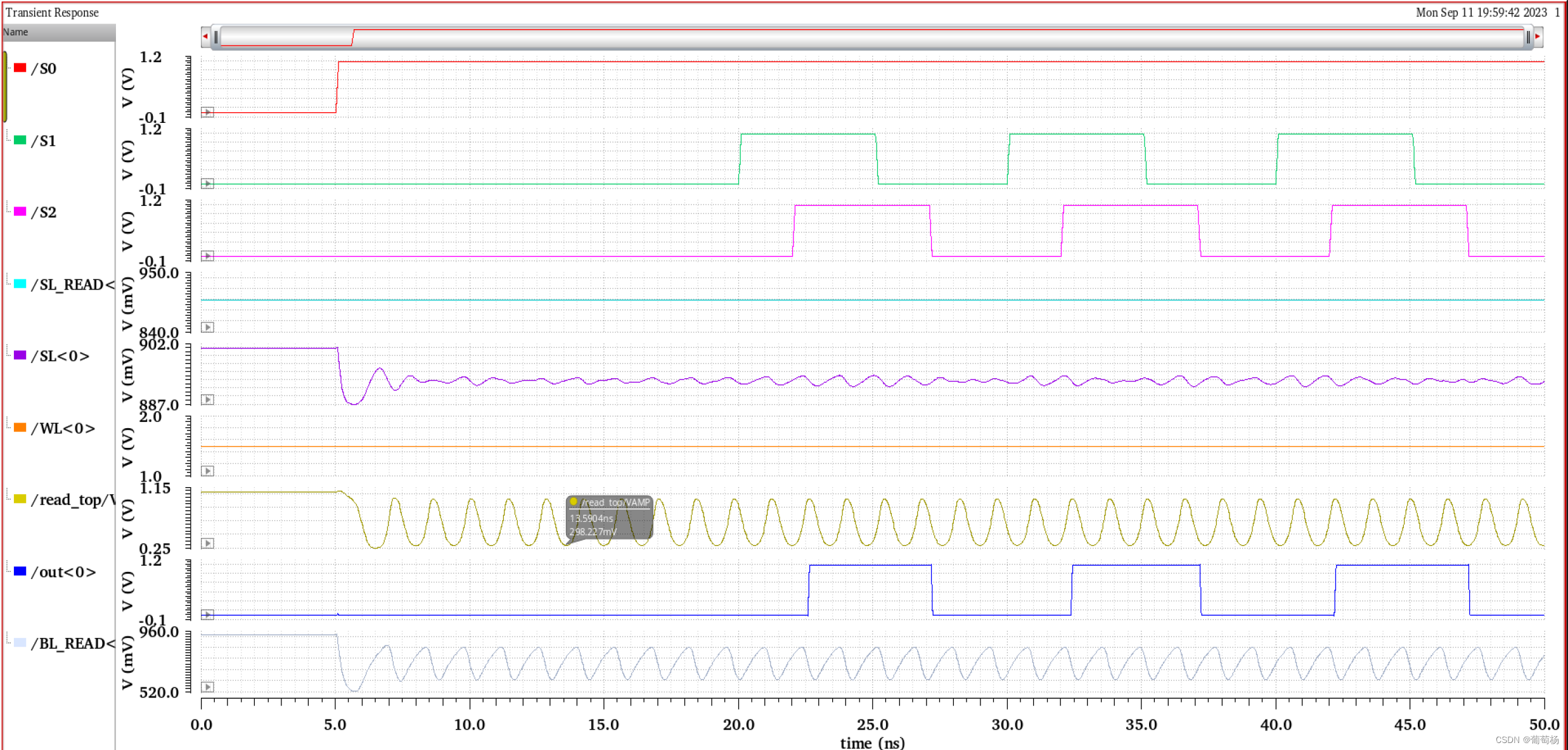

1. 饱和区临界情况的电流

- PM1要满足region=2的饱和区,消耗的电压裕度小于1.1-0.75V=0.35V,并且此电压需要保证PM1导通,即大于vth。分配340m, region=2符合条件,此时其宽长比为300n/30n, vth = 301mV, vsg=340m时,电流等于2.56uA。如果增大PM1的长度,选择/L= 500n/50n时,340m的电压无法保证PM1位于饱和区。因此选择PM1的尺寸为300n/30n。尽管此举可能使得电流镜复制的精度降低。

- 选择NM2时,同样需要保证其位于饱和区,nulvt的vth较低,可选择长度较长的MOS管,150n/60n的宽长比使得其可以位于饱和区。仿真表明其vth = 0.23V左右,vgs为260mV时可以保证NM2的region = 2。

- 为了留足相应的电压余量,设计时取pmos的vsg = 348m, nmos的 vgs = 250m。此时电流为3uA。因此取偏置电流为3uA。此时pmos和nmos消耗的电压为348.846m和252.407m。

- 同时以上仿真也说明,如果MOS管位于饱和区,则其流过的电流会有一个下限,否则即便vg = vd其也不会位于饱和区。以PMOS W/L = 300n/30n为例,其位于region = 2的饱和区时其电压vsg = 310m,此时其电流为1.4uA左右。所以此电路的最小测量电流为1.4uA。

发现嵌位电压在0.75V时运算放大器的尾电流管不在饱和区,因此设置嵌位电压为0.8V。因此需要找到阈值电压vthp小于300mV的pmos。不过这点很难达到。实际上只要保证vds > vgt即可保证pmos位于饱和区,然而由于沟道长度调制效应的影响,电流复制的精度会受到影响。

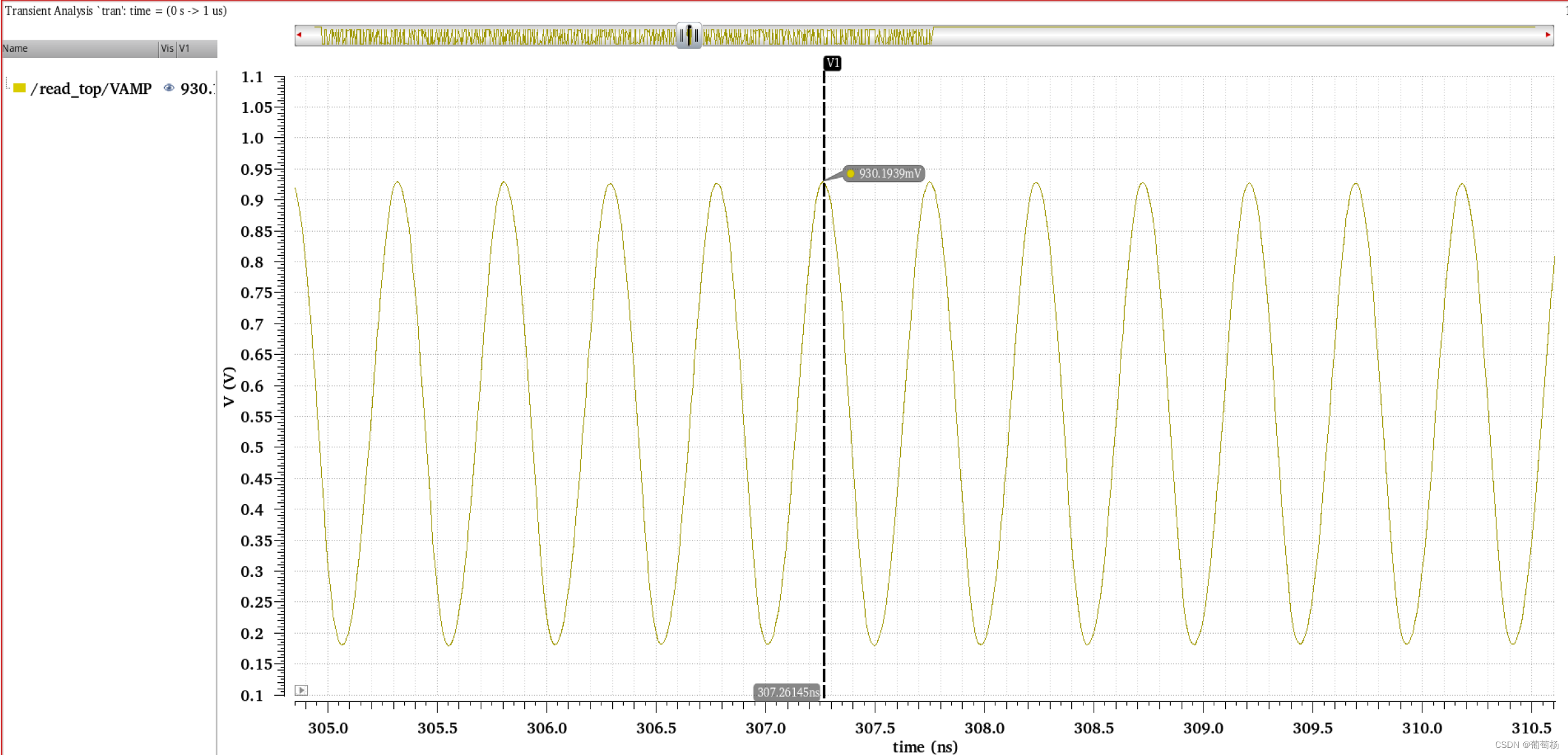

2. 电压满足情况

- 由于amplifier的输出电压最小值可到vamp = 0.56V。此举需要满足2个阈值电压vthn的要求,以上步骤已知其中一个nmos管的尺寸为150n/60n。此时其阈值电压的大小为0.23mV。根据电流大小,150n/60n消耗的电压余量至少为252mV。假设电流大小为15uA时,其vgs为449mV。留给开关mos管的电压余量为[vamp - 0.252, vamp - 0.449]。

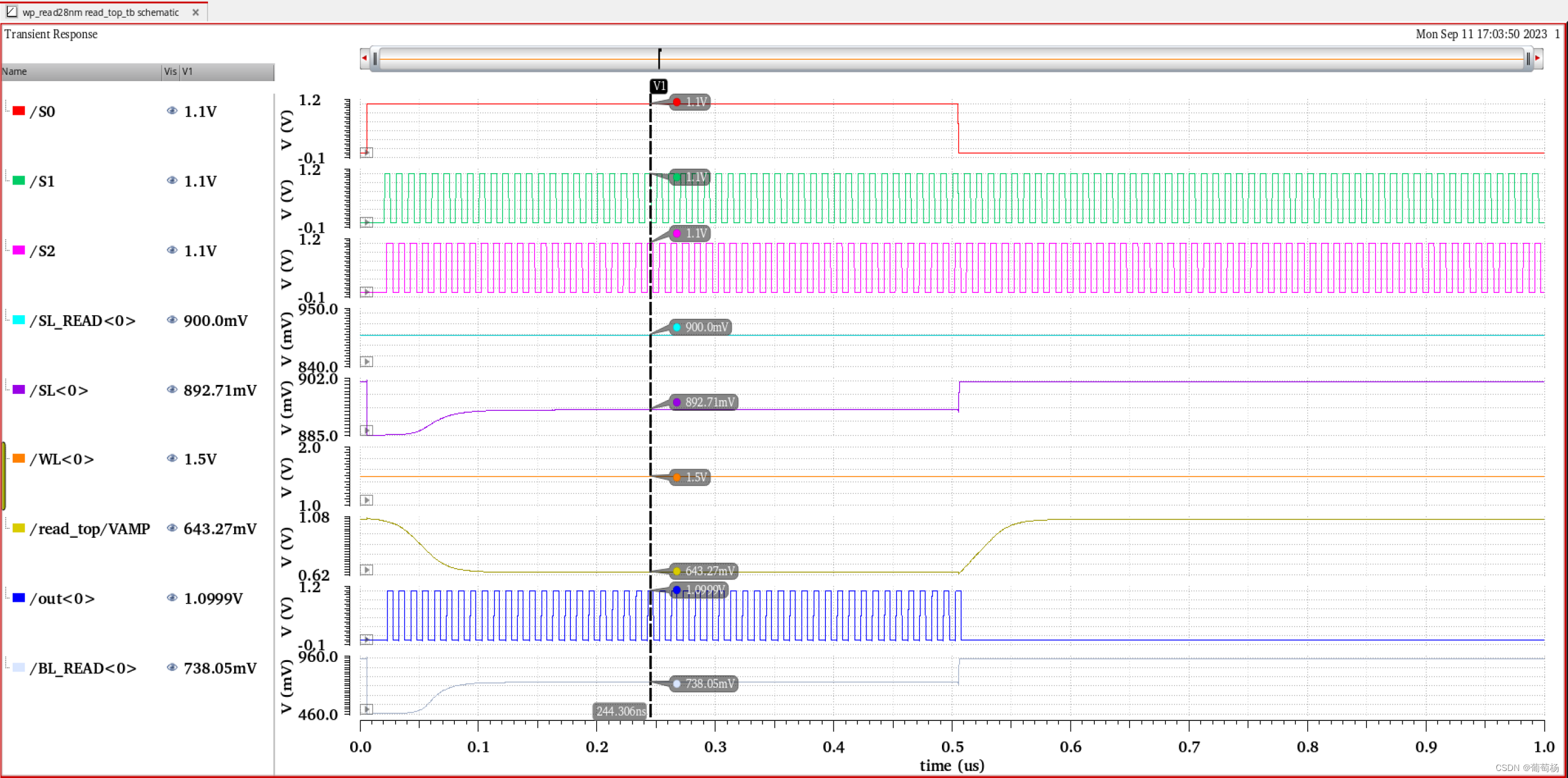

3. 阵列设计

导通电阻和导通电流之间的平衡。导通电阻为$ ron = \partial vds / \partial id$,vds越大,则导通电阻越小。因此实际施加到vds上的电压很小。

- HRS/LRS = 130k/30k。2V的写电压情况下其导通电流 2V/30k = 0.067uA, 2V/130k = 0.0154uA。电流较小。28nm工艺库中取n18_ckt的器件保证写操作可以正常进行。

- 假设其长度取最小值L = 150n。由于电流较小,因此1T1R阵列的w/l取值较小,假设取值w/l = 270n/150n,这也是mos管尺寸的最小值。假设分配在memristor两端的电压为0.2V, 与读电路相连的端口电压为0.74V。则mos管S端的电压为0.94V = 0.2V + 0.74V。则G端电压为0.94V + vth。w/l = 270n/150n时其vth = 573mV。从而大于1.513V。在vg = 1.8, vs = 0.95, vd = 1.1, 即vgs = 0.85v, vds = 0.15v时,流过MOS管的电流较大,大概18uA。此配置不可取。

- 实际上假设0.2V的电压施加到memristor上,其HRS电流为0.001538462uA,电流极小,LRS电流为0.006666667, 电流也很小。因此需要减小MOS管的宽长比。W取最小值270n,w/l = 270n/450n时,其vhtn = 500mV。经过仿真可得到以下结果。其中vds = 0.15mV。

- w/l = 270n/150n vthn = 573mV

- w/l = 270n/270n vthn = 532mV

- w/l = 270n/540n vthn = 490mV

- 导通时n18_ckt的电流都在uA级

- 降低vds的电流

4. 仿真过程中的震荡问题

-

有电容补偿,Av = 52dB。电压比较稳定。

-

如果取消补偿电容,则会发生振荡

-

5管运放也会产生此问题。

-

continue

1677

1677

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?