一、基础理论

随着现代技术的发展,MOS管沟道越来越短,在长沟道工艺下器件的平方律模型逐渐被淘汰,不再适用于目前的工艺65nm及其以下,在当前的设计工作中,计算机仿真更多的采用BSIM4模型,该模型的计算方式更为复杂,拥有更多的参数考虑,本文的Gm/Id方法可不用知道MOS管的电子迁移率μ和栅氧化层电容Cox,直接通过查找表的方法求出MOS管的宽长比,达到设计目标。

二、设计指标

GBW=10M Hz、CL=1p F、Av=70 dB

三、设计流程

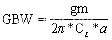

选取电路结构:折叠Cascode,电路图结构如下所示:

1、设计思路——指标分析

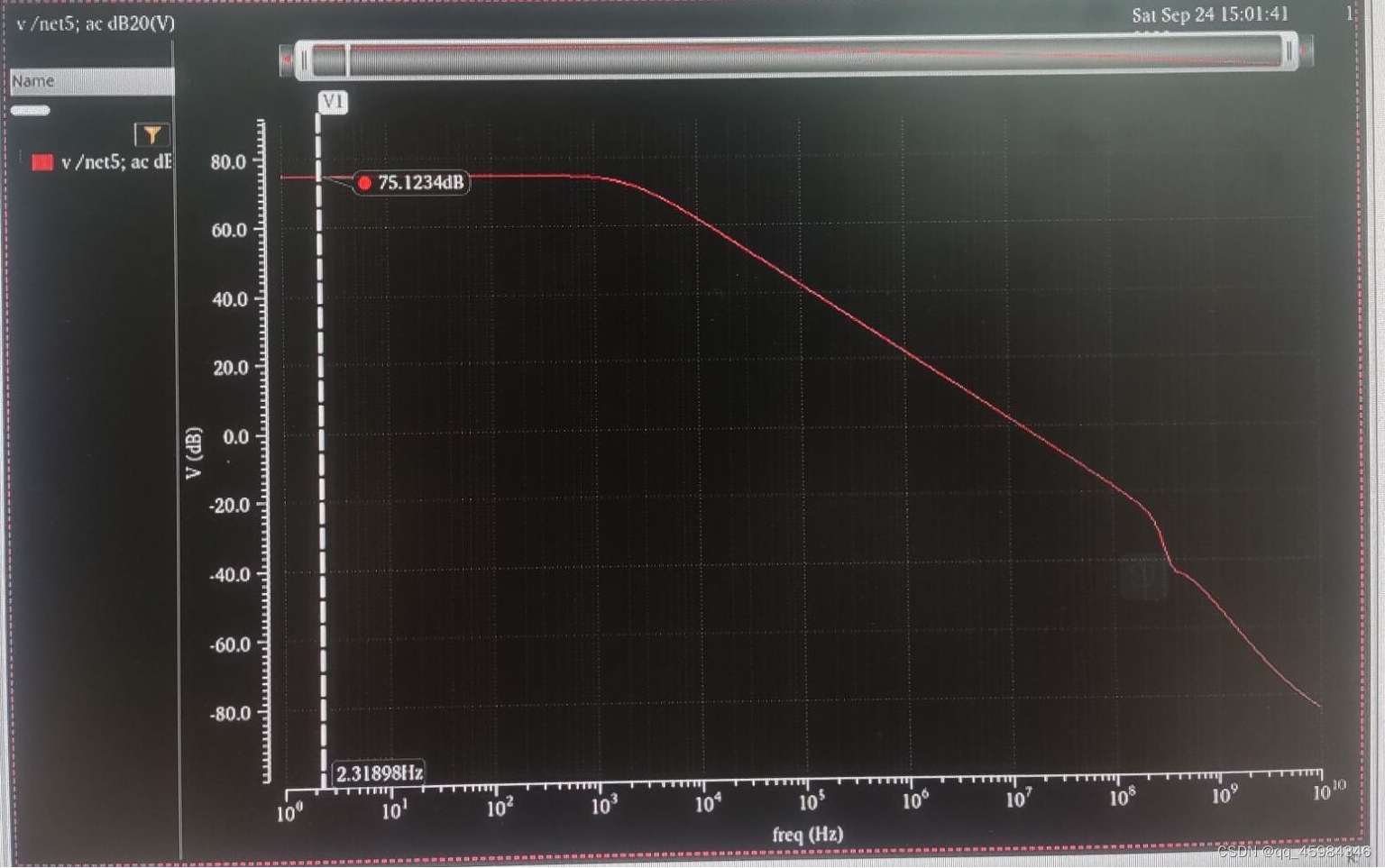

①确定输入管M1、2跨导:根据GBW=10M Hz,CL=1p F,由公式 (a为工程经验值,一般可取1.2 --1.4,猜测原因可能考虑寄生电容影响,本文选取1.2),得出gm=75.36μ S,选择80μ S

(a为工程经验值,一般可取1.2 --1.4,猜测原因可能考虑寄生电容影响,本文选取1.2),得出gm=75.36μ S,选择80μ S

②确定增益:由Av=70 dB,根据dB=20lgAv1得出Av1=3162,选取为3500,(选择稍大范围,便于后续调节MOS管参数)

③确定其余MOS管参数:根据折叠共源共栅增益计算公式![]() ,该设计仅为简略估计,故忽略gmb,选择gm6ro6=self_gain6;gm8ro8=self_gain8。

,该设计仅为简略估计,故忽略gmb,选择gm6ro6=self_gain6;gm8ro8=self_gain8。

2、设计步骤

①确定放大器的gm

②选择合适的沟道长度L(短沟适合高速,长沟适合高增益),本文选择L=700n m

③根据gmoverid*ft VS gmoverid图像选取合适的gm/id值,一般为10,可上下波动。(大的gm/id适合放大管,低功耗,小的gm/id值适合电流源管,高摆幅)

④已知gm/Id和gm求出Id

⑤由Id/W VS gm/Id图像找出符合④步骤的Id值,进一步计算出MOS的宽W

最后再循环④、⑤确定出所有MOS管的W。

3、仿真参数确立

在Virtuoso软件上仿真出下列图像

N2P5:

①gmoverid*ft VS gmoverid

②Id/W VS gmoverid

③gds VS gmoverid

④self_gain VS gmoverid

P2P5:

①gmoverid*ft VS gmoverid

②Id/W VS gmoverid

③gds VS gmoverid

④self_gain VS gmoverid

参数表:

| gm/Id | Id | Id/W | W | mul | Self_gain | gds | Ro(1/gds) | |

| M3 | 6 | 10.6 | 17.23 | 0.62 | 4 | |||

| M1,2 | 15 | 由gm=80u→5.3u | 2.54 | 2.09 | 4 | 0.42u | 2.38M | |

| M4,5 | 9 | 2.65u | 8.02 | 0.33 | 4 | 1.19u | 0.84M | |

| M8,9 | 7 | 2.65u | 8.65 | 0.31 | 1 | 224.88 | ||

| M10,11 | 5 | 7.95u | 17.23 | 0.46 | 1 | 1.92u | 0.52M | |

| M6,7 | 9 | 2.65u | 8.02 | 0.33 | 4 | 241.86 | ||

| 注:M4,5,gm/Id=6时 Id/W=17.23,使W过小,仿真无法满足,故选9 M8,9,gm/Id=3时 Id/W=17.23,使W过小,仿真无法满足,故选7 | ||||||||

根据公式,可以大概计算出要达到Av=3500,至少使gm6rO6即self_gain6大于95,本文选择gm/Id=6时,self_gain=166.55,但Id/W过大,取gm/Id=9

四、搭建电路

由上表所示参数搭建相应电路:

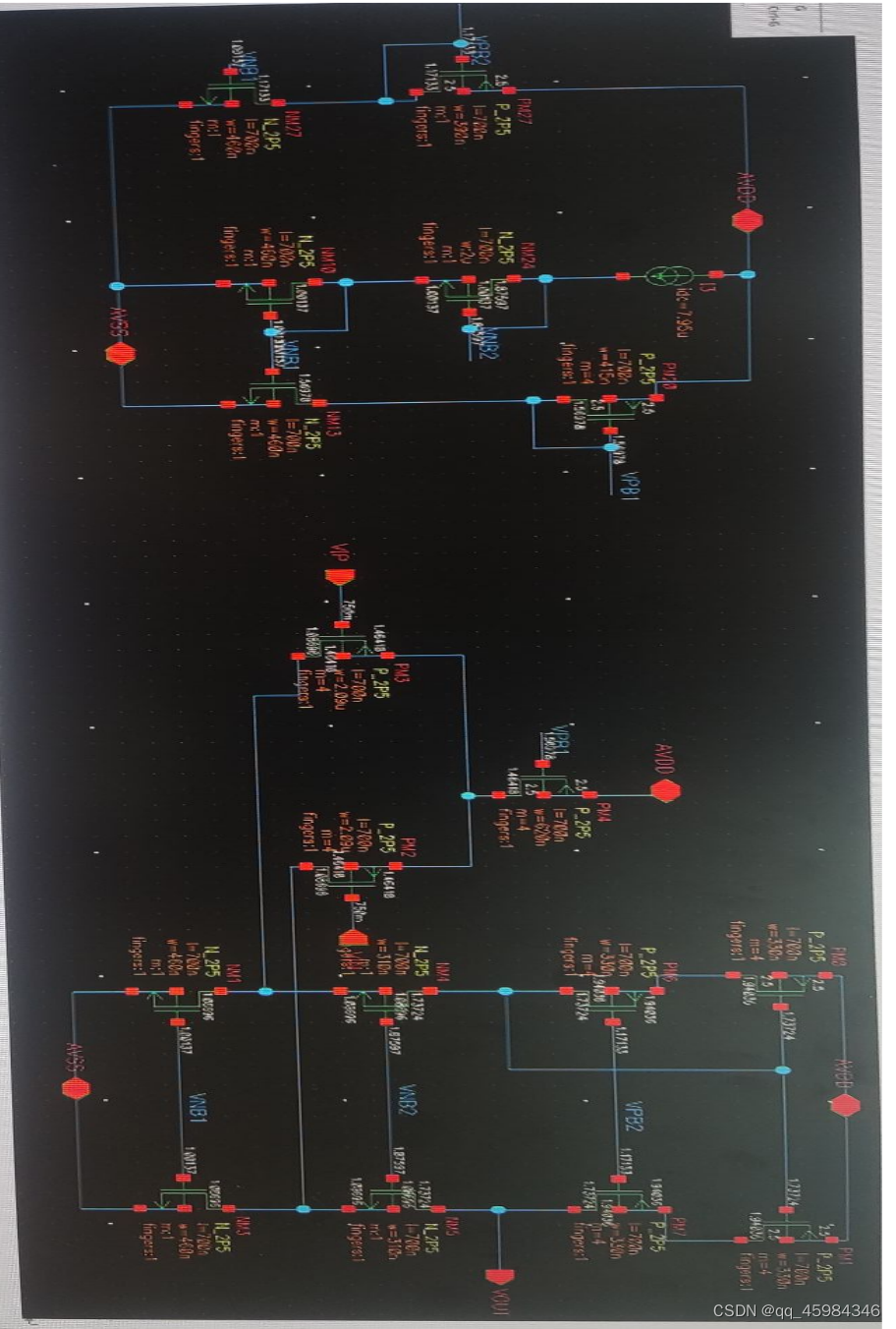

五、仿真结果

注:①本文仅为自学归纳,若有侵权,联系删除!!

②对文中提到的知识有不同见解的欢迎评论区讨论,博主纯小白,欢迎各路大神指正。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?