模拟CMOS集成电路设计中的电流镜及用Cadence Virtuoso IC617设计并仿真有关电路

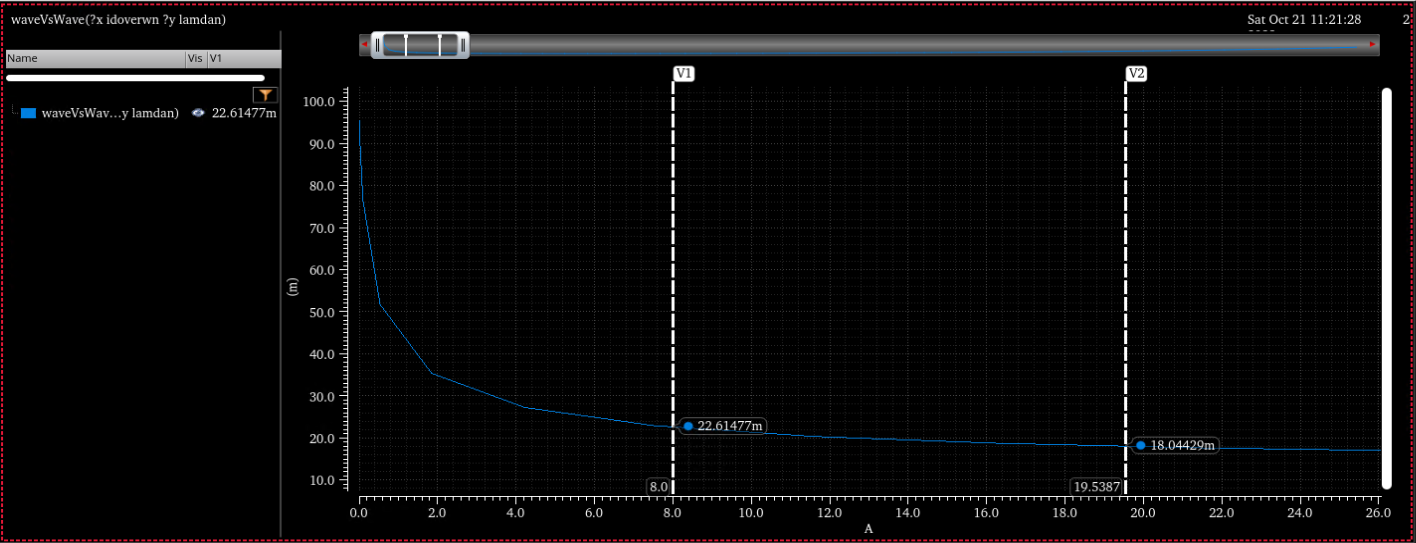

前面铺垫了那么多,其实都是在讲一些基本理论。我们在设计运放时,无非就是设计晶体管的尺寸,即W和L。那么,我们怎样把gm/id的数值映射到尺寸上?

此处引入一个新的概念,电流密度,用id/W代表。意思是,在单位尺寸W下的电流。在不同的gm/id取值下,有着不同的电流密度id/W。同时,晶体管的栅长L也对其有一定的影响。

这里的W参数是我事先计算好的,大约为40um,因为不同的W,出来的id/W是稍微有些差别的。

在实际设计时,我们通过计算得到W后,应该再重新仿真一次id/W曲线,用这个新得到的id/W数值再重新计算一遍,得到的结果才比较准确。

模拟CMOS集成电路设计中的gm/id设计方法及用Cadence Virtuoso IC617仿真有关参数曲线

同时,为了让压摆率满足50V/us的需求,gm/id就不能取太大,以此来保证电流不会太小,这里gm/id取值为12。

观察晶体管的self_gain - gmoverid曲线,找出在gm/id=12时,哪个沟道长度L下的增益大于200。最终确定L=500nm。

7119

7119

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?