案例:译码器

1.设计定义–>分析,将问题转化控制电路

译码器

二进制译码器有 n个输入端(即n位二进制码), 2"个输出线, 其功能是将输人的二进制代码译成相应的状态信息,常见的二进制译码器有2-4译码器、3-8 译码器和4-16译码器。

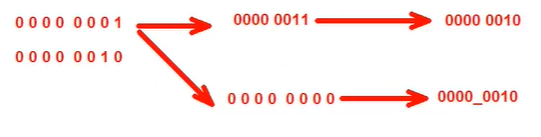

本案例以3-8译码器为例说明设计过程,3-8 译码器有3位输入,8位输出。其功能见表。

3-8译码器模块设计

2.综合

3-8译码器模块.v

module mytest(a,b,c,out);

input a,b,c;//输入端口

output[7:0] out;//输出端口

reg[7:0] out;

always @(a,b,c)

begin

case({a,b,c})//位拼接形成3位信号

3'b000: out=8'b0000_0001;

3'b001: out=8'b0000_0010;

3'b010: out=8'b0000_0100;

3'b011: out=8'b0000_1000;

3'b100: out=8'b0001_0000;

3'b101: out=8'b0010_0000;

3'b110: out=8'b0100_0000;

3'b111: out=8'b1000_0000;

default:out=8'b1111_1111;

endcase

end

endmodule

3-8译码器模块仿真 快捷键:ctrl+A

`timescale 1ms/1ms

module mytest_test;

reg a,b,c;//输入端口

wire[7:0] out; //输出端口

mytest mytest1(a,b,c,out);//调用模块

initial

begin

a=0;b=0;c=0;//0时刻

#50 a=0;b=0;c=1;

#50 a=0;b=1;c=0;

#50 a=0;b=1;c=1;

#50 a=1;b=0;c=0;

#50 a=1;b=0;c=1;

#50 a=1;b=1;c=0;

#50 a=1;b=1;c=1;

#50 $stop;

end

initial $monitor($time, , ,"a=%b,b=%b,c=%b,out=%b",a,b,c,out);

endmodule

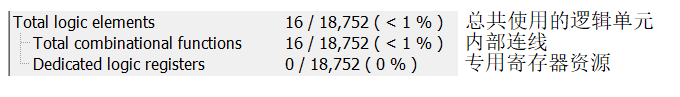

3.布局布线

4.时序仿真与功能仿真

毛刺

5.编程下载和在线测试

2708

2708

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?