//

// Company:

// Engineer:

//

// Create Date: 2020/02/24 11:08:14

// Design Name:

// Module Name: serial1

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

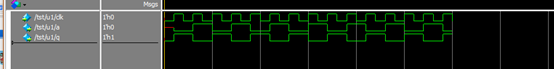

module serial1(

input clk,

output reg a,q

);

initial q<=0;

always @(posedge clk)

begin

q=~q;

a=~q;

end

endmodule

`timescale 1ns / 1ns

//

// Company:

// Engineer:

//

// Create Date: 2020/02/24 11:09:13

// Design Name:

// Module Name: tst

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tst(

);

reg clk;

wire a,q;

serial1 u1(.a(a),.q(q),.clk(clk));

initial begin

clk<=1'b0;

end

always #10 clk<=~clk;

endmodule

//

// Company:

// Engineer:

//

// Create Date: 2020/02/24 11:39:46

// Design Name:

// Module Name: serial2

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

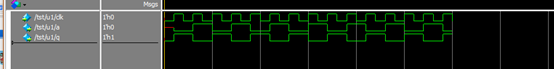

module serial2(

input clk,

output reg a,q

);

initial q<=0;

always @(posedge clk)

begin

a=~q;

q=~q;

end

endmodule

`timescale 1ns / 1ns

//

// Company:

// Engineer:

//

// Create Date: 2020/02/24 11:41:10

// Design Name:

// Module Name: tst

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tst();

wire a,q;

reg clk;

serial2 u1(.a(a),.q(q),.clk(clk));

initial begin

clk<=1'b0;

end

always # 10 clk<=~clk;

endmodule

3405

3405

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?