vhdl入门2——ise制作一位全加器

先写一下vhdl的,先做一个两输入或门,再做一个半加器,在连接形成一个1位全加器

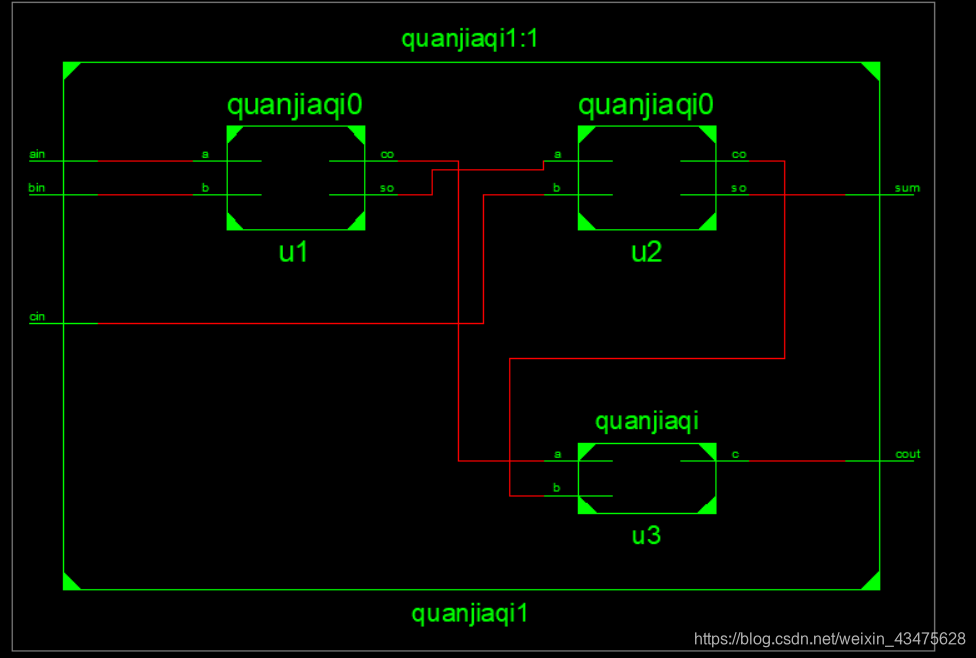

下边的命名有误:quanjiaqi1——一位全加器,quanjiaqi0——半加器,quanjiaqi——或门。

--ujs-lili

--这个做的是半加器

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity quanjiaqi0 is --定义实体

port ( a,b : in std_logic; --定义端口

co,so: out std_logic);

end quanjiaqi0;

architecture Behavioral of quanjiaqi0 is

begin

so <= (a or b) and (a nand b);

co <= not(a nand b);

end Behavioral;```

--这个做的是或门

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity quanjiaqi is

port(a,b :in std_logic;

c : out std_logic);

end quanjiaqi;

architecture Behavioral of quanjiaqi is

begin

c <= a or b ;

end Behavioral;

--做一位全加器

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity quanjiaqi1 is

port( ain,bin,cin : in std_logic;

cout,sum : out std_logic);

end quanjiaqi1;

architecture Behavioral of quanjiaqi1 is

component quanjiaqi --这里就是使用之前做好的原器件了

port(a,b :in std_logic; --这个是之前元器件的端口申明

c: out std_logic);

end component;

component quanjiaqi0

port ( a,b : in std_logic;--同上

co,so: out std_logic);

end component;

signal d,e,f : std_logic; --这个是中间信号,就是每个元器件的端口刚出来接到的地方,用的是位矢量

begin

u1: quanjiaqi0 port map( a => ain,b=>bin,co=>d,so=>e); --这个就是硬件的连接了

u2: quanjiaqi0 port map( a => e,b=>cin,co=>f,so=>sum);

u3: quanjiaqi port map(a =>d,b=>f,c=>cout);

end Behavioral;

--仿真程序:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY quanjiaqi1_tb IS

END quanjiaqi1_tb;

ARCHITECTURE behavior OF quanjiaqi1_tb IS

COMPONENT quanjiaqi1

PORT(

ain : IN std_logic;

bin : IN std_logic;

cin : IN std_logic;

cout : OUT std_logic;

sum : OUT std_logic

);

END COMPONENT;

signal ain : std_logic := '0';

signal bin : std_logic := '0';

signal cin : std_logic := '0';

--Outputs

signal cout : std_logic;

signal sum : std_logic;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: quanjiaqi1 PORT MAP (

ain => ain,

bin => bin,

cin => cin,

cout => cout,

sum => sum

);

process

begin --起初忘记写begin

ain <= '0';bin <= '0';cin<='0'; --这地方是“;”

wait for 100ns;

ain <= '0';bin <= '0';cin<='1';

wait for 100ns;

ain <= '0';bin <= '1';cin<='0';

wait for 100ns;

ain <= '0';bin <= '1';cin<='1';

wait for 100ns;

ain <= '1';bin <= '0';cin<='0';

wait for 100ns;

end process;

END;

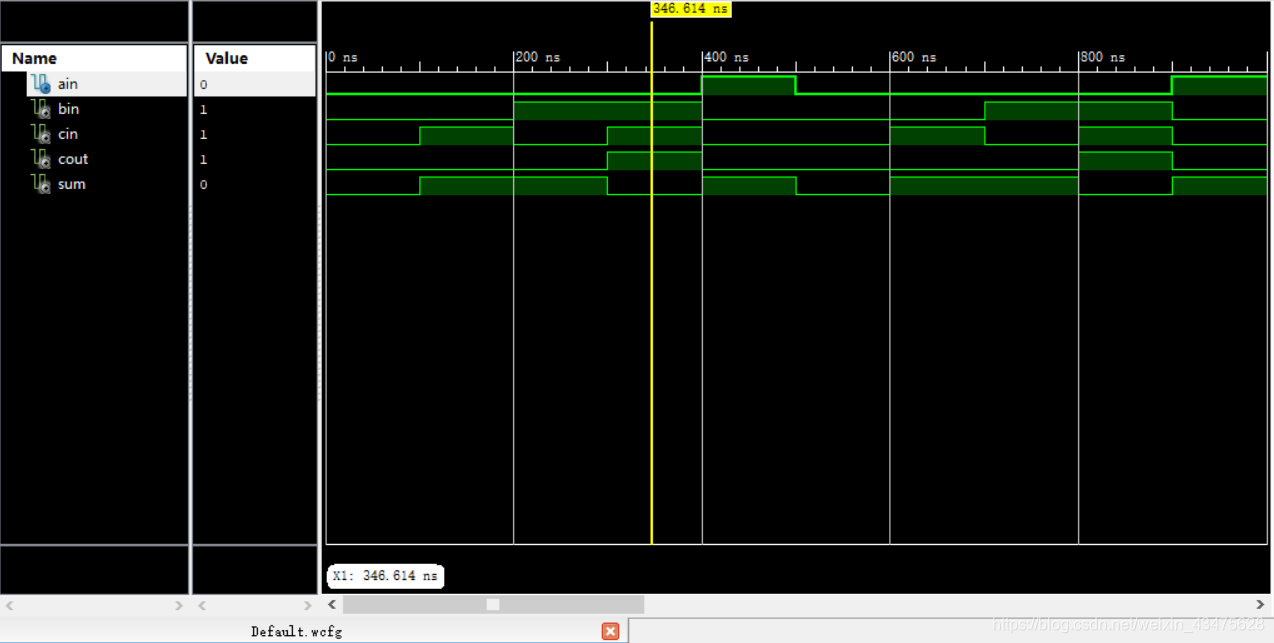

下面看一下仿真图:

感兴趣可以和真值表对比一下:是正确的。

再看一下原理图:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?