一.DDR介绍

- DDR是双倍速率同步动态随机存储器,即内存(之一)。

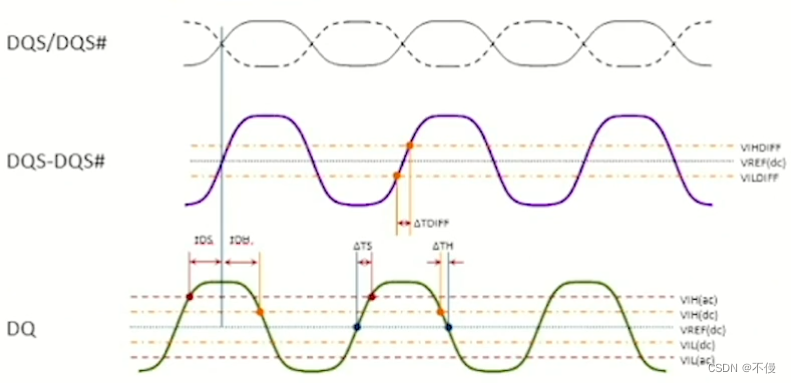

- DDR内存是一个时钟周期内传输两次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。注:数据线是双沿采样,地址、控制线是单沿采样。

- SDRAM在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输。DDR内存可以在与SDRAM相同的总线频率下达到更高的数据传输率。

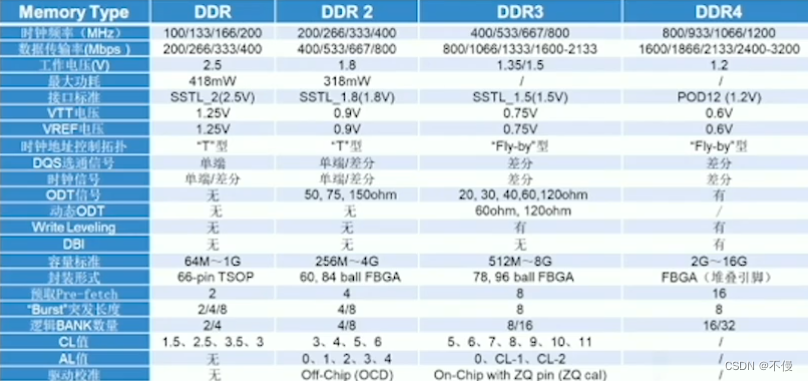

- DDR参数规范:

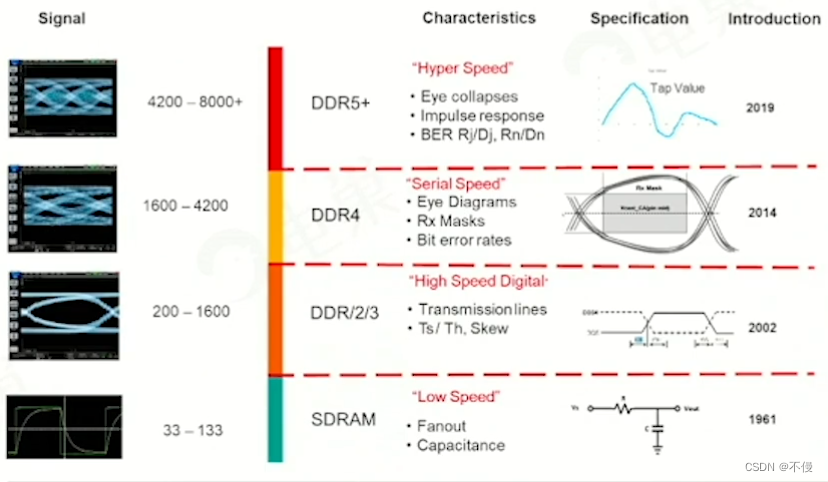

不同阶段内存关注重点:

- SDRAM:连线,等长。

- DDR2、DDR3:反射,串扰,建立时间、保持时间,时序误差。

- DDR4:眼图,误码率。

- DDR5:数据线预加重。

二.DDR信号描述

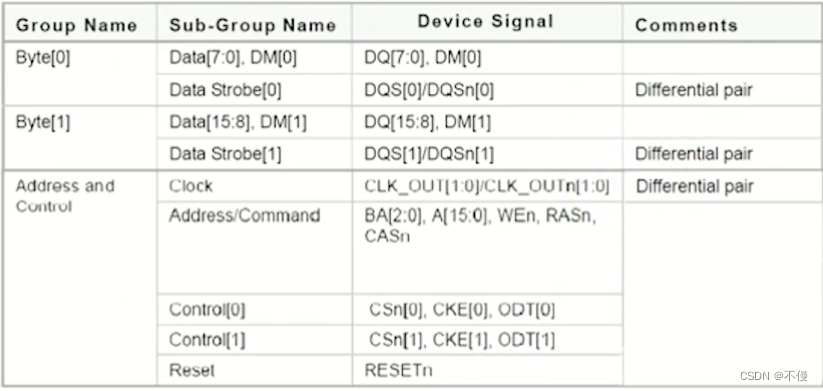

DDR信号描述:

电源、地、配置:

控制:

时钟、地址、数据:

三.DDR设计例程简介

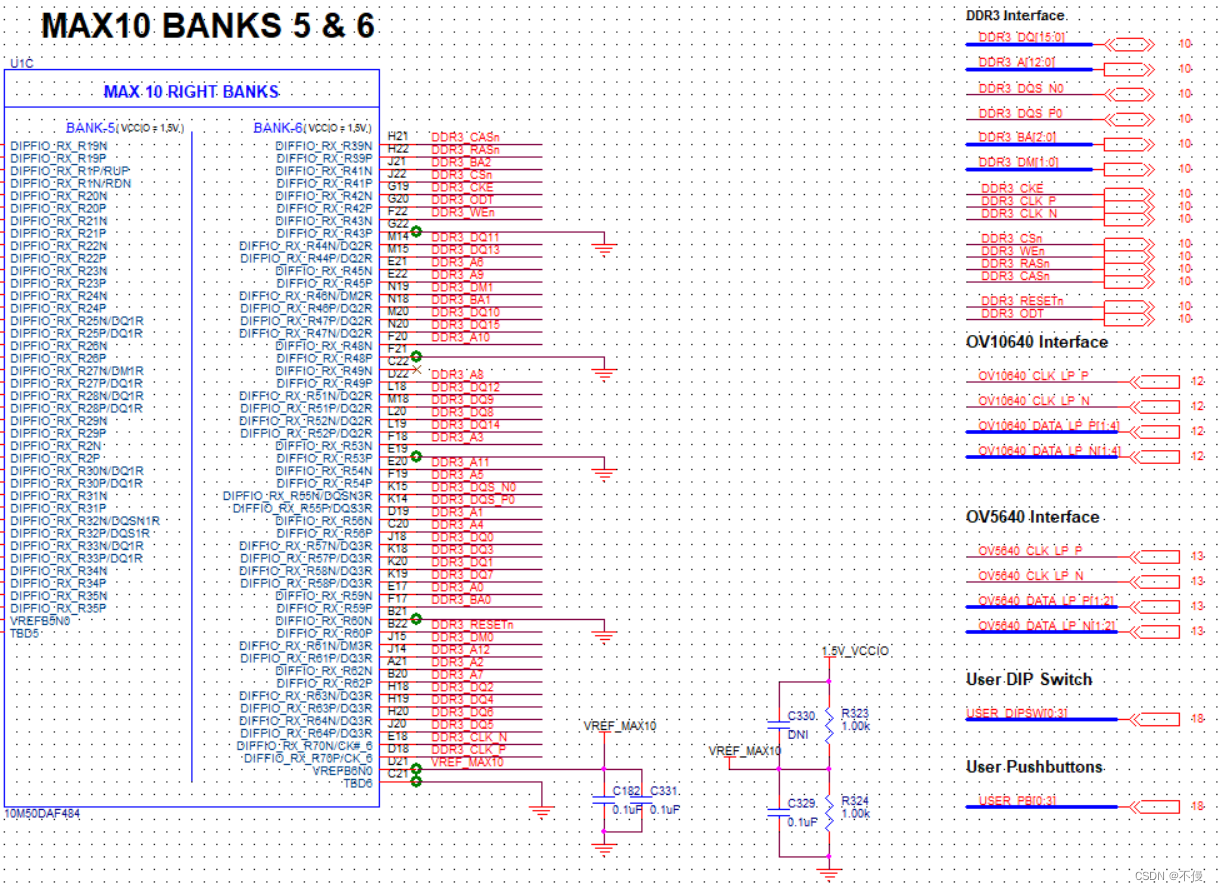

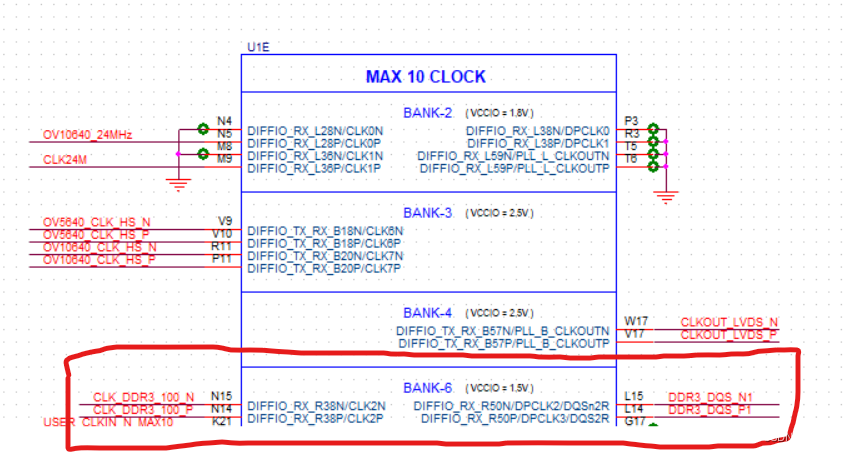

主控端:

上图例FPGA端有关DDR设计要点:

- DQ信号只能接DQ管脚,数据信号。DQ之间可以交换。

- DM信号只能接DM管脚,掩码信号。

- 时钟信号只能接时钟信号。

- 控制信号可以随意接在DDR的BANK内。

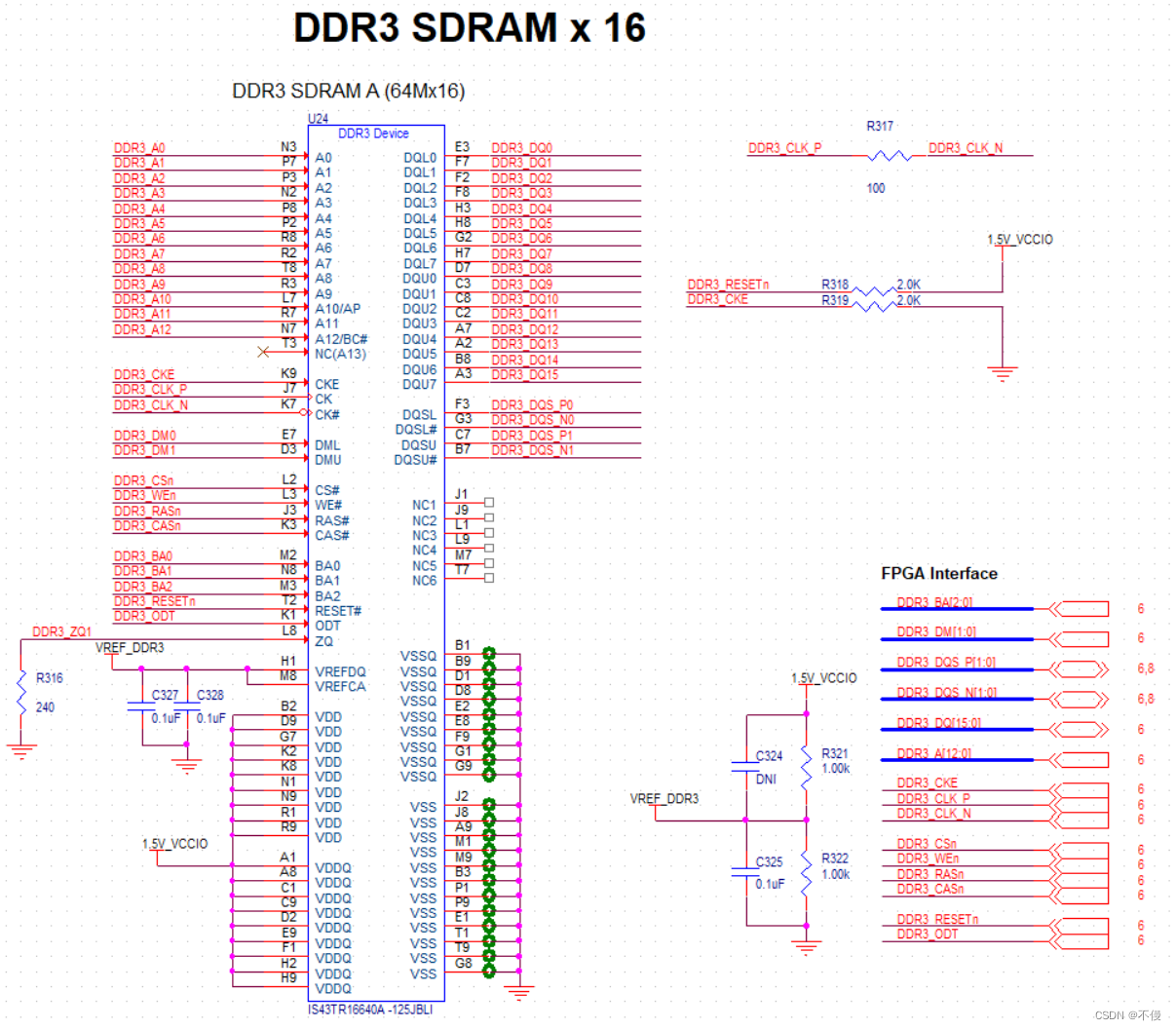

DDR端:

上图例DDR参数特点:

- 数据位宽x16

- 芯片容量64Mx16=1Gbit;(1/8GB)

- 最高传输速率1866Mbps(实际速率取决于FPGA端)

- 工作电压1.5V

- 无VTT(多片DDR时需要)

上图例DDR设计要点:

- 两组数据线可分别等长(高8位和低8位),组间可使用FPGA逻辑进行时序调整。

- R317时钟终端匹配电阻,要靠近DDR管脚。

- ZQ为内部ODT校准,R316精度要搞。

- VREF精度要高,要稳定,电阻要用高精度。

- RESETn、CKE上下拉稳定电平,防止误操作。

待补充

参考引用:

1.相关内容及图片为《电巢》课程的学习记录,侵删。

2.管脚说明列表参考链接,侵删。

1702

1702

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?