文章目录

一、约束规则的来历

1.高速PCB有哪些规则?

- 板材

- 叠层

- 线宽

- 间距

- 线长

- 等长(等时)

- 回流(不能跨分割)

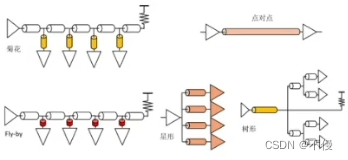

- 拓扑

- 过孔

- 载流

- PDN(电源分配网络)

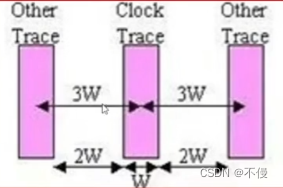

2. 3W规则

- 在PCB上,当走线的中心间距不小于3倍线宽时,则可保持大部分电磁场不互相干扰,这就是3W规则。对于边缘间距就是2W。

- 3W规则虽然简单易记,但要强调一点,这个规则成立是有前提条件的。距参考层近才有用,即满足50欧姆阻抗的情况下。

- 3W规则很实用,但也不是所有线都要强制符合3W规则。(时钟、复位、高速信号要满足。)

- 满足3W规则能使信号间的串扰减少70%,而满足10W则能使信号间的串扰减少近98%。

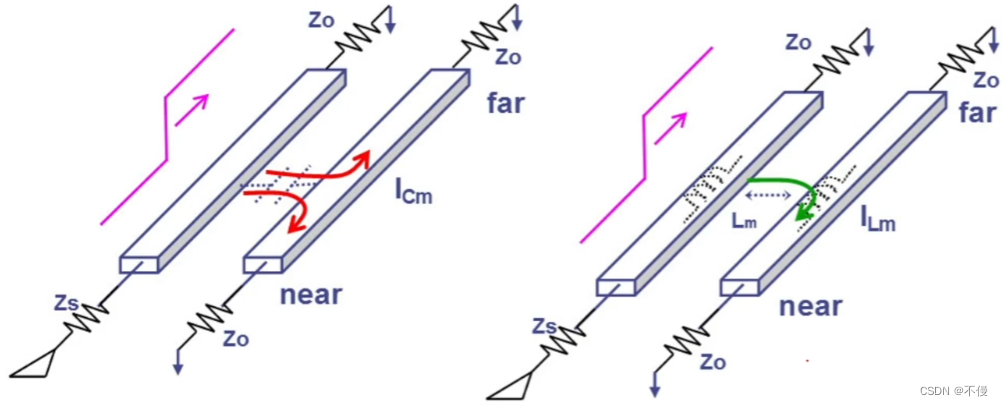

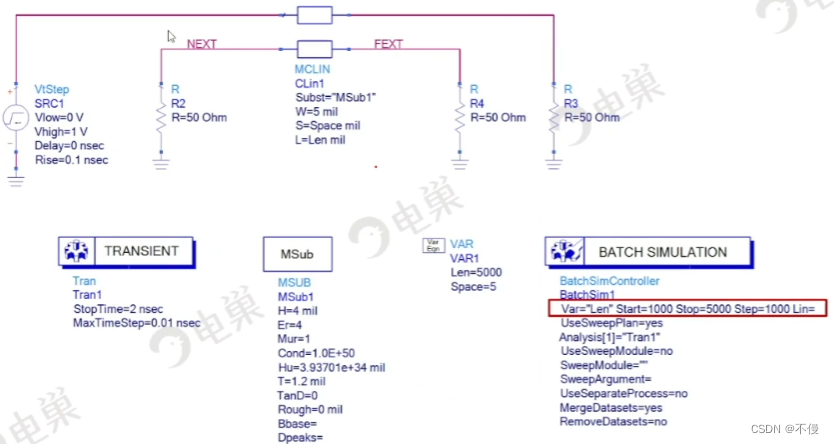

3. 串扰的产生

- 互容是通过电场耦合,互感是通过磁场耦合。

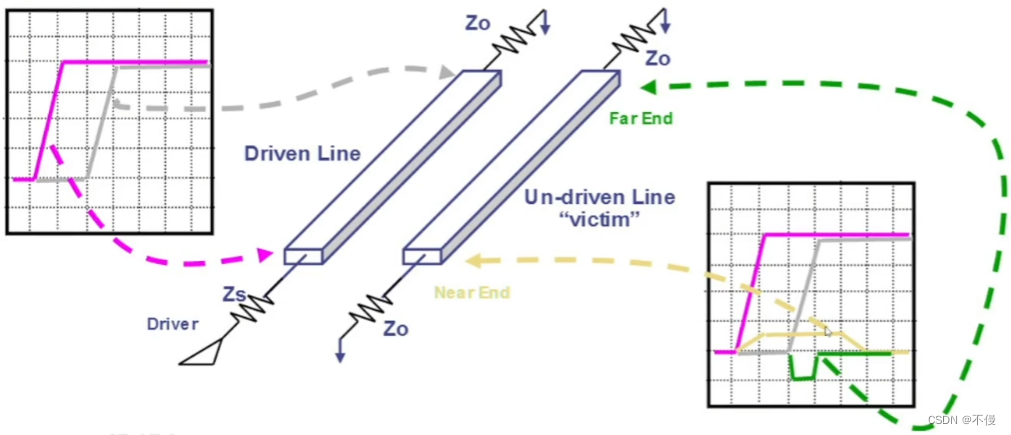

- 流向近端的是后向串扰,流向远端的是前向串扰。

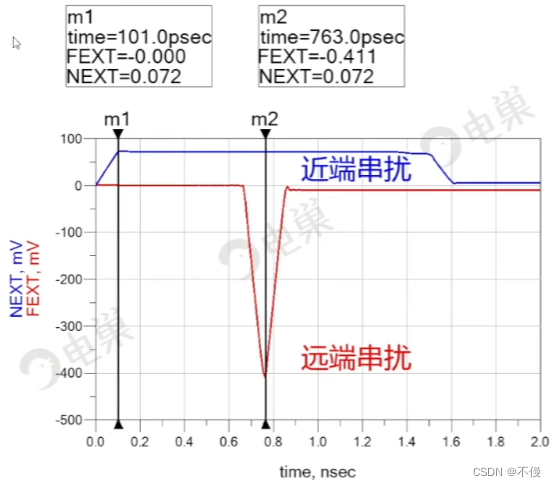

近端串扰与远端串扰:

- 如果在攻击线末端和受害线的两端都匹配端接,近端形成的是两种串扰的同向叠加,幅度是正值,以微带线为例,通常来说互感引起的耦合电流要更大,所以在远端叠加形成的串扰为负。

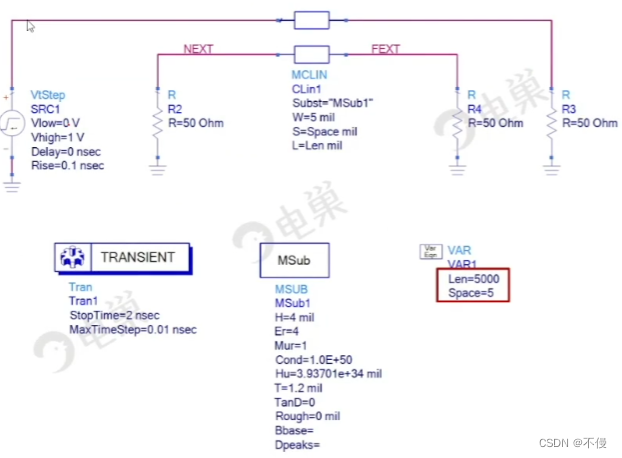

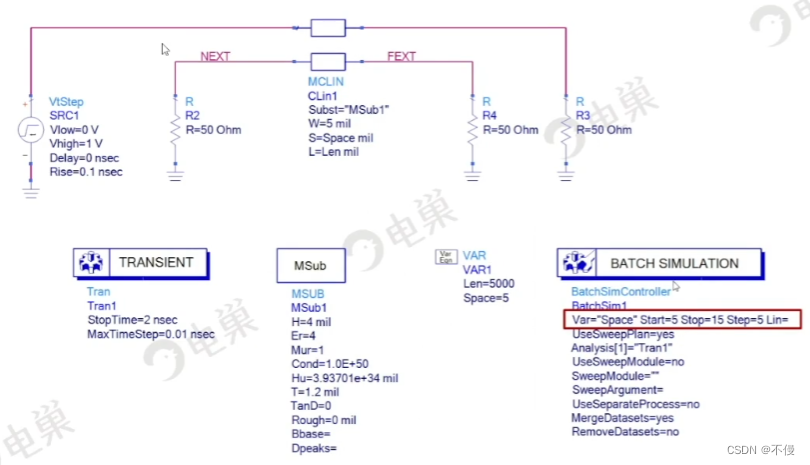

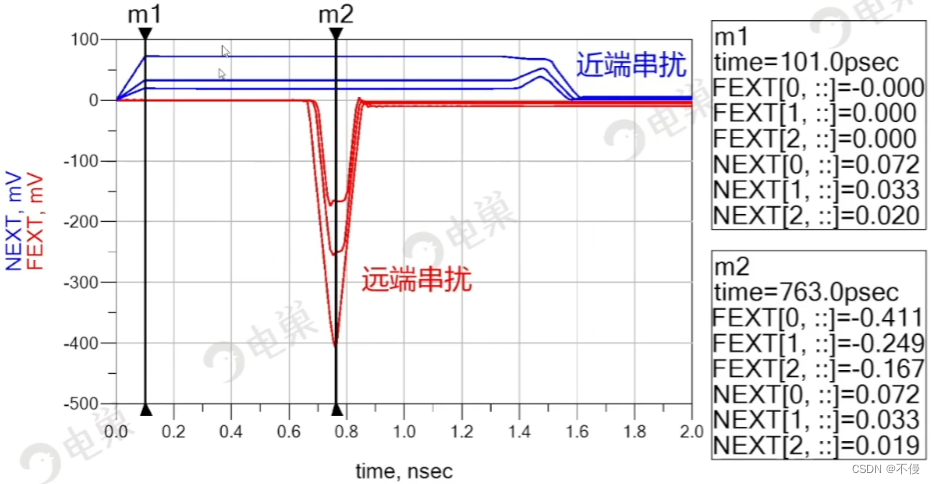

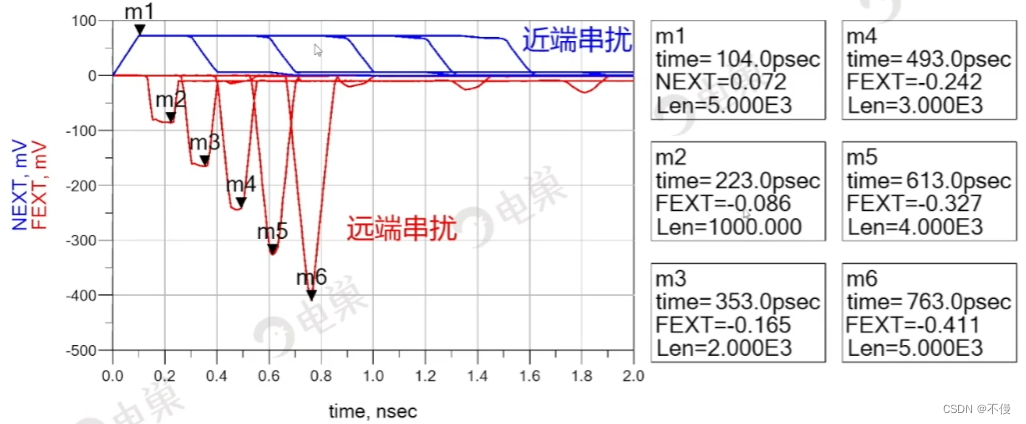

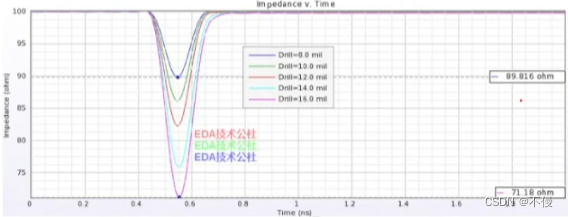

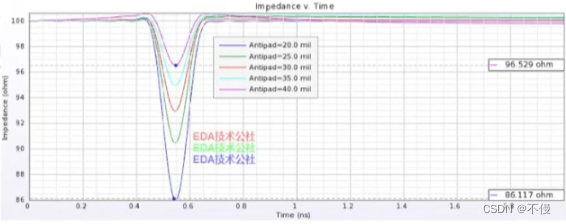

4. 串扰理论评估

改变间距扫描:

改变线长扫描:

5. 降低串扰的措施

- 增加信号路径之间的间距;

- 使耦合长度尽量短;

- 在带状线层布线;(平衡带状线,在两参考层正中间时最好,互感相互抵消,远端串扰很小)

- 用平面作为返回路径;

- 减小信号路径的特性阻抗;(阻抗越高,互感越大,互容越小)

- 使用介电常数较低的叠层;

- 在封装和接插件中不要共用返回引脚;

- 使用两端和整条线上有短路过孔的防护布线;(包地,且包地线上要小于1/4波长打地孔)

- 降低信号上升/下降沿时间。

6. 串扰要点

- 串扰只能降低,不可消除

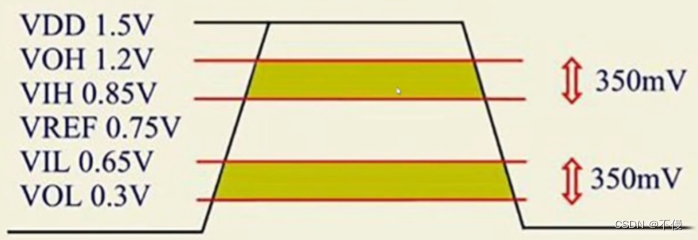

- 多大的串扰可以接受?

①每条受影响走线上的总串扰来自附近多个串扰源的串扰,所有这些串扰累加起来达到了最大值。然后进行仿真。

②串扰只是信号噪声的一部分,实际仿真、测试中很难单独观测到。(包含串扰、反射、地弹等。)

③不同电平噪声容限是不一样的。

7.高速PCB设计规则的目的

- 满足反射、串扰、时序等信号完整性要求

- 满足压降、载流等电源完整性要求

- 满足DFF、DFA、DFT等生产加工要求

- … …

7.1降低反射

- 将阻抗计算得出的线宽设置到软件中,并限制阻抗失配的走线长度。

- 对于差分线还包括对内间距,失配长度等。

- 所用过孔不仅要符合加工要求,超高速信号所用过孔规格还要通过仿真确定。

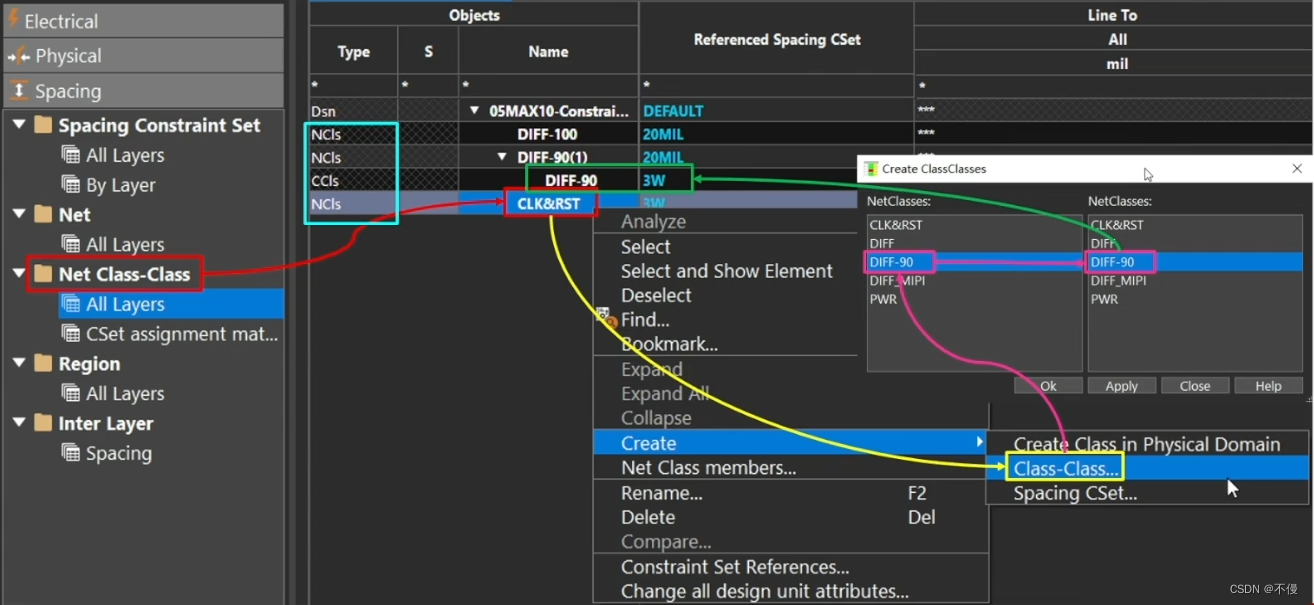

7.2降低串扰

- 通过软件控制走线、过孔、铜箔等对象之间的间距,避免人工通过肉眼测量。

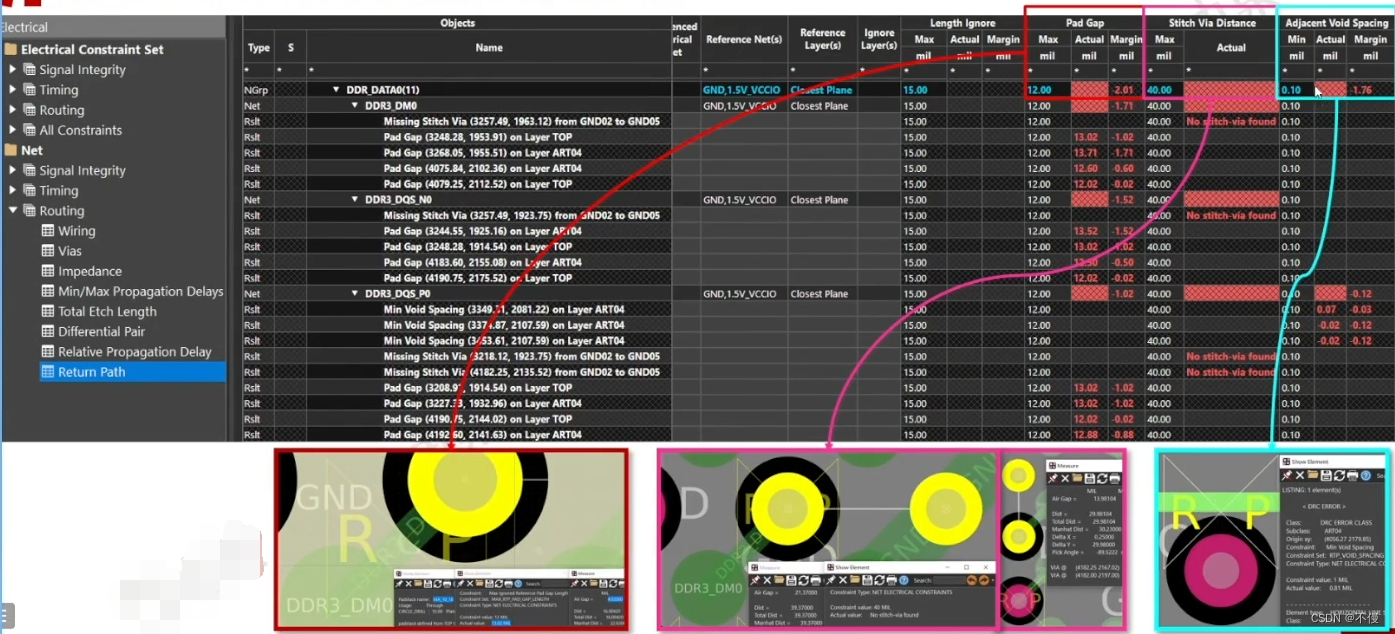

7.3控制返回路径

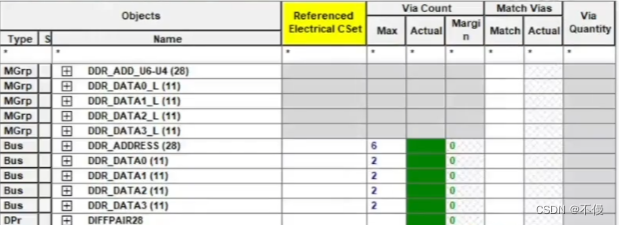

- 针对有过孔数量要求的高速信号可设置相应规则进行约束,以防信号换层过多,导致信号回路问题。

7.4满足时序

-

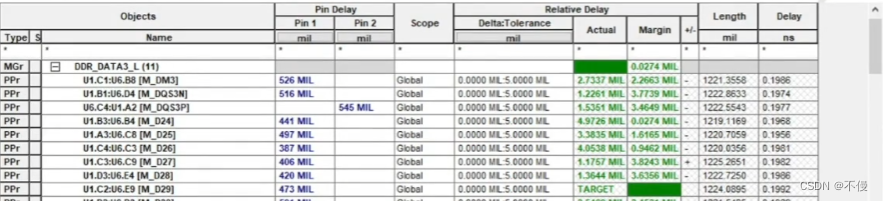

有时序等长要求的信号总线设置等长约束。

-

共同同步时钟:最大最小长度要求;源同步时钟:相对延时等长。

-

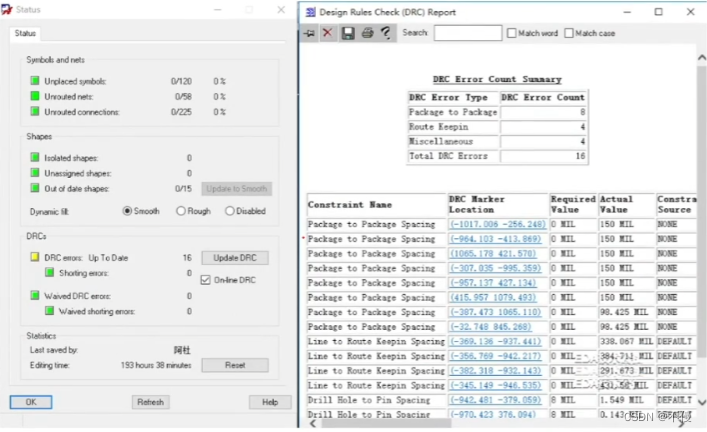

接住软件快速对设计状态进行查看,包括连通性、多余线段、过孔、DRC。

-

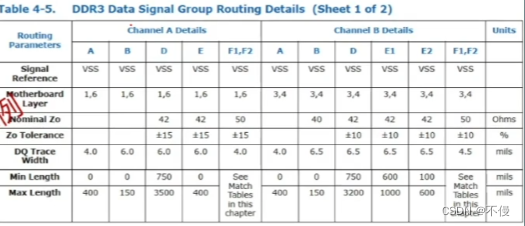

高速芯片专用规则举例:

二、约束规则的设置

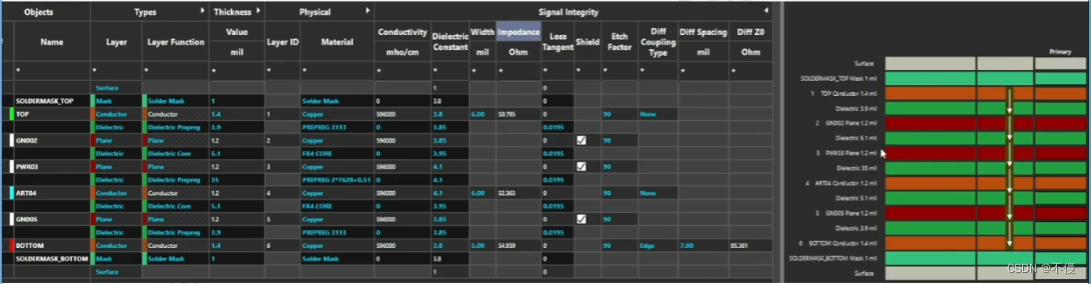

1.叠层规则设置

- 根据《PCB加工工艺要求说明书》上的层叠信息,在PCB上进行对应的叠层设置。

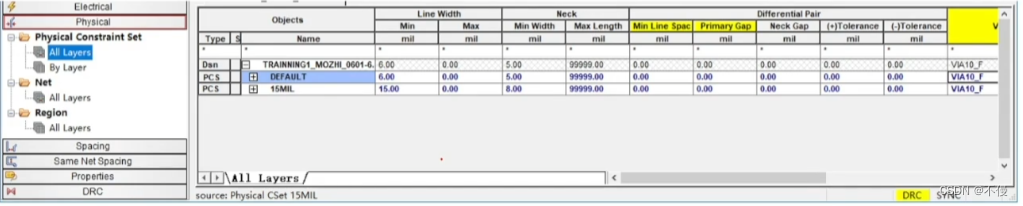

2.线宽规则设置

- 所有阻抗线线宽满足《PCB加工工艺要求说明书》中的阻抗信息。

- 电源/地线:线宽>=15Mil,Neck线宽不大于Pin宽。

- 整板过孔种类≤2,且过孔孔环>4Mil,Via参数与《PCB Layout工艺参数》一致,板厚孔径比满足板厂工艺能力。

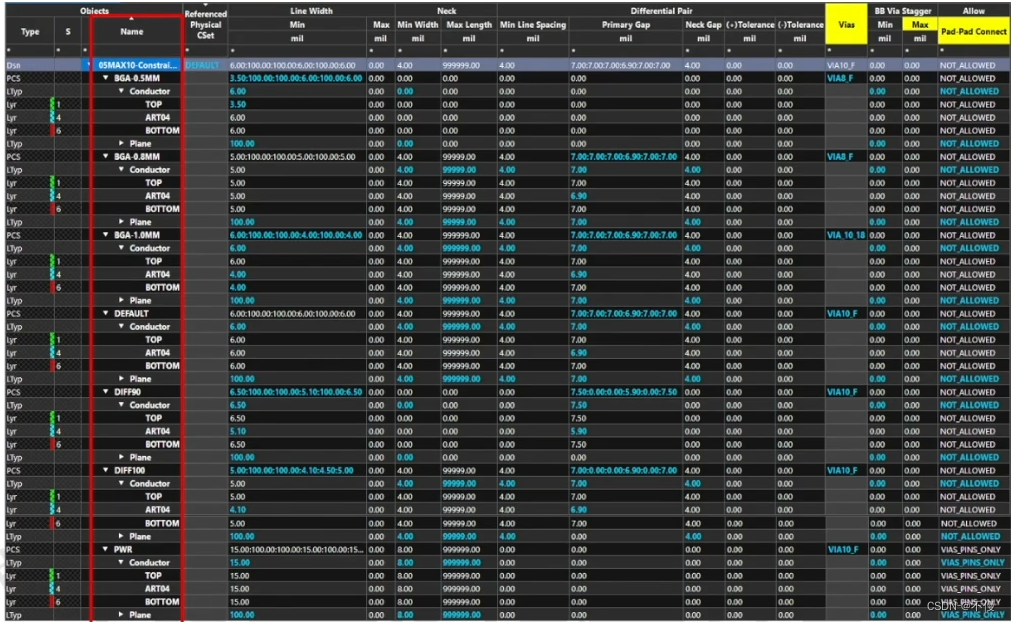

线宽规则模板设置示例

- 平面层线宽设置过大,可防止线走至平面层。

- BGA下线宽设置:单根线,Air Gap:9.85mil,线宽9.35/3=3.11mil约等于3.5mil。

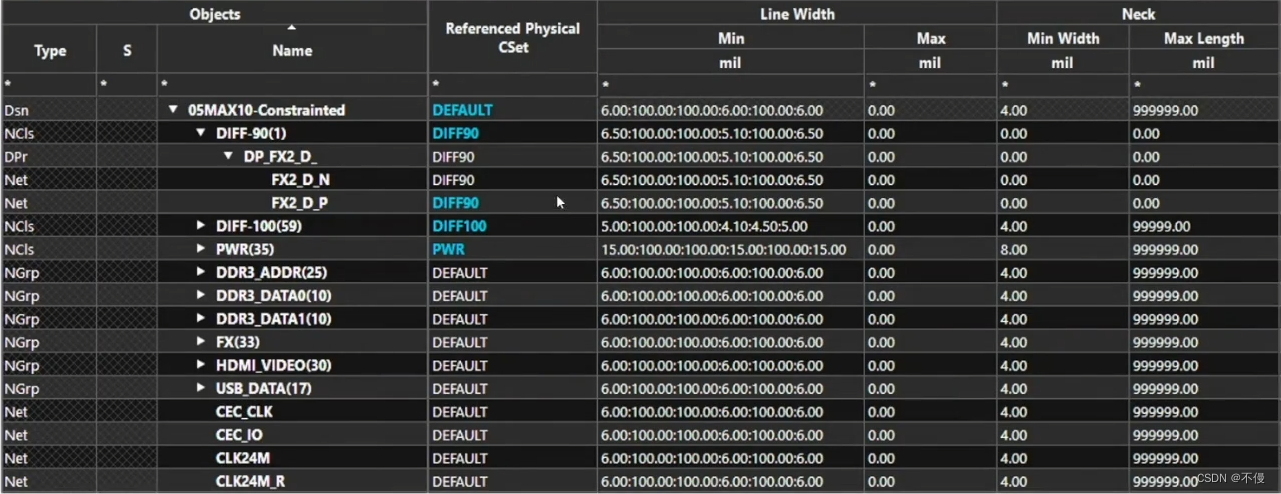

线宽规则模板分配示例

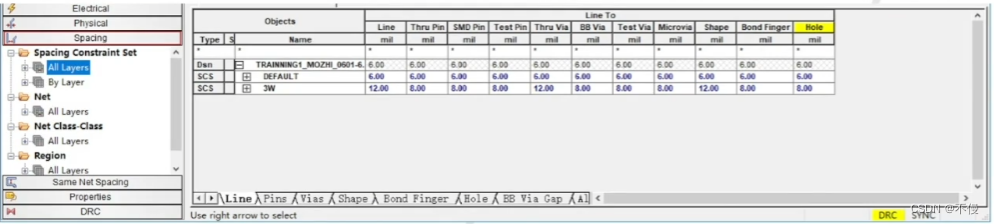

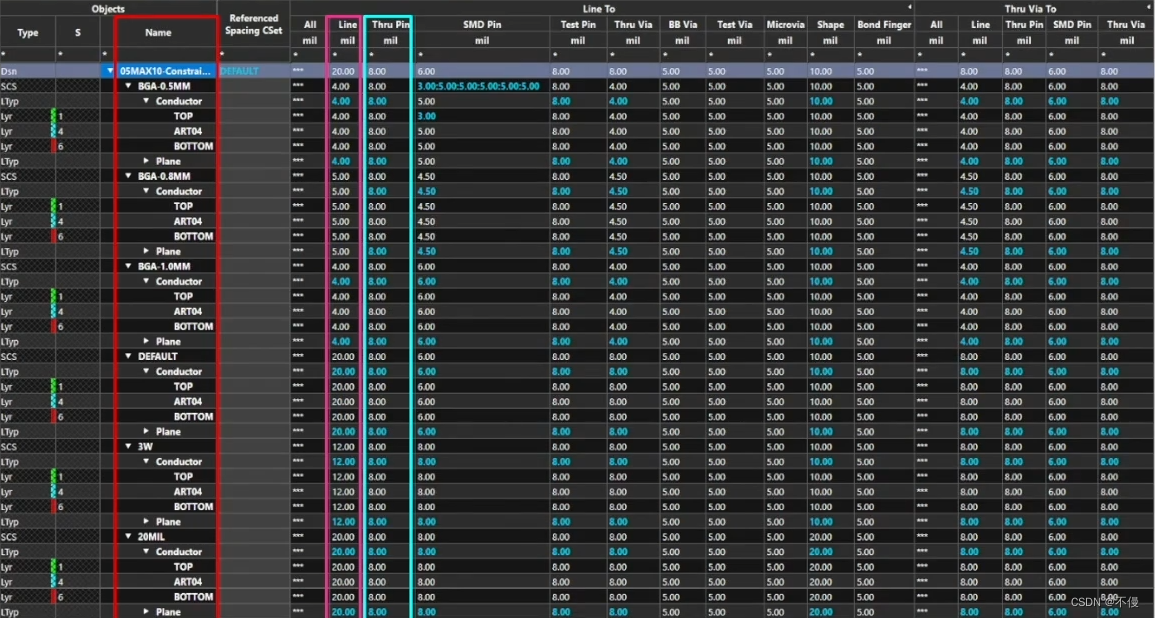

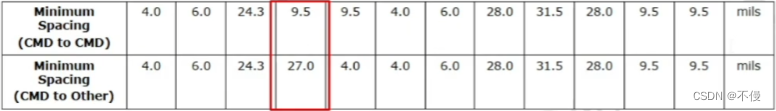

3.间距规则设置

- 根据《PCB Layout工艺参数》中的间距要求设置间距规则,时钟、复位等重要信号线间距至少3W以上,差分线与其他信号线的距离≥20Mil。

- 此外,还应保证内外层导体到安装孔、定位孔、邮票孔、V-CUT、导轨、板边缘距离与《PCBLayout工艺参数》一致,以免开短路。

间距计算

- 以1.0mm Pitch BGA为例:

- Line to SMD Pin(表层): (SMD Pin Air Gap-Width)/2=(20.47-6)/2~7.0mil

- Line to Through Via(内层): (Pin Pitch-Via Pad Size-2Width)/3=(39.37-18-24)/3~4.0mil

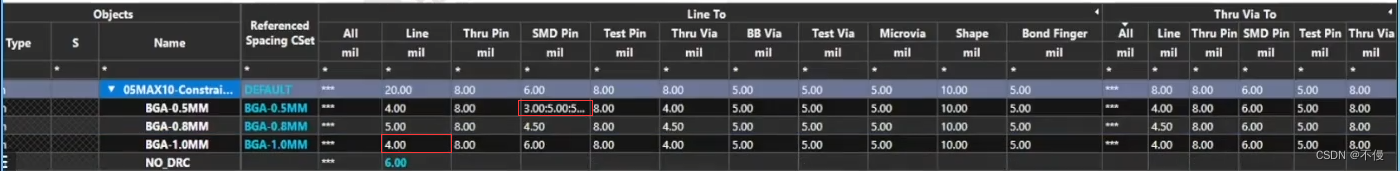

间距规则模板设置

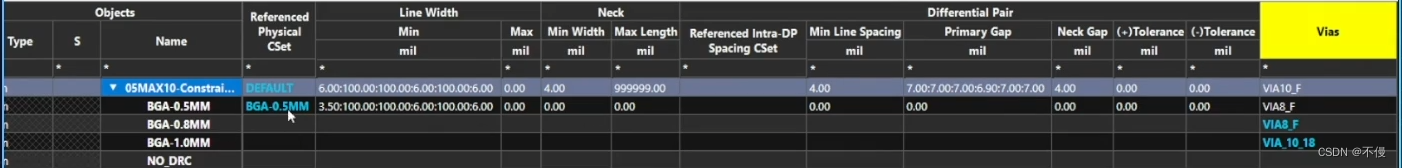

4.约束区域规则设置

- 过孔设置见《PCB Layout工艺参数》中的通孔设计方案。

- 1.0mm、0.8mm Pitch BGA中的信号线、孔和铜皮两两相互间的最小间距为4Mil。

- 0.65mm、0.5&0.4mm Pitch BGA中的信号线、孔和铜皮两两相互间的最小间距为3Mil。

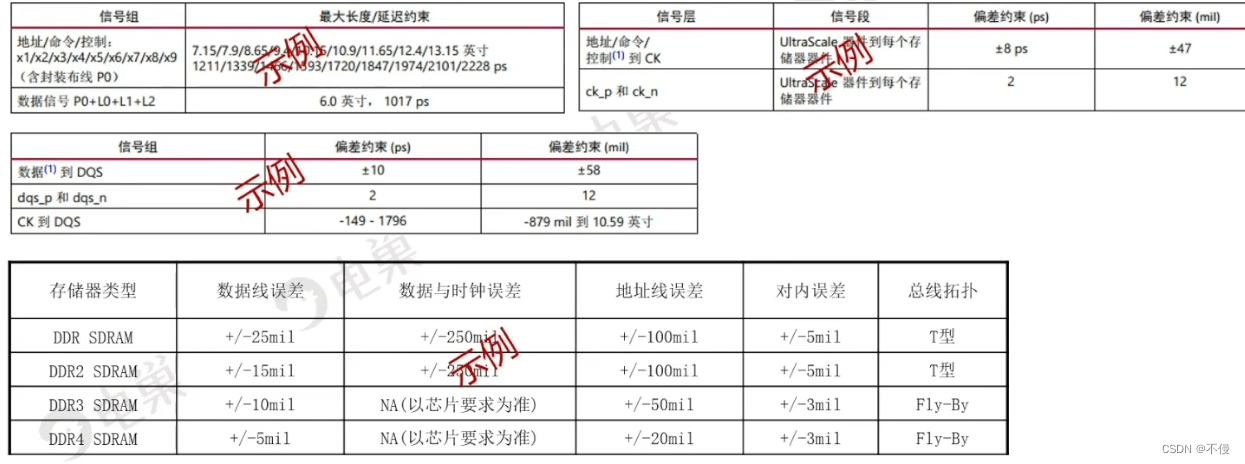

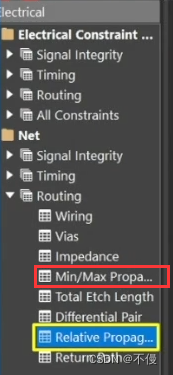

5.时序规则设置

- 根据《PCB Layout资料及要求》中的电气要求,参考对应电路、总线接口等设计指南或仿真结果,在PCB中设置时序规则。

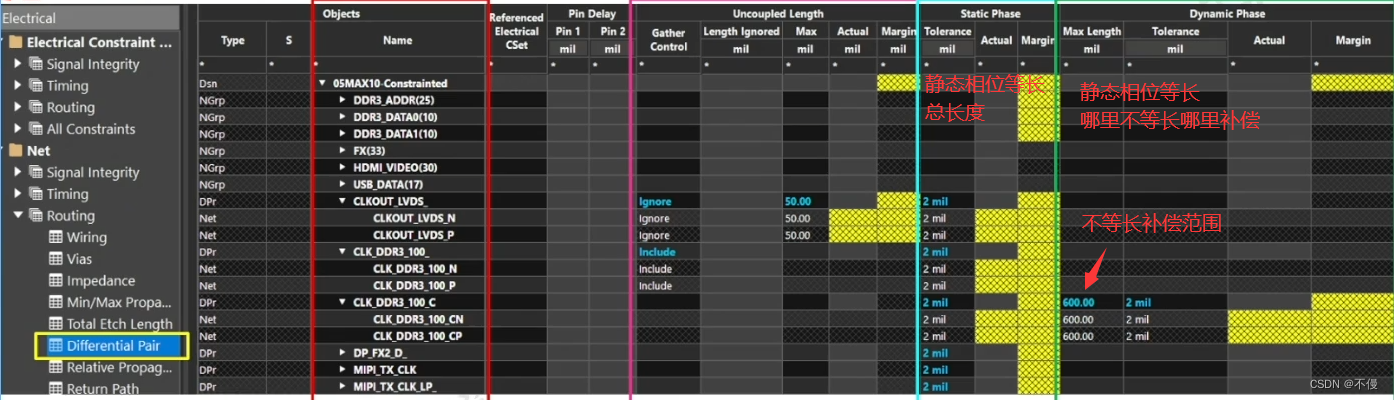

差分线时序规则设置示例

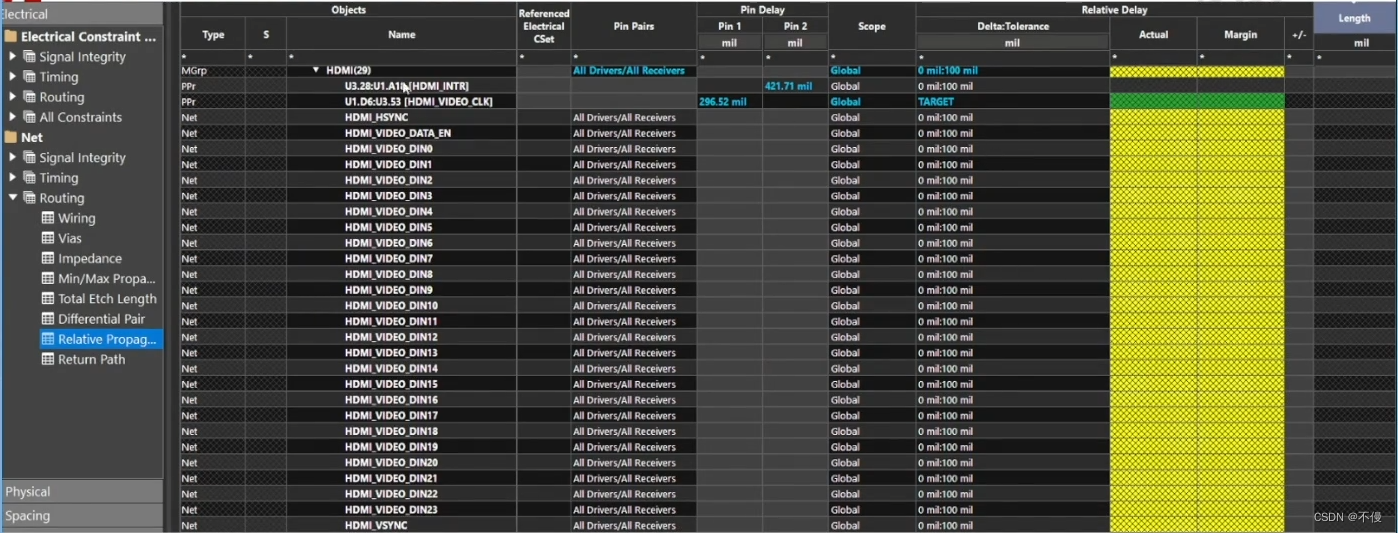

并行总线规则设置示例 - 源同步,相对延时等长。

- 一般来说并行总线基准线设置成对应参考时钟。

- 误差规范来源方法:芯片原厂、公司经验规范、仿真得到。

- 共同同步总线,最大最小延时等长。

6.生产相关规则设置

三、规则设置技巧

1.组间与组内差异化规则约束应用

2.信号回流路径规则设置示例

3.快速设置复杂拓扑总线相对延时等长

链接: 阻抗等长约束

4.Technology文件复用

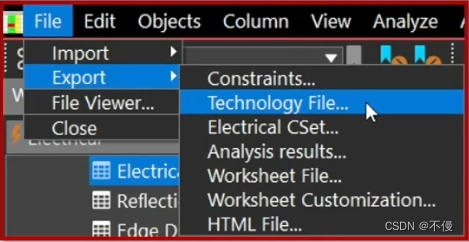

导出:

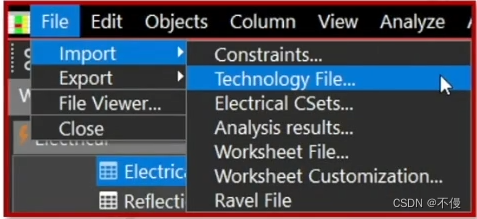

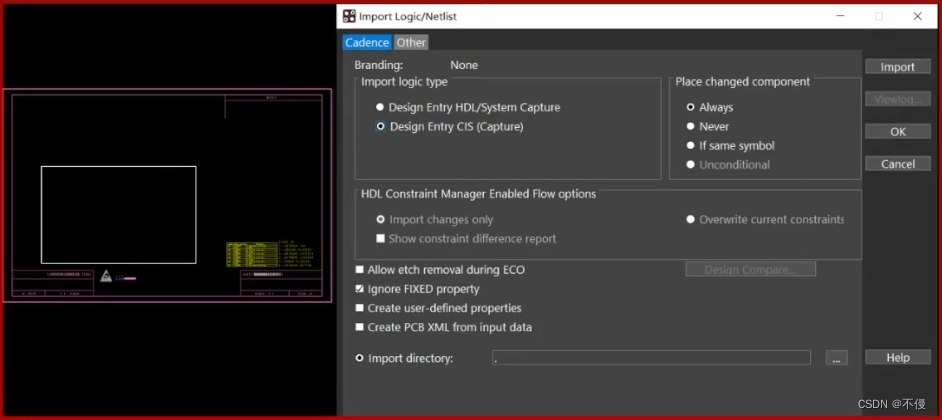

导入:

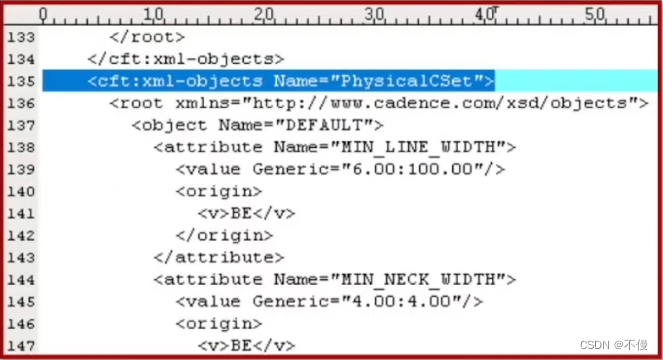

文件内容样式:

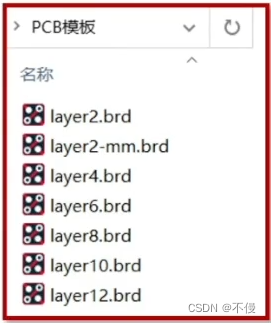

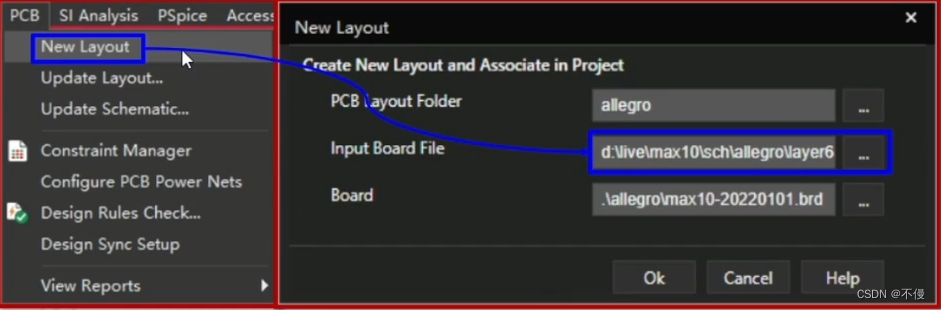

另一方法:

- PCB模板复用

四、总结

约束规则的来历:

- 电气上: SI、PI、EMC、Thermal…

- 生产上:DFF、DFA、DFT…

规则设置:

- 规则驱动设计:线宽、间距、耦合长度、时序等长、回流路径…

- 约束规则复用:约束模板、PCB模板…

具体的规则设计可参照文件《Allegro16.6约束规则设置详解(图文并茂).pdf》,需要可评论私信索取。

参考资料来自电巢,侵删。

2889

2889

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?