1 简介

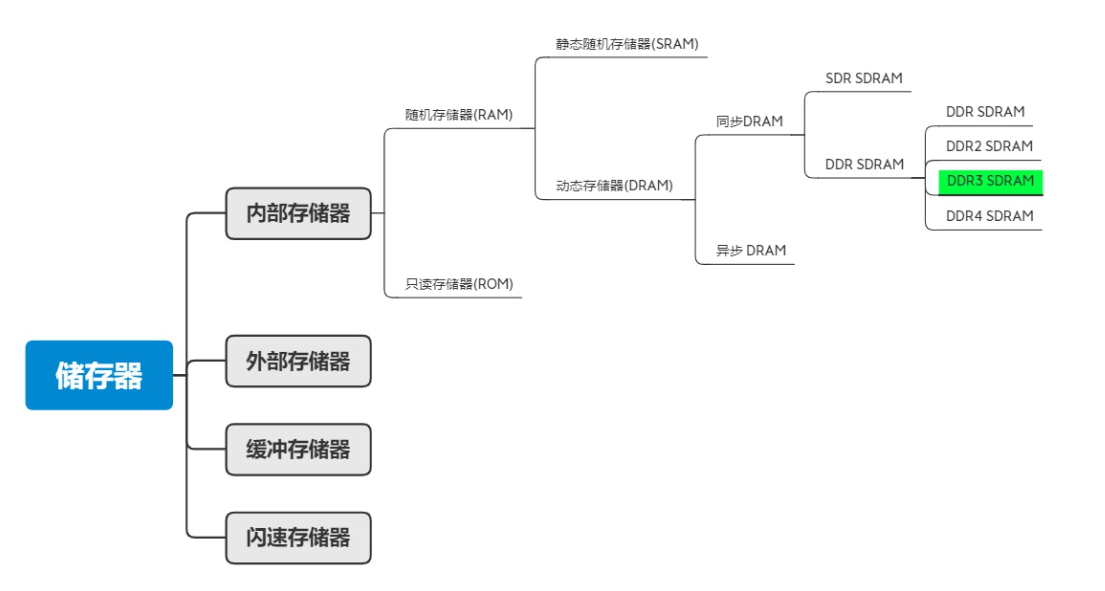

存储器大体可以分为RAM和ROM,其主要的区别如下:

- RAM存储器:掉电数据丢失;

- ROM存储器:掉电数据不丢失;

电路设计中常见的DDR属于SDRAM,中文名称是同步动态随机存储器。其中同步和动态的意义分别如下:

- 动态存储器(Dynamic RAM,DRAM):存储器需每个一段时间,要刷新冲一次电,否则会丢失内部的数据。

- 静态存储器(Static RAM,SRAM):不需要刷新电路,内部数据不会丢失。

- 同步(Synchronous):工作需要同步时钟,它是内部数据和指令的发送于接收的基准。

- 随机存储器:数据不是线性存储,而是通过指定地址来进行数据的读写。

2 DDR的发展

DDR的发展历程:

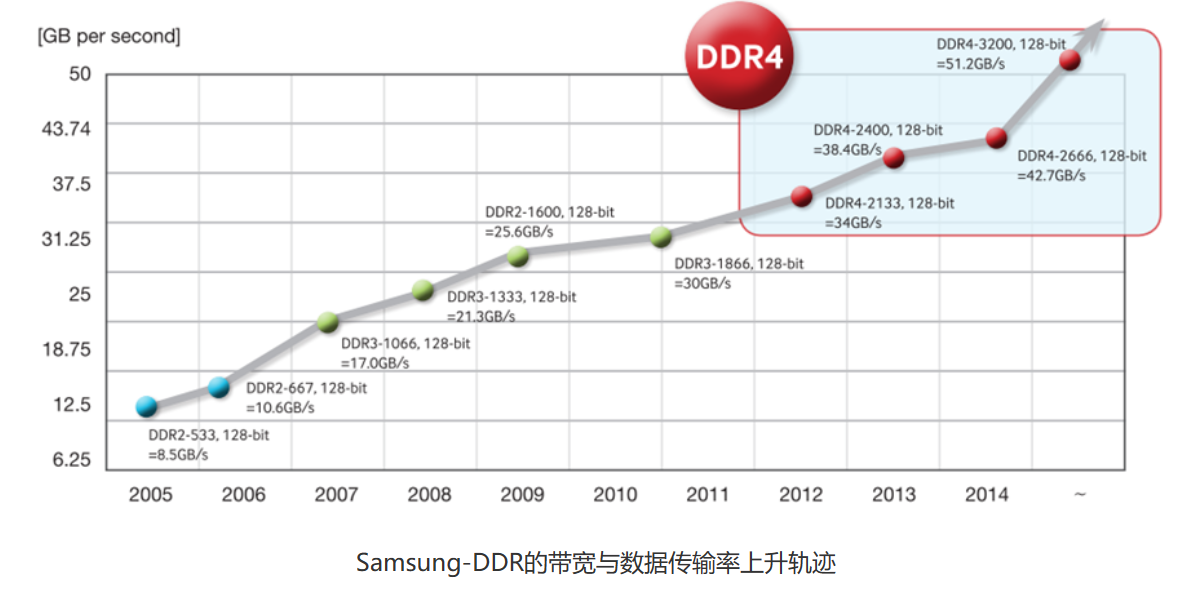

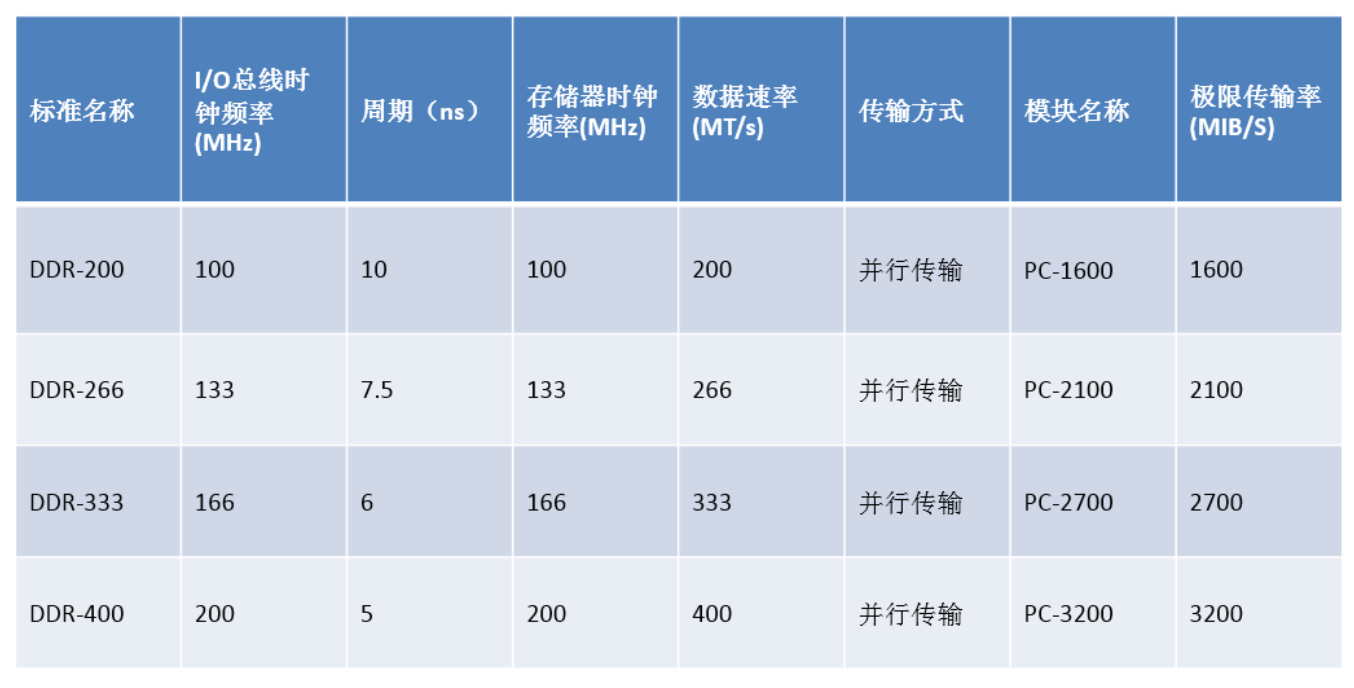

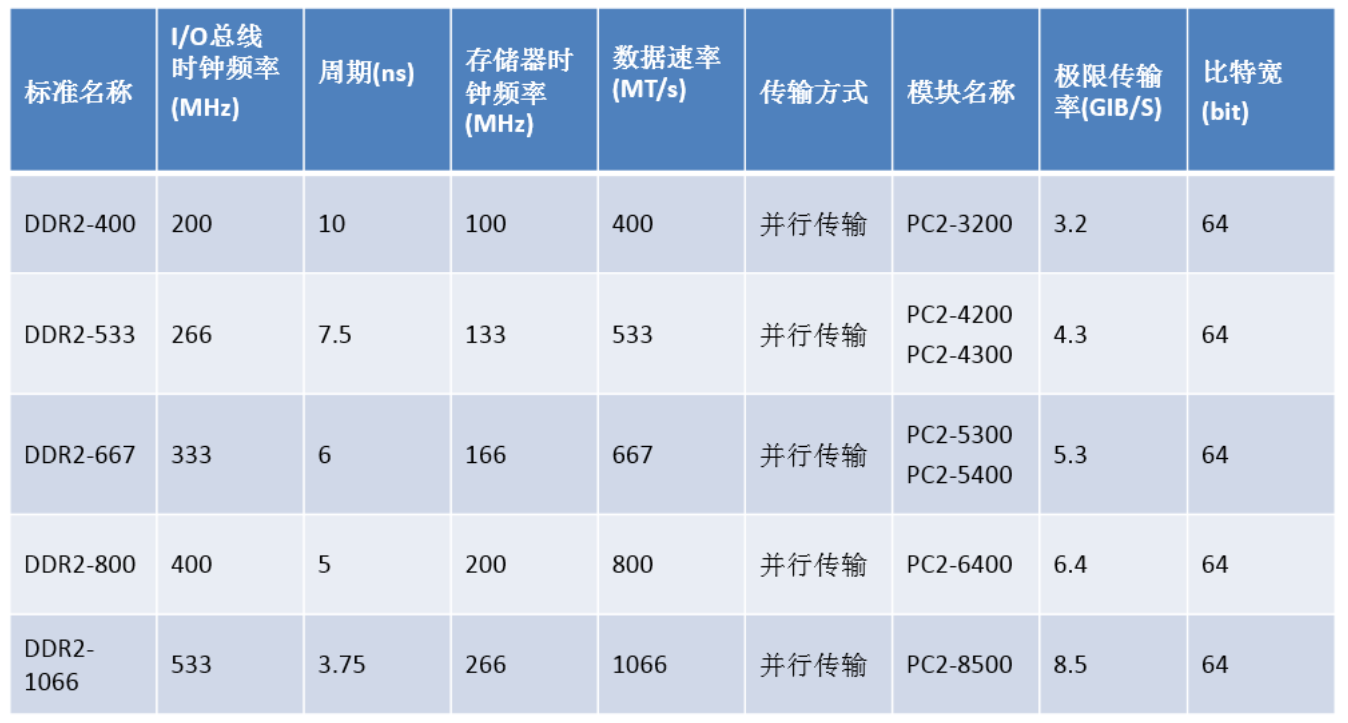

DDR的带宽于时间的关系见下:

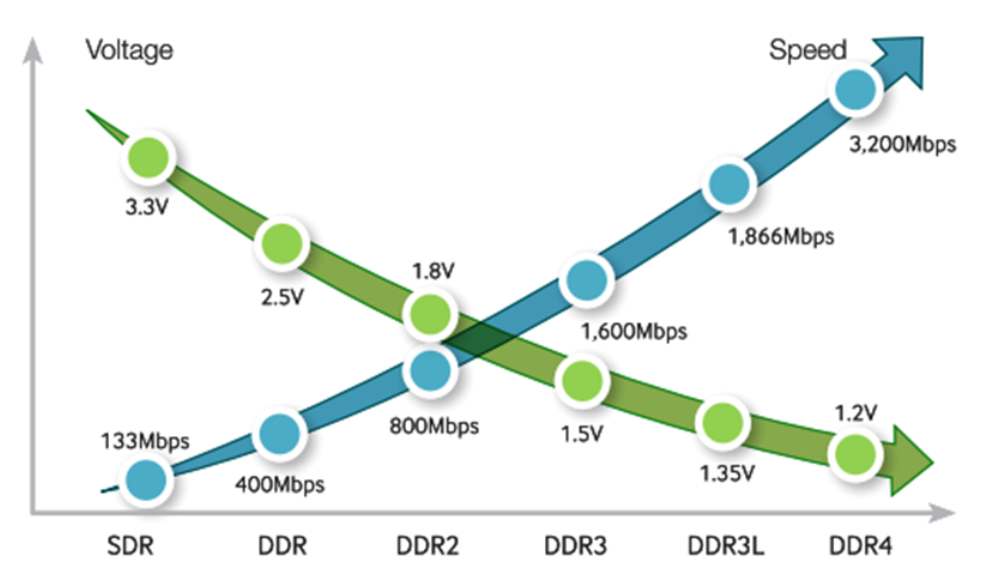

DDR核电压与速率的关系见下:

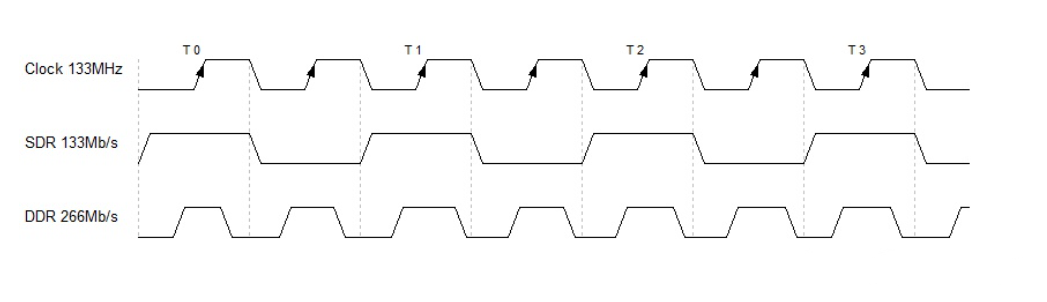

DDR数据传输速度为系统钟频率的两倍,能在选通脉冲的上升沿和下降沿传输数据,见下:

- DDR2

DDR2的数据传输速度为系统时钟频率的四倍,详情见下:

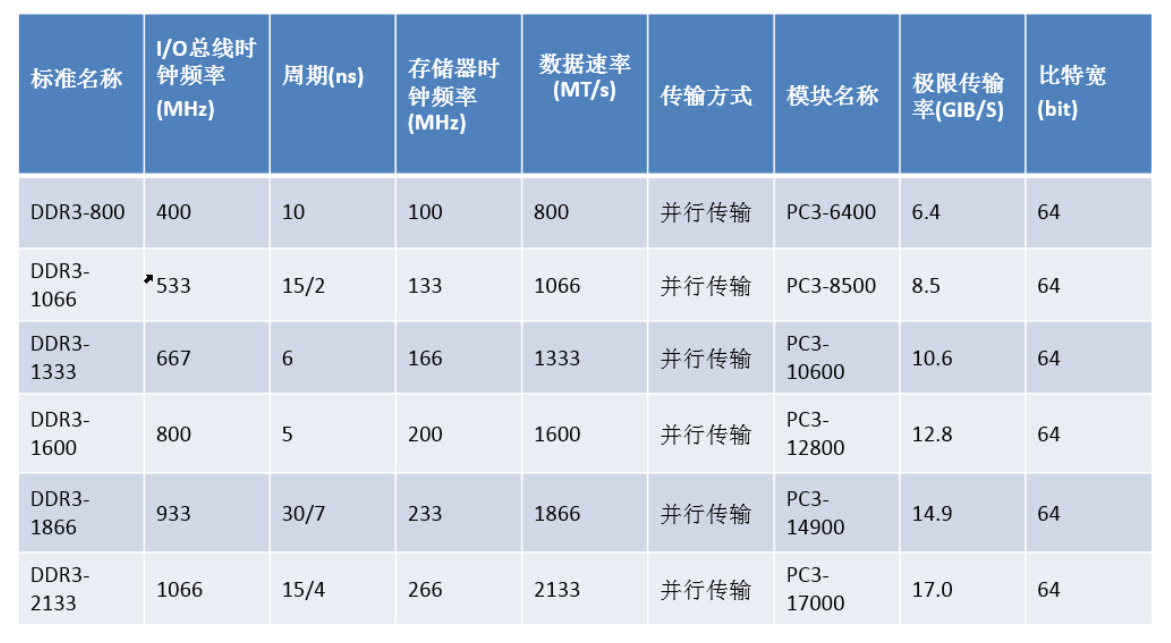

- DDR3

DDR3的数据传输速度为系统时钟频率的8倍,详情见下:

目前DDR常见的厂家有:三星、镁光(慎用,已不华出售)、东芝,长鑫、紫光等。

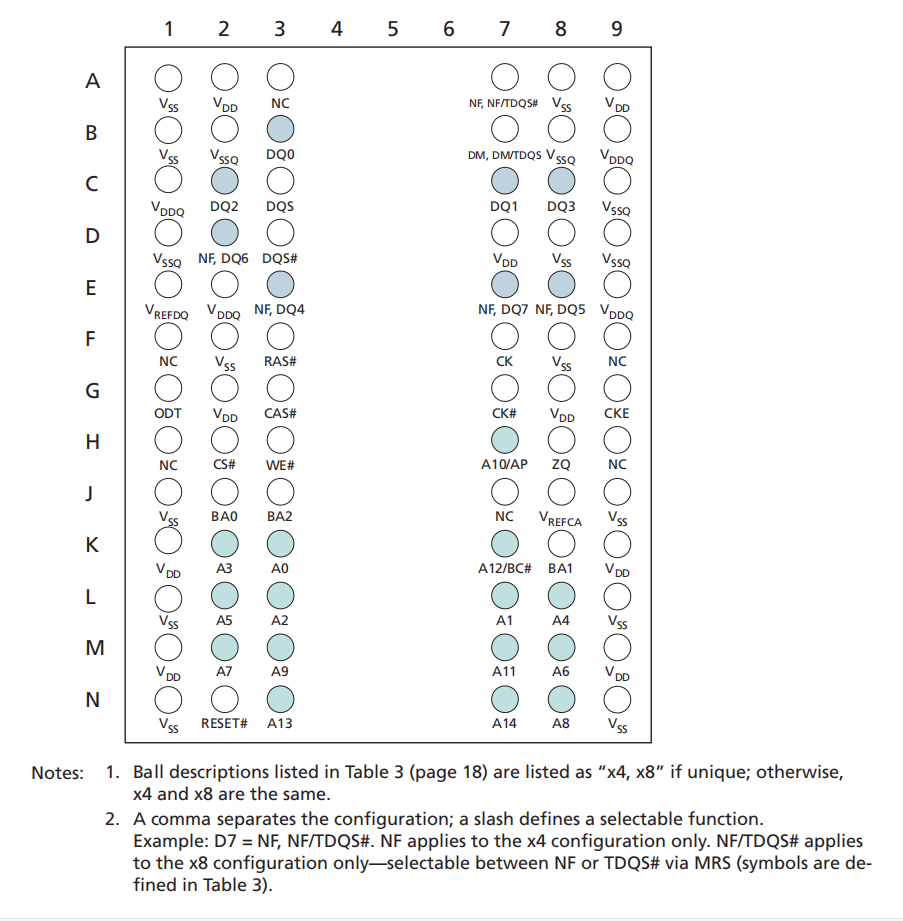

3 DDR的封装

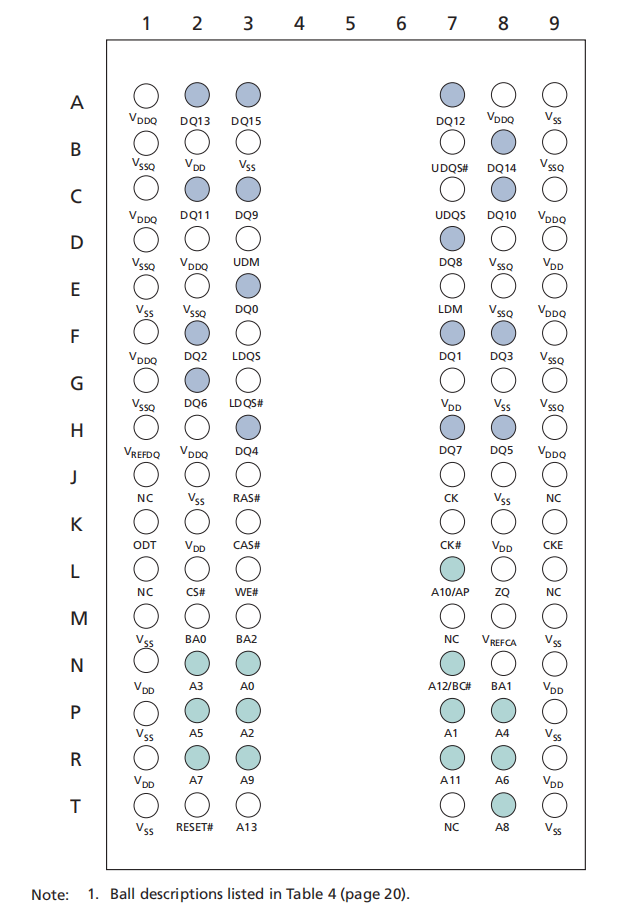

DDR3和DDR4的封装主要有两种:78-Ball FBGA – x4, x8 和96-Ball FBGA – x16。

- 78-Ball FBGA – x4, x8 (Top View)

- 96-Ball FBGA – x16 (Top View)

4 DDR的容量计算

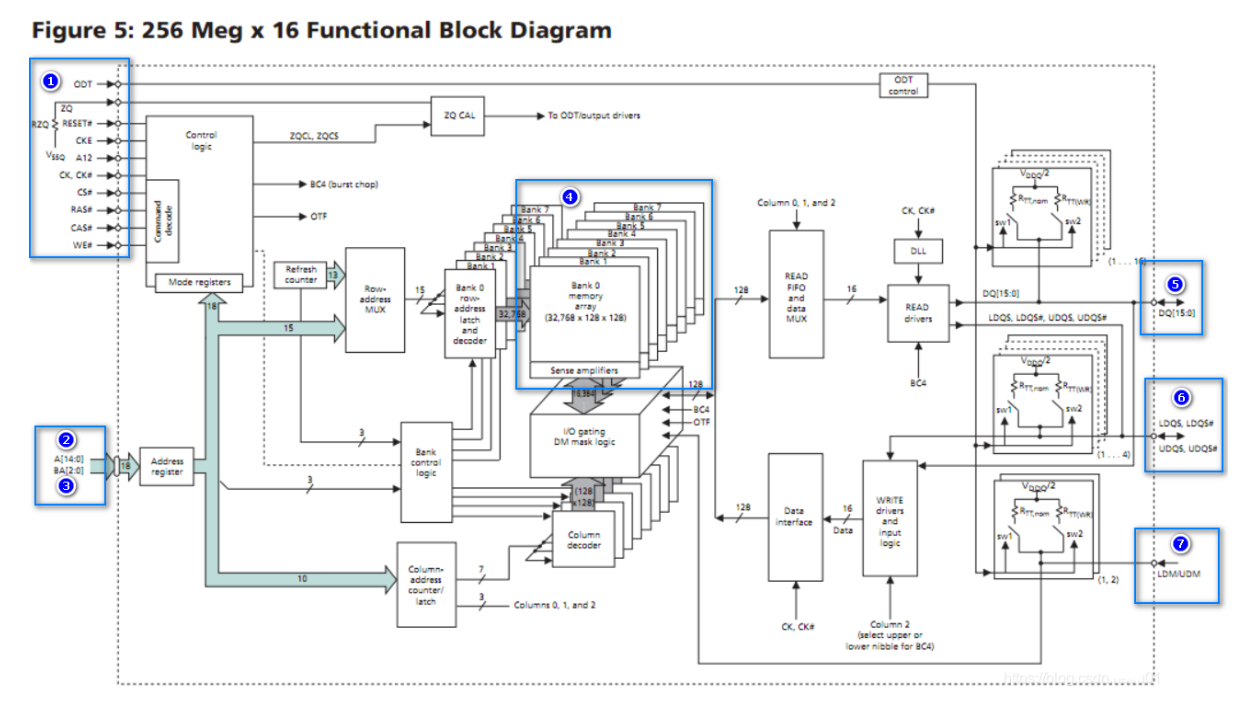

由图可以归纳出:

- bank有8个;对应BA[2:0];

- 行地址有15bit;列地址有10bit(其中低3bit不会用于列寻址);

- 内存颗粒的容量 =行列单元存储bit数=2^15 * 2^10 * 8*16bit=4096Mbit

- 根据DDR数据信号线位宽,描述上图产品的规格,即256 * 16bit。

说明:15为行地址数目;7为列地址数目;8为Bank数目;16为数据位宽。

5 DDR的基本原理

DDR里面主要使用了Double Data Rate 和 Prefetch两项技术。实际上,无论是 SDR 还是 DDR 或 DDR2、3,内存芯片内部的核心时钟基本上是保持一致的,都是 100MHz 到 200MHz(某些厂商生产的超频内存除外)。DDR即 Double Data Rate 技术使数据传输速度较 SDR 提升了一倍。如下图所示,SDR 仅在时钟的上升沿传输数据,而 DDR 在时钟信号上、下沿同时传输数据。例如同为133MHz 时钟,DDR 却可以达到 266Mb/s 的数传速度。

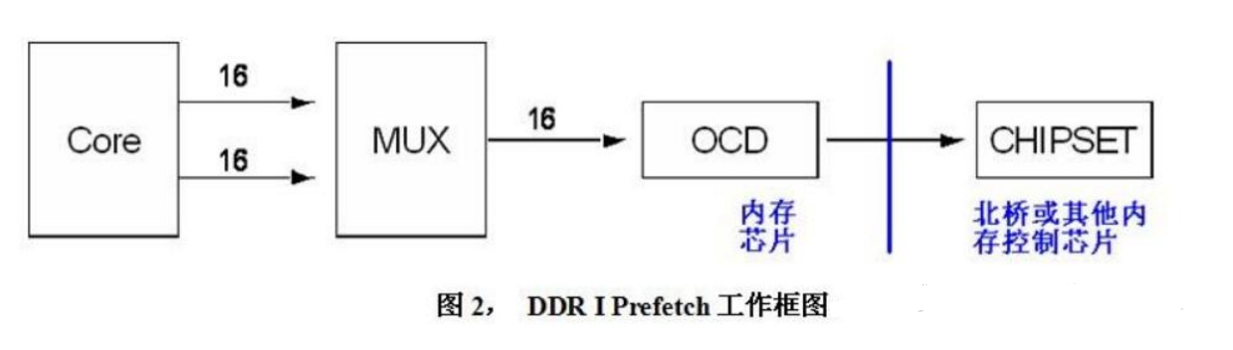

芯片内部数据数据传输速度的提升则是通过 Prefetch 技术实现的。所谓 Prefetch 简单的说就是在一个内核时钟周期同时寻址多个存储单元并将这些数据以并行的方式统一传输到 IO Buffer 中,之后以更高的外传速度将 IO Buffer 中的数据传输出去。这个更高的速度在 DDR I 上就是通过Double Data Rate 实现的,也正因为如此,DDR I 外部 Clock 管脚的频率与芯片内部的核心频率是保持一致的。如下图所示为 DDR I 的Prefetch 过程中,在 16 位的内存芯片中一次将 2 个 16bit 数据从内核传输到外部MUX 单元,之后分别在 Clock 信号的上、下沿分两次将这 2 x 16bit 数据传输给北桥或其他内存控制器,整个过程经历的时间恰好为一个内核时钟周期。

发展到 DDR2, 芯片内核每次 Prefetch 4 倍的数据至 IO Buffer 中,为了进一步提高外传速度,芯片的内核时钟与外部接口时钟(即我们平时接触到的Clock 管脚时钟)不再是同一时钟,外部 Clock 时钟频率变为内核时钟的 2 倍。同理, DDR3 每次 Prefetch 8 倍的数据,其芯片 Clock 频率为内核频率的 4 倍, 即 JEDEC标准(JESD79-3)规定的 400MHz 至 800MHz,再加上在 Clock 信号上、下跳变沿同时传输数据,DDR3 的数据传输速率便达到了 800MT/s 到 1600MT/s。具体到内存条速度,我们以 PC3-12800 为例,其采用的 DDR3-1600 芯片核心频率为 200MHz,经过Prefetch 后 Clock 信号频率到达 800MHz,再经过 Double Data Rate 后芯片数据传输速率为 1600 MT/s,内存条每次传输 64 bits或者说 8 bytes数据,1600*8 便得到12800MB/s 的峰值比特率。

6 引脚说明

| 信号名 | 方向 | 功能描述 |

|---|---|---|

| CK_t,CK_c | Input | 差分时钟输入。所有的地址、控制信号都是通过CK_t的上升沿与CK_c的下降沿进行采样的 |

| CKE | Input | 时钟使能:CKE为高电平时,启动内部时钟信号、设备输入缓冲以及输出驱动单元。CKE低电平时则关闭上述单元。当CKE为低电平时,可使设备进入PRECHARGE POWER DOWN、SELF-REFRESH以及ACTIVE POWER DOWN模式。CKE与SELF REFRESH退出命令是同步的。在上电以及初始化序列过程中,VREFCA与VREF将变得稳定,并且在后续所有的操作过程中都要保持稳定,包括SELF REFRESH过程中。CKE必须在读写操作中保持稳定的高电平。在POWER DOWN过程中,除CK_t,CK_c,ODT以及CKE以外的所有输入缓冲都是关闭的。在SELF REFRESH过程中,除CKE以外的所有输入缓冲都是关闭的。在正时钟上升边沿采样。 |

| CS_n | Input | 片选信号:当CS_n锁存为高电平时,所有的命令都被忽略。在正时钟上升边沿采样。 |

| CA_n | Input | 命令/地址输入信号。可作为地址线使用,也可作为命令代码使用,是命令代码的一部分。 |

| ODT | Input | On-Die Termination,片上终端电阻:ODT信号可使能DDR SDRAM内部的RTT_NOM终端电阻。该设计通过允许DRAM控制器独立地打开/关闭任一或所有DRAM设备的终端电阻来改善存储器通道的信号完整性。 DRAM通过ODT控制引脚为每个DQ,DQS_t及DQS_c和DM开启/关闭终端电阻。与其他输入命令不同,ODT引脚直接控制ODT动作,不对其进行时钟采样。 请注意,如果在掉电模式下启用ODT,则在掉电期间可能无法关闭VDDQ(I/O供电),同时DRAM也会在读操作期间无法关闭。 |

| DM_n | Input | 输入数据掩码:DM_n信号是作为写数据的掩码信号,当DM_n信号为低电平时,写命令的输入数据对应的位将被丢弃。DM_n在DQS的两个条边沿都采样。 |

| DQ | Input\Output | 数据输入、输出:双向数据总线。若模式寄存器中使能了CRC功能,那么在数据burst结束时就会附加一段CRC码。 |

| DQS_t,DQS_c | Input\Output | 差分数据选通信号:差分信号对,作输入时与写数据同时有效,作输出时与读数据同时有效。读数据时与边沿对齐,但是跳变沿位于写数据的中心。DDR4 SDRAM仅支持选通信号为差分信号,不支持单根信号的数据选通信号。 |

| NC | N.A | 无电气连接。 |

| VDDQ | Supply | I/O供电:1.2V +/- 0.06V |

| VSSQ | Supply | GND |

| VDD | Supply | Core供电:1.2V +/- 0.06V |

| VDDCA | Supply | CA供电 |

| VSSCA | Supply | GND |

| VSS | Supply | GND |

| VPP | Supply | DRAM激活供电:2.5V(最小2.375V,最大2.75V) |

| VREF | Supply | 参考电压 |

| ZQ | Supply | Drive Strength Calibration校准参考电阻 |

7 PCB设计要点

- 考虑BGA可维修性:BGA周边器件5MM禁布,最小3MM。

- DFM 可靠性:按照相关的工艺要求,布局时器件与器件间满足DFM的间距要求;且考虑元件摆放的美观性。

- 绝对等长是否满足要求,相对长度是否容易实现:布局时需要确认长度限制,及时序要求,留有足够的绕等长空间。

- 滤波电容、上拉电阻的位置等:滤波电容靠近各个PIN放置,储能电容均匀放置在芯片周边(在电源平面路径上);上拉电阻按要求放置(布线长度小于500mil)。

注意:如有提供DEMO板或是芯片手册,请按照DEMO板或是芯片手册的要求来做。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?