目录

1 功能

在FPGA上实现可动态调整低通滤波器截止频率的滤波模块,并且滤波系数通过外部模块输入。

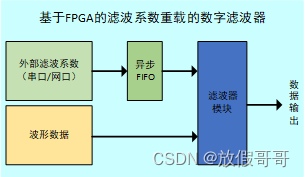

2 框架

整个框架分为三个部分,滤波系数的输入、滤波系数的重载,低通滤波。其中,滤波系数我通过串口送入,经过一个异步FIFO进行跨时钟处理(串口的时钟和滤波器的时钟可能不同),在经重载模块送入低通滤波器模块,这里低通滤波器直接采用赛灵思的官方IP核。

3 FIR IP设置

网上有很多关于此IP核的说明与使用,本文就不在阐述,主要说下核心配置,首先是滤波器系数配置界面,滤波器系数可使用Matlab生成,具体操作可参考(Matlab生成滤波器抽头系数)这篇博客。

1:Select Source 有Vector 和COE File两种选择。Vector是十进制系数,COE File可通过Matlab生成。同时要进行系数重载需勾选Use Reloadabel Coefficients。

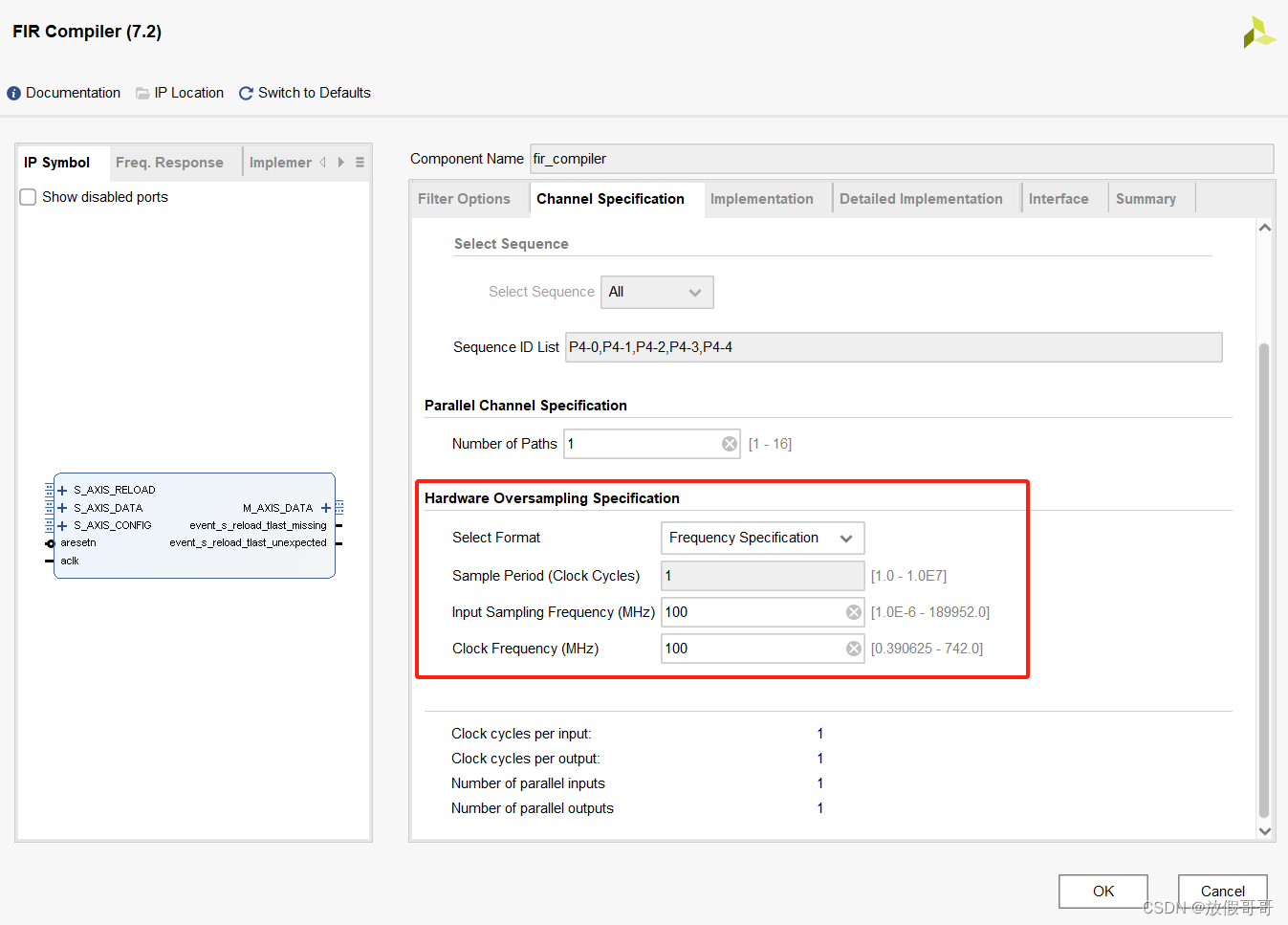

2:Channel Specification:这个是设置采样率工作时钟一致。

3:接着是滤波系数和输入数据位宽及数据类型、重加载顺序、输出数据模式(Full Precision 全精度,即不舍弃位宽)的选择,其他的保持默认即可,也可根据具体需求进行更改。

4 仿真验证

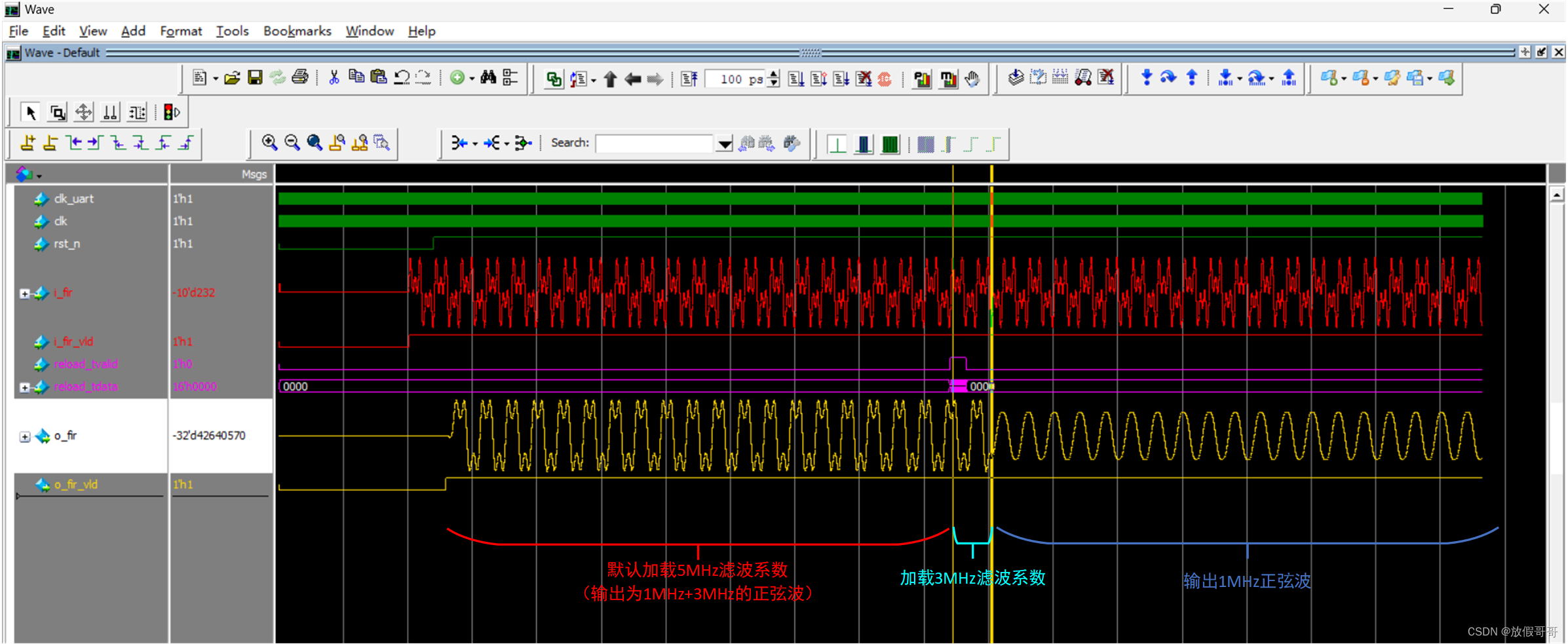

采用DDS IP产生1MHz、3MHz、5MHz的正弦波信号进行叠加作为滤波器的输入信号,并在仿真中模拟串口输入新的滤波系数。输出波形如下图所示,滤波器默认加载的是滤除5MHz的抽头系数,再加载完3MHz滤波系数后,输出为1MHz正弦波。

5 资源获取

https://m.tb.cn/h.gTEUuAq?tk=d0GSWAKypI2 CZ3460

2439

2439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?