1.驱动原理

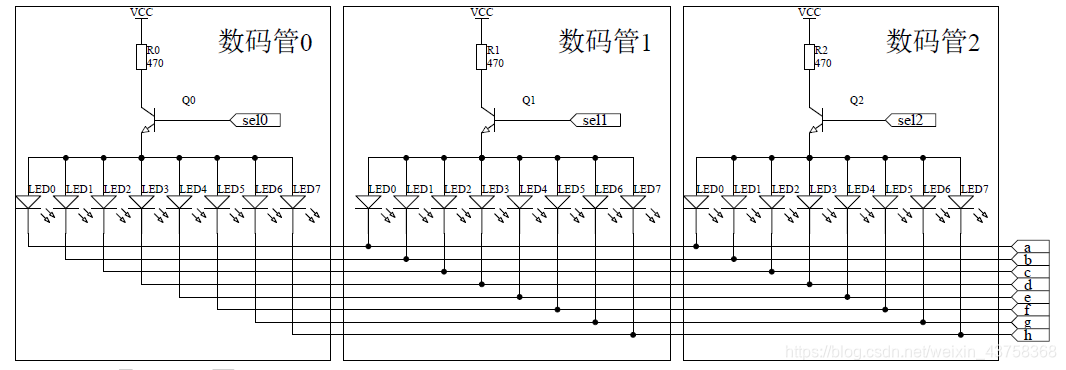

其中8段数码管的动态显示驱动如图1所示,动态显示的特点是将所有位数码管的段选线 并联在一起,由位选线控制是哪一位数码管有效。选亮数码管采用动态扫描显示。所谓动态扫描显示即轮流向各位数码管送出字形码和相应的位选,利用发光管的余辉和人眼视觉暂留作用,使人的感觉好像各位数码管同时都在显示。

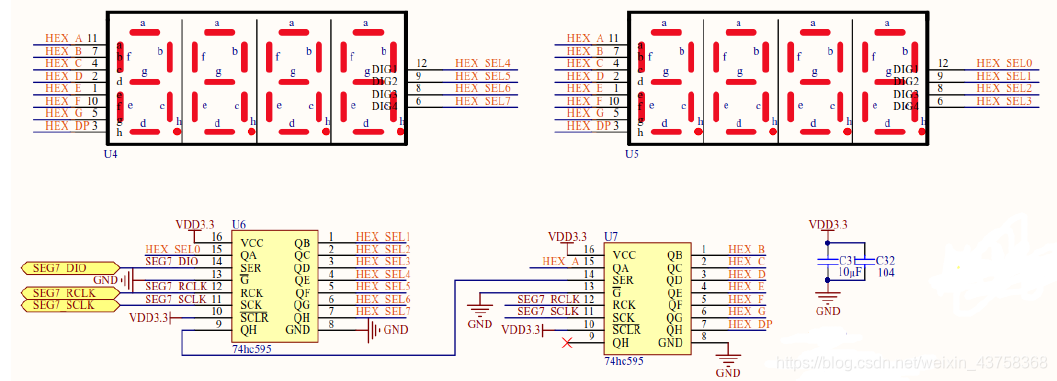

而在实际的使用中,由于FPGA出来的引脚资源宝贵,因此在FPGA外部用了两个74HC595的芯片进行控制。其主要的作用就是将FPGA输出的串行信号转化为数码管需要的sel信号以及段信号(seg)。74HC595的芯片示意图如下。

可以看出该芯片需要3个信号,分别为DIO(串行数据),RCLK(移位寄存时钟),SCLK(存储时钟),以下分别称为DS,SH_CP,ST_CP。

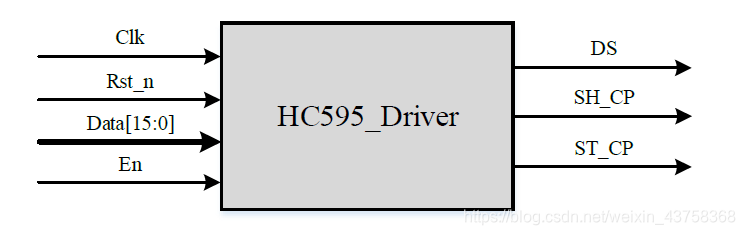

数码管的驱动如下所示。即,在FPGA内部产生动态的扫描seg和sel。其中的En没有在设计中使用,所以在代码中去掉。

然后将产生的sel和seg如何送入到74HC595芯片?通过设计出其需要的端口及串行信号以及另外的两个时钟信号即可。模块原理图如下。

因此总共包括两个部分:1,扫描信号驱动,2,模块接口驱动。

2.RTL部分

(1).产生计数信号用于sel的翻转

module divider(clk, rst_n,divider_cnt,clk_1k);

input clk;

input rst_n;

output reg [31:0] divider_cnt;

output reg clk_1k;

parameter CNT_MAX = 28'd49_999;

//对divider_cnt进行计数,计数到24999就归零

alway

本文介绍了FPGA中八位数码管动态显示的驱动原理,通过74HC595芯片将FPGA的串行信号转换为数码管所需的sel和seg信号。动态扫描显示利用人眼视觉暂留效果,实现多位数码管同时显示的错觉。设计包含扫描信号驱动和模块接口驱动两部分,并详细说明了RTL部分和模块驱动信号的实现过程。

本文介绍了FPGA中八位数码管动态显示的驱动原理,通过74HC595芯片将FPGA的串行信号转换为数码管所需的sel和seg信号。动态扫描显示利用人眼视觉暂留效果,实现多位数码管同时显示的错觉。设计包含扫描信号驱动和模块接口驱动两部分,并详细说明了RTL部分和模块驱动信号的实现过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1228

1228

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?