本项目基于Xilinx artix-7 xc7a35t 芯片

开发软件是VIVADO 2018.3

RAM,即随机存储器,是计算设备中作为临时数据存储媒介的一种单元,它的特点是速度快,可按要求随意存入取出、掉电丢失。在各类逻辑系统中运用非常广泛。

在FPGA高级应用四的这个标题下,我们将会从内部存储器到外部存储器,介绍FIFO、ram、ddr几种常用的存储器设计。

第一期我们介绍FIFO

FIFO,全称是first in first out (先入先出存储队列) 。

在程序中FIFO作为数据的队列通道,让数据暂时缓存,等待读取,FIFO没有地址,先入先出!

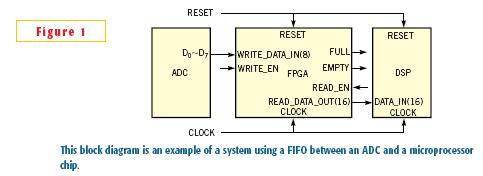

FIFO的结构如下图

data in/out 是数据输入/出口

write/read en 是写/读使能信号

clk 是FIFO时钟

reset复位

empty/full分别是表示FIFO空/满的信号

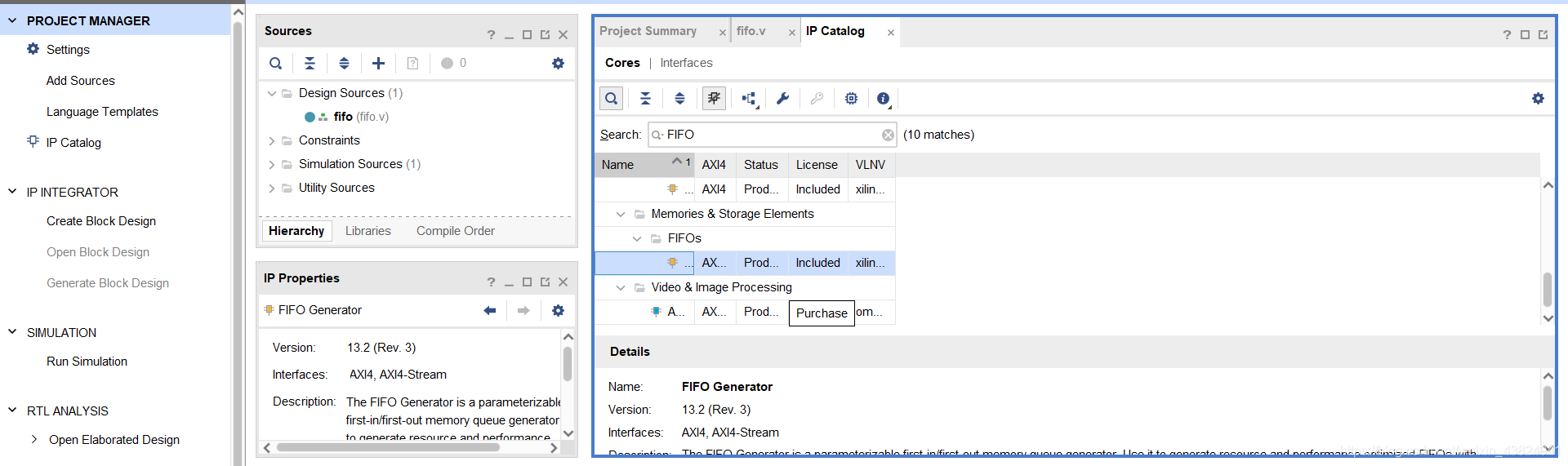

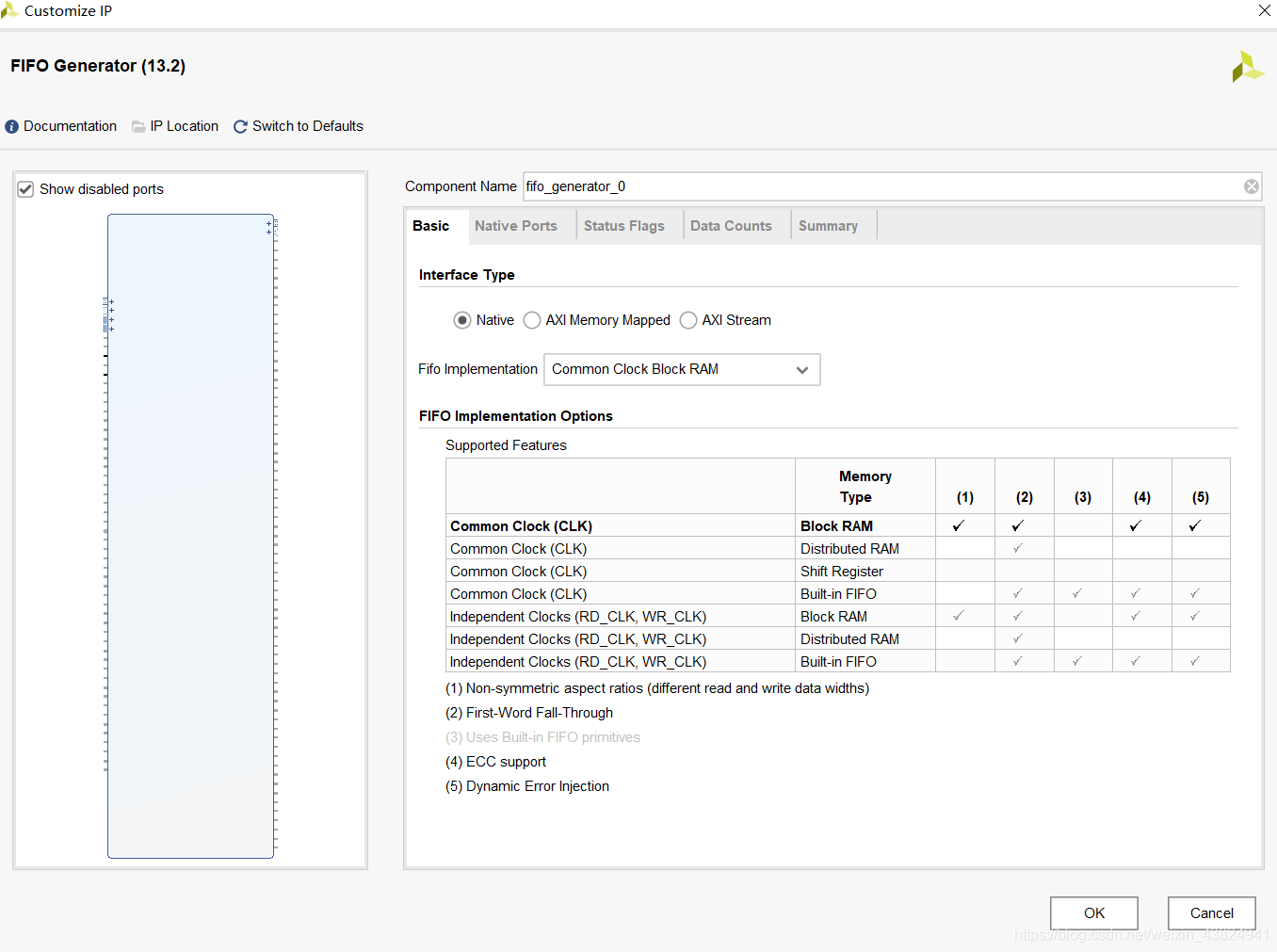

这里我们直接使用Xilinx提供的ip核来进行开发:

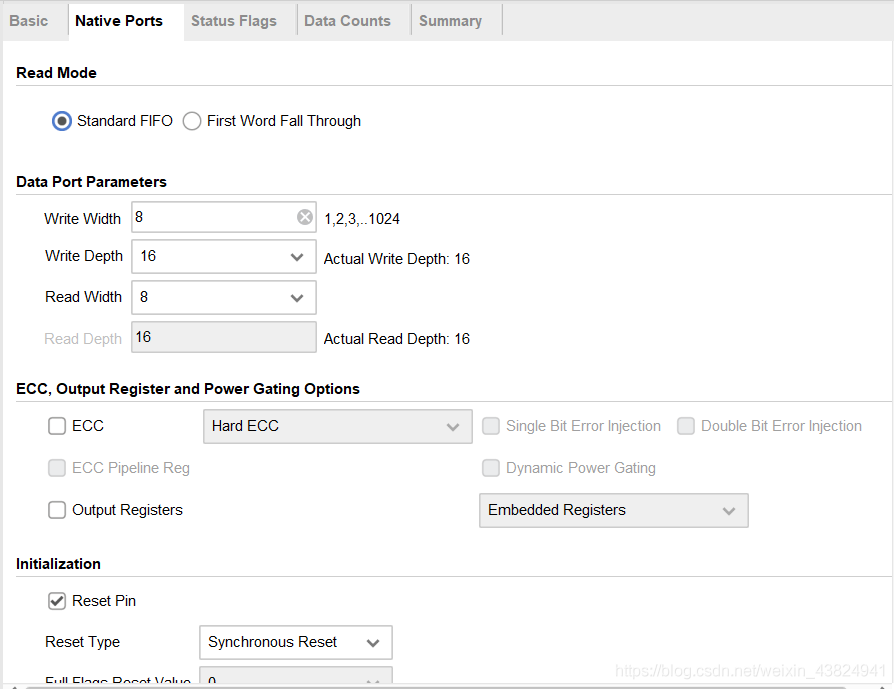

这里选择native (不启用总线)

然后在native ports 页面选择standard FIFO ,这里我们可以确定数据的宽度,确定读写的深度。

接下来在status flags 里面选择数据为多少时拉起满/空标志位。

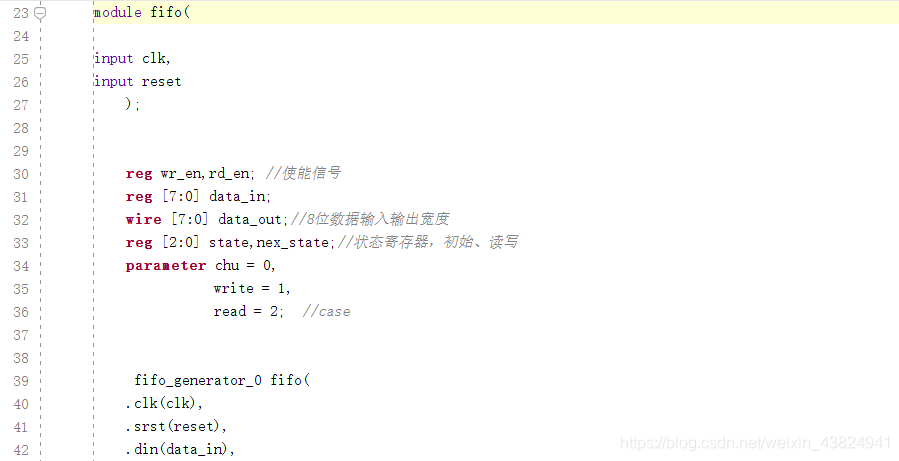

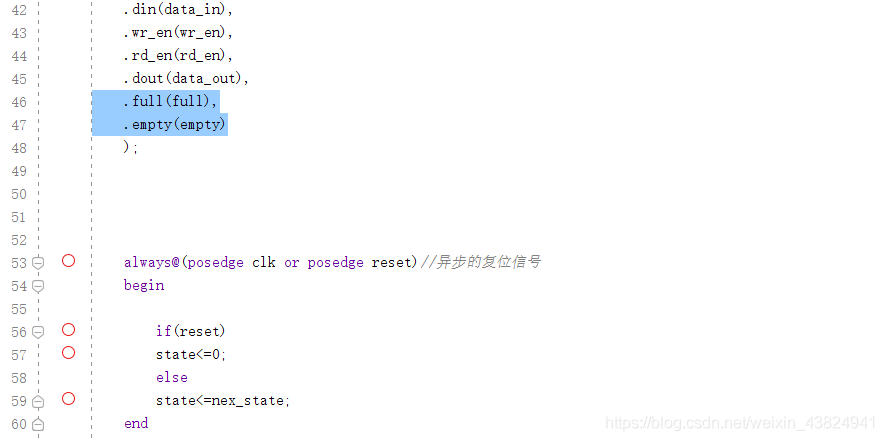

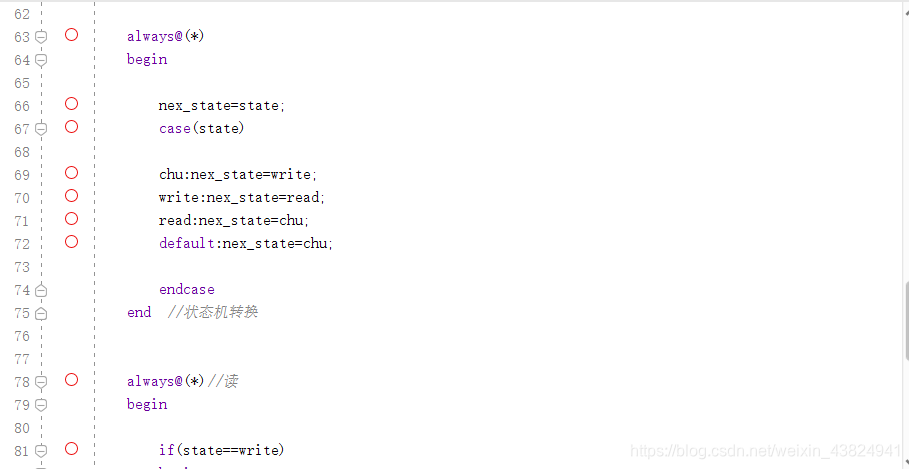

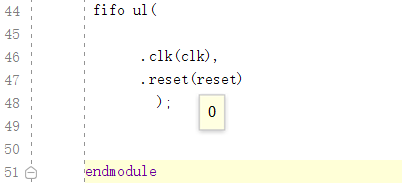

建立好IP核之后,我们写顶层模块:

上图中的复位功能,其中posedge reset 这个触发信号非常重要!如果没有这个触发就不能实现功能!

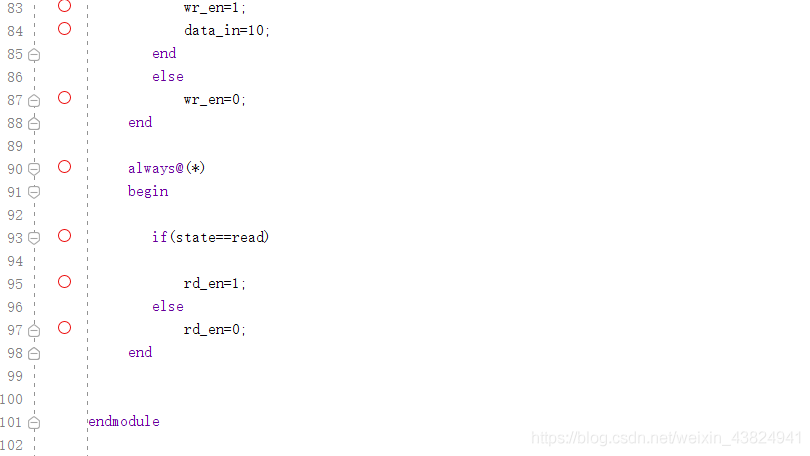

然后是仿真文件:

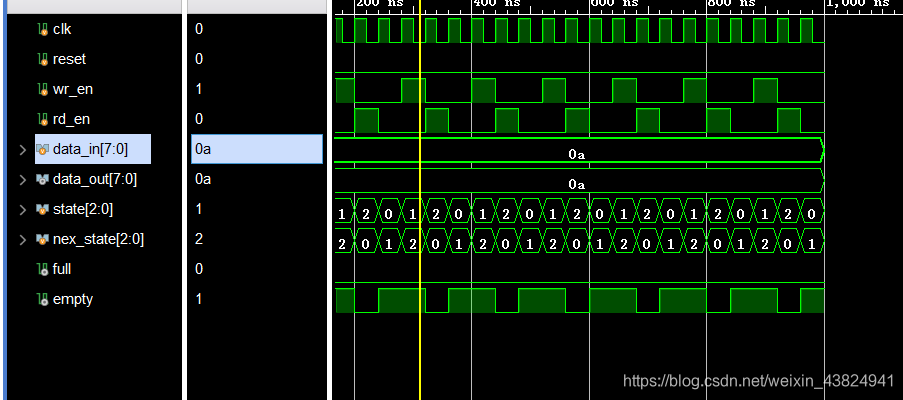

最后形成的仿真如下:

到这里咱们的FIFO就完成了。

谢谢观看!

3854

3854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?