硬件乘法器——由组合逻辑组合的乘法器

一. 整数乘法器:

1.1整数的概念:

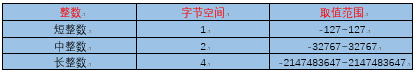

整数包括:短整数(short integer)、中整数(integer)和长整数(long integer)

① 短整数的最高位是符号位,符号位的正负表示了该值是“正还是负”,正值的表示方法一般是8位二进制数来表示,负值的表示方法是以补码来表示

+127——8’b0111_1111(表示位宽为8的二进制数)

+4——8’b0000_0010

-4——8’b1111_1100(在原码的基础上先求出反码,再在末位加上1求出补码)

比如求出-4的补码的操作:

8’b0000_0100;表示4

8’b1111_1011求出4的反码

8’b1111_1100这就是补码

② 短整数里面的一个特殊存在8’b1000_0000:

+127——8’b0111_1111

划分——8’b1000_0000

-127——8’b1000_0001(可以这么说:在8’b1000_0000之前的都是正值,在其后的都是负值)

③ 正值可以经过“求反加一成正值”,负值同样可以“负值求反加一成正值”:

-4——8’b1111_1100

求反——8’b0000_0011

加一——8’b0000_0100

1.2乘法器

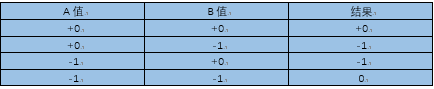

在传统的概念上乘法等价于:“重复几次”,打个比方:B= 4,A * B亦即A要重复加4次才能得到答案,在乘法中,“负值正值的关系”就是异或的关系

从上面的内容看出:无论A值和B值是什么样的“正值和负值的关系”,结果C都是一样,所以我们可以有一个想法:“在做乘法的时候只是我们只要对正值进行操作,然而‘负值和正值的结果’,我们用异或关系来判断”

实验一:传统的乘法器(代码有点冗长,不是我现在能驾驭的)

该乘法器的大致思路是:

1) 在初始化之际,取乘数和被乘数的正负关系,然后取被乘数和乘数的正值

2) 每一次累加操作,递减一次乘数,直到乘数的值为0,表示操作结束

3) 输出结果根据正负关系取得

先来看一下简单的二位乘法器:(假设A0和B0都代表十位数字、B1和A1分别代表个位数字)A0A1B0B1,可以看见下面的表格:(P0到P3分别代表着得到的数字的各位)

Verilog乘法器

最新推荐文章于 2024-01-28 10:12:48 发布

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6651

6651

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?