标题:关于combinational loop(组合逻辑环)的一点探究

最近在写中断轮询round_robin的过程中出现过这个combinational loop的警告信息,当时由于任务要求急,时间紧,就没有仔细研究这块,当时只是简单看了下警告信息,把其中一段组合逻辑改成时序逻辑就解决了问题,现在补一下吧。

废话不多说,先看下警告信息出现的场景吧

loop顾名思义就是说由于设计的需要,designer会把output接回与input一起控制自己的out,其实就是反馈,逻辑上来说这样并没有什么问题,但我们是硬件描述语言,时刻谨记代码是要转换为硬件电路的。在反馈的过程中如果output不经过中间的寄存器直接接回与input进行逻辑控制,那么就会出现comb loop的错误报警,可以看看下面的图示体会一下

上图中左边是有loop报警的,右边在加入了触发器之后就没有了组合逻辑环。

下面的部分是我用代码实现简单印证了一下,觉得没用的话可以忽略哈….

首先看下出现loop报警的代码以及对应的原理图吧

下面是中间使用触发器打断没有comb loop报警的代码及对应的原理图

可以看到,添加了触发器的其实仍然是存在反馈的,即也是有loop的,但为什么这次没出现报警呢???

问题出在综合上,上述的组合逻辑综合时被综合成了一个与非门,这就导致当输入端是逻辑1时,输出端是会进入不断振荡的状态,随着器件延迟不断在0和1之间跳变。这并不是代码的本意,这段代码想描述的是输入变化检测,即out只有在输入a变化时才会置高。因此仿真和综合的结果是有出入的。

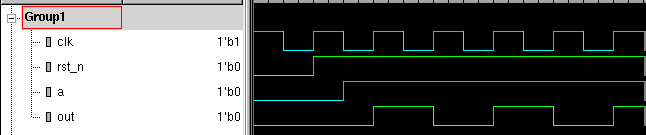

写完才发现上述的分析是有问题的,即我处理loop的方法(直接加触发器)是有问题的,loop还是loop没变,仿真试一下吧

可以看出组合逻辑的代码输出是无法预知的,

至于我之前写round_robin模块中解决comb loop的方法正确是正确,结果是好的,但是我过程有点冗余,多写了一个触发器,理解有一定的偏差,在本篇博客的撰写过程中也及时纠正过来,理解的跟能写下来果然还是挺有差距的,慢慢进步吧!!!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?