Verilog代码bug:一种特殊的组合逻辑环

组合逻辑环(Combinational Loop)是什么,别的文章已经写的很多了,本文就不赘述了,本文主要记录遇到过的一种特殊的逻辑环;

代码如下所示:

module test(

b, a0

);

input b;

output a0;

assign a = !b ? a0 : 1'b1;

assign a0 = !b ? 1'b0 : a;

endmodule

理论上,若b=0, 则a0 = 1’b0;

若b=1,则a0 = 1’b1;不会产生组合逻辑环

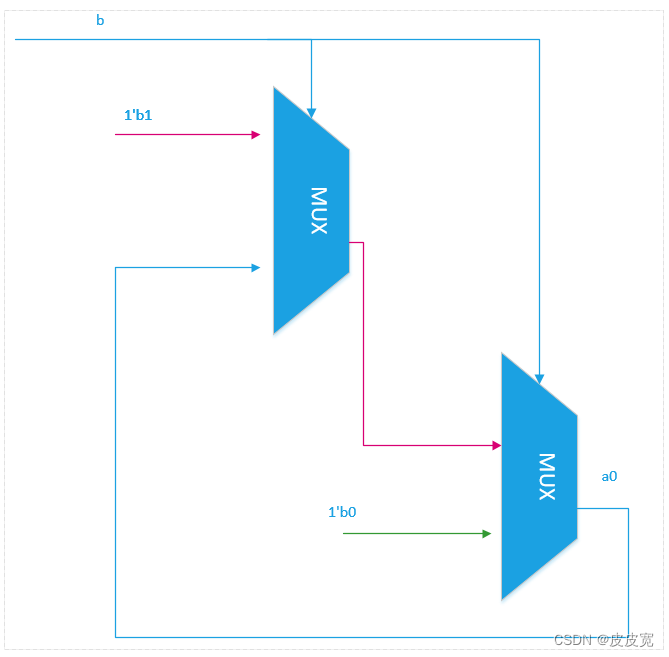

但实际电路结构如下所示:

- b = 1时,数据传输如红线所示,

- b=0时,数据传输如绿色线所示;

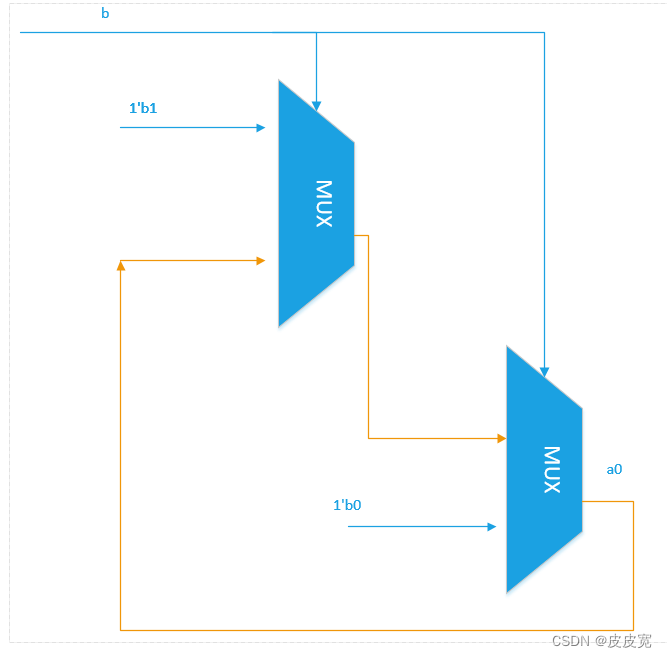

但由于b信号传输到两个MUX选择器端点存在延时的差异,因此当b从1变为0时,可能存在某一时刻,两个MUX接受的b信号,一个是0,另一个还是1(延时差异,还未传输过来),从而导致如下的逻辑环路

因此,这种电路依然会产生组合逻辑环,需要被优化;

661

661

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?