目录

[1.3.x]HS Electrical Characteristics- HS DATA TX

[1.3.2]HS Entry:DATA TX THS-PREPARE

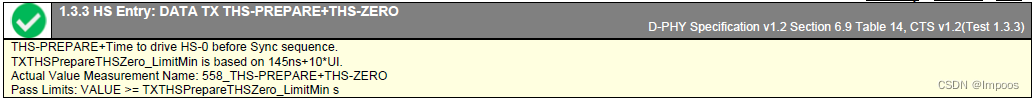

[1.3.3]HS Entry:DATA TX THS-PREPARE+THS-ZERO

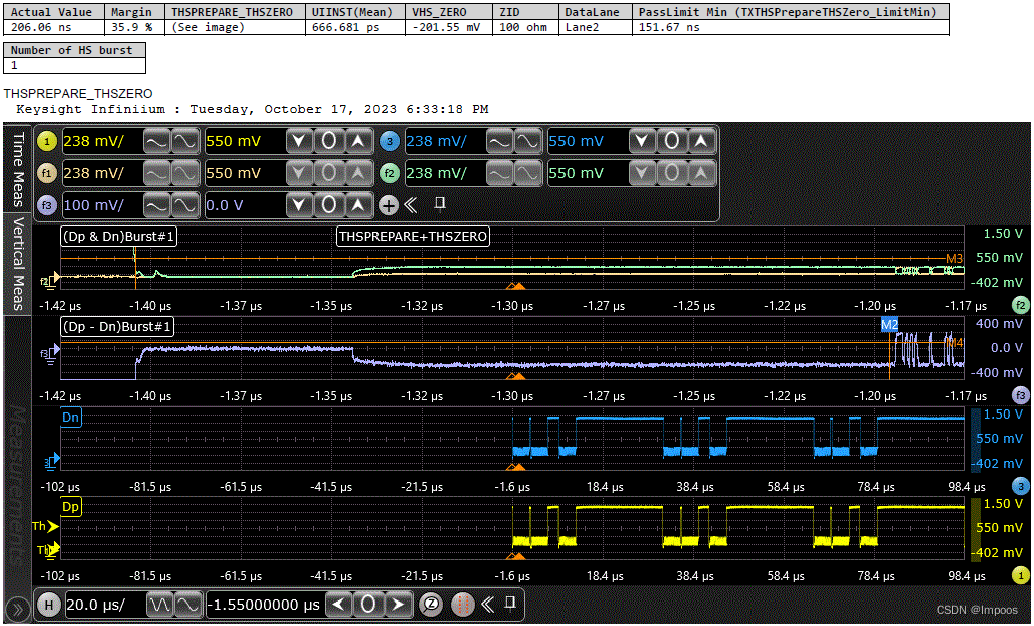

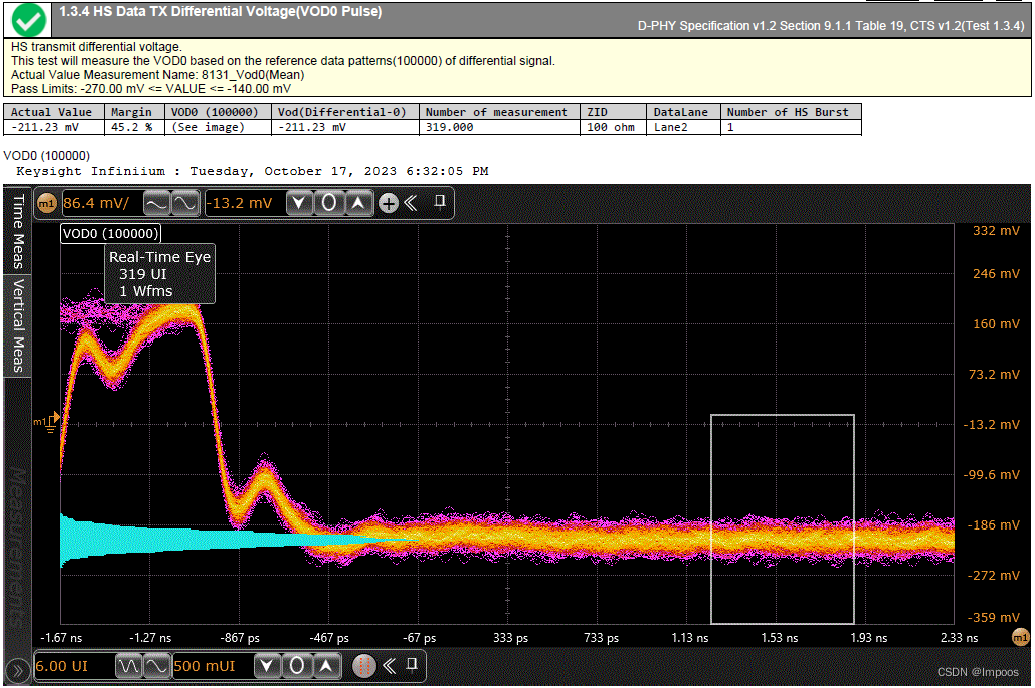

[1.3.4]HS DATA TX Differential Voltage(VOD0/VOD1 Pulse)

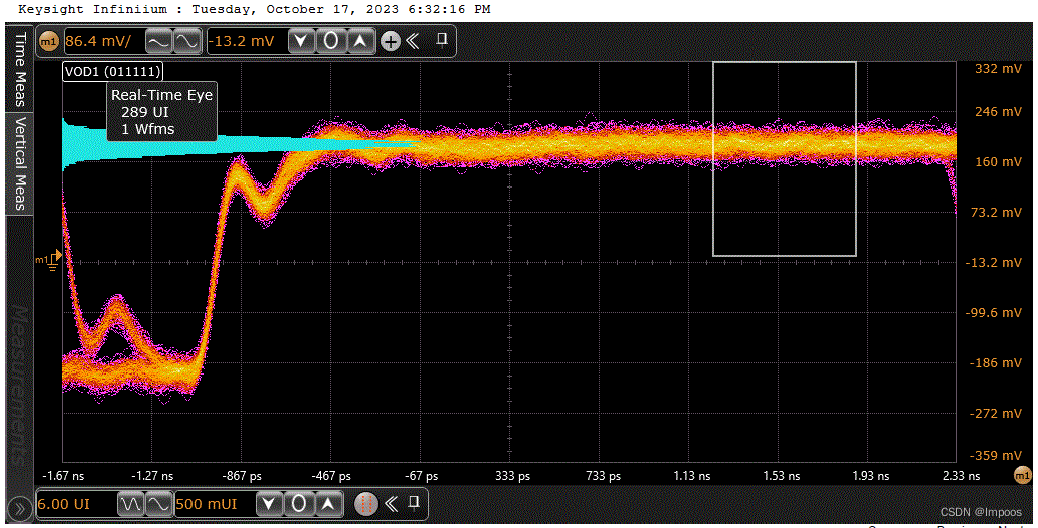

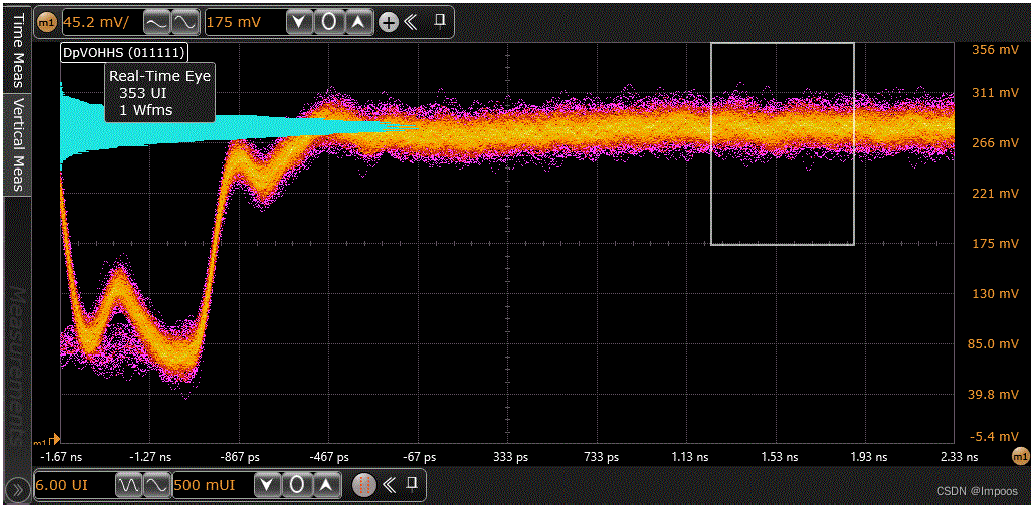

[1.3.5]HS DATA TX Differential Voltage Mismatch(Pulse)

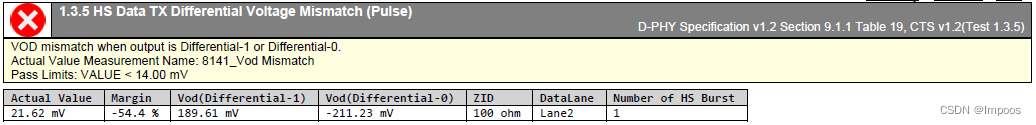

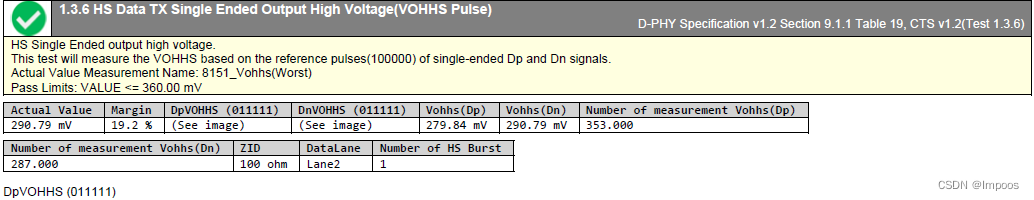

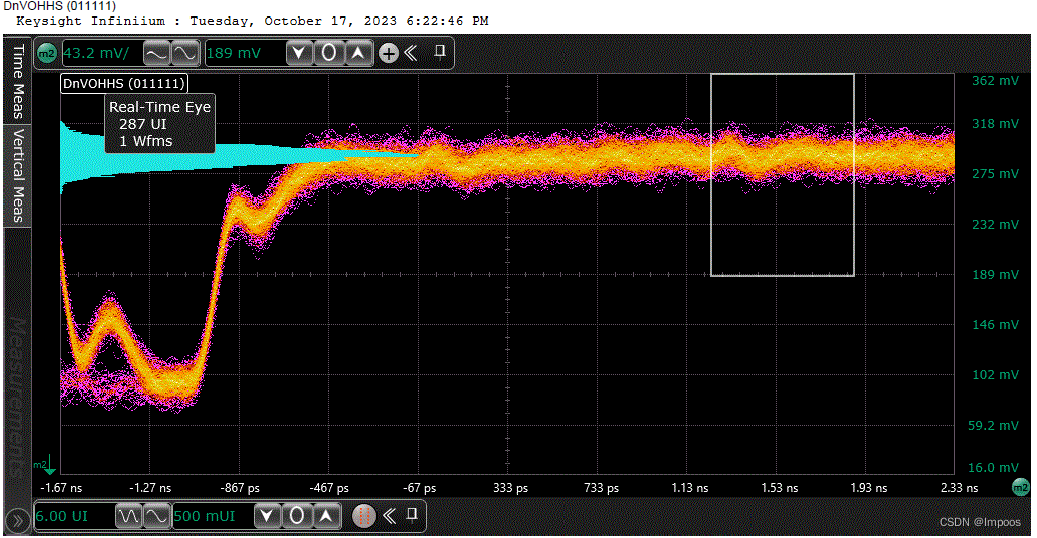

[1.3.6]HS DATA TX Single Ended Output High Voltage(VOHHS Pulse)

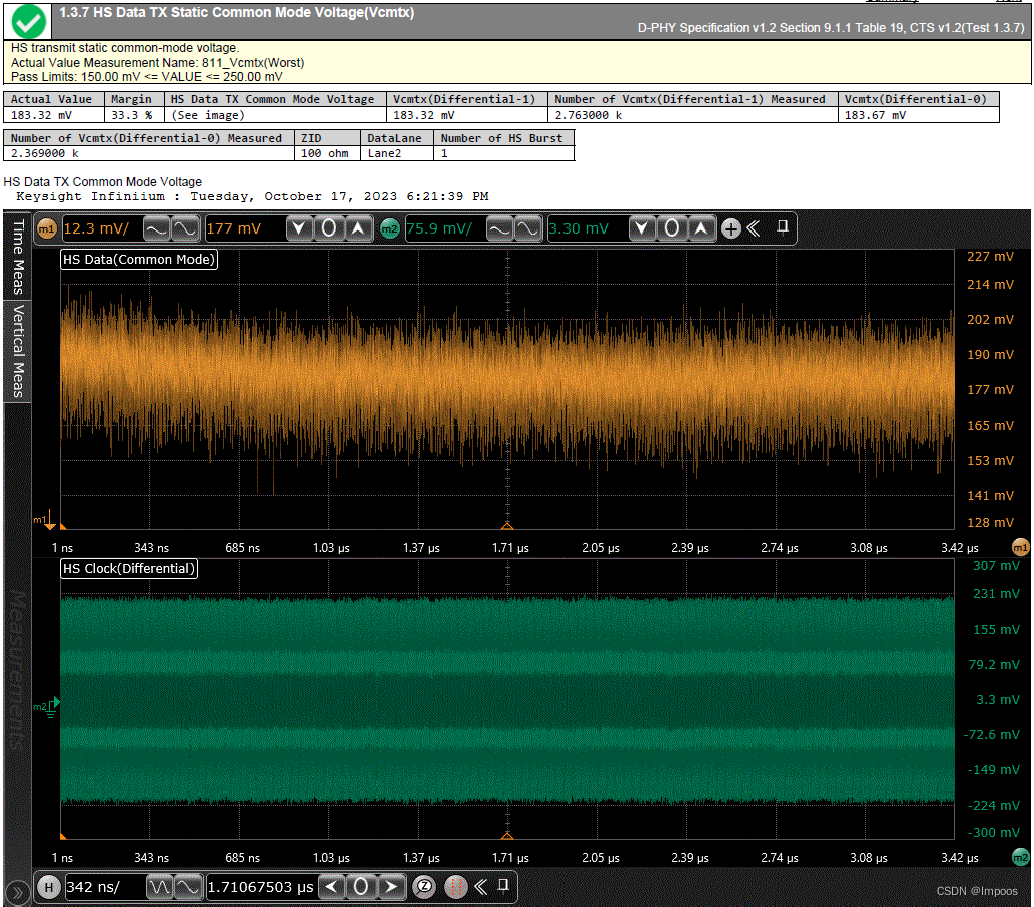

[1.3.7]HS DATA TX Static Common Mode Voltage(VCMTX)

[1.3.8]HS DATA TX Static Common Mode Voltage(VCMTX)

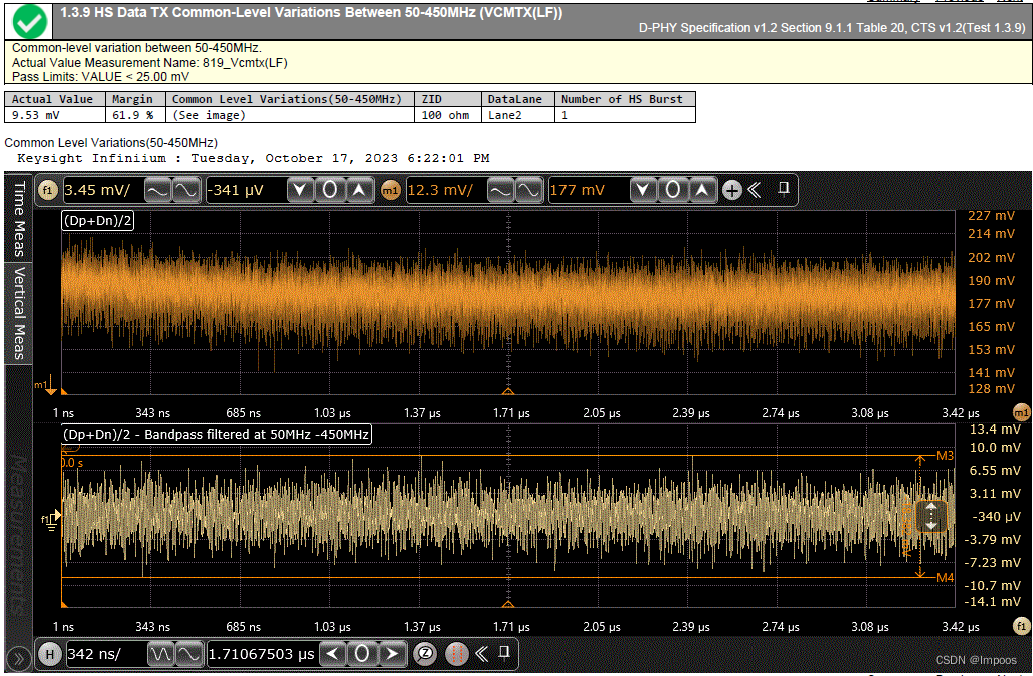

[1.3.9]HS Data TX Common-Level Variations Between 50-450MHz(VCMTX(LF))

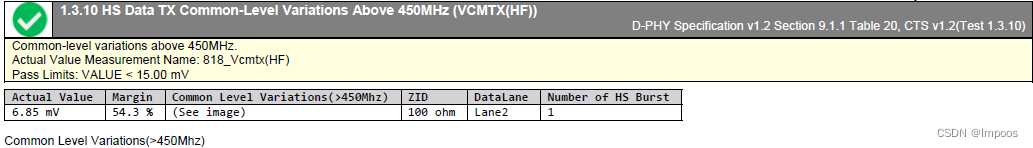

[1.3.10]HS DATA TX COMMON-LEVEL Variations Above 450MHz(VCMTX(HF))

[1.3.11]HS DATA TX 20%-80% Rise Time(tR)[Burst Data]

[1.3.12]HS DATA TX 80%-20% Fall time(tF)[Burst Data]

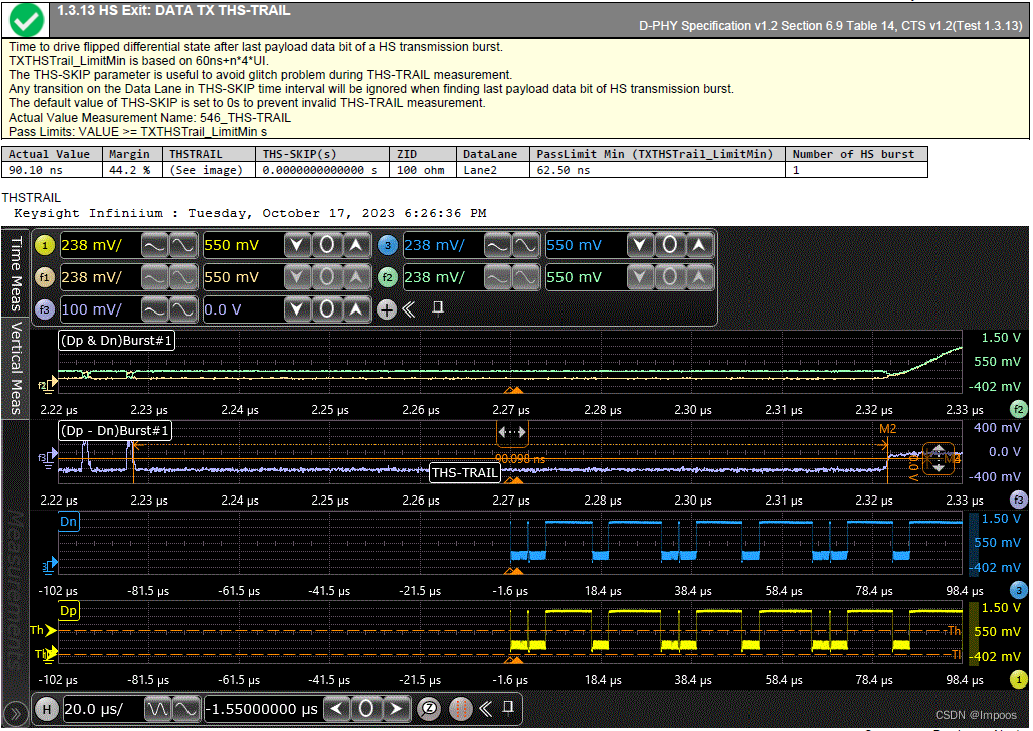

[1.3.13]HS Exit:DATA TX THS-TRAIL

[1.3.16]HS Exit:DATA TX THS-EXIT

[1.4.x]HS Electrical Characteristics- HS CLOCK TX

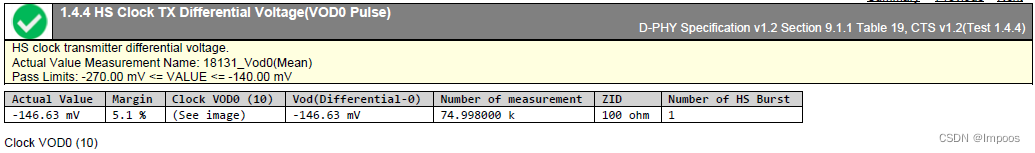

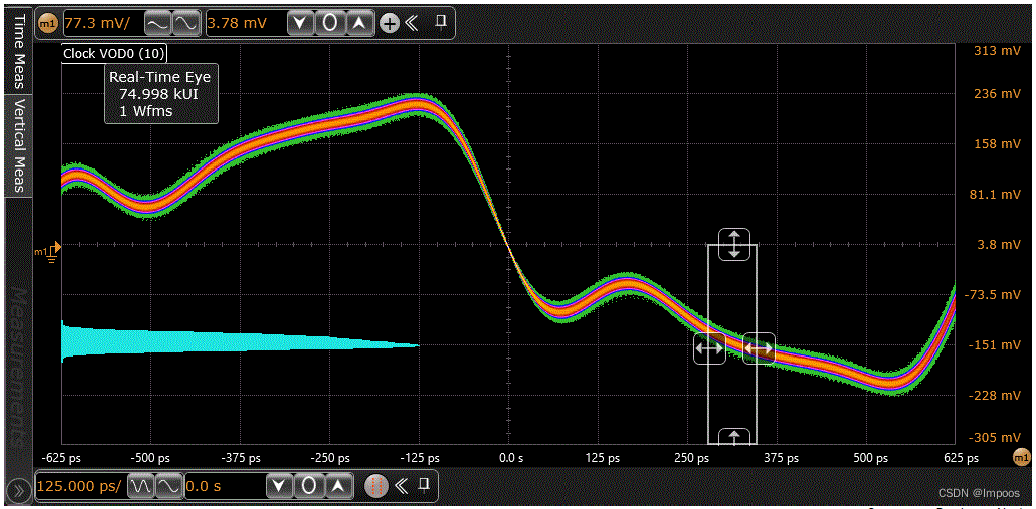

[1.4.4]HS Clock TX Differential Voltage(VOD0/VOD1 Pulse)

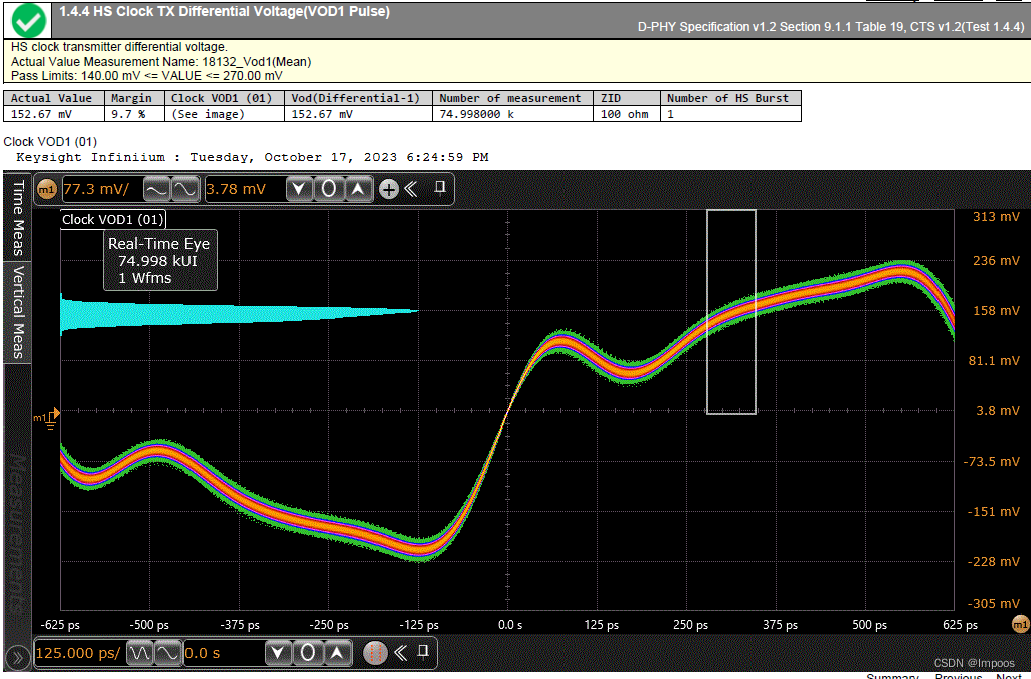

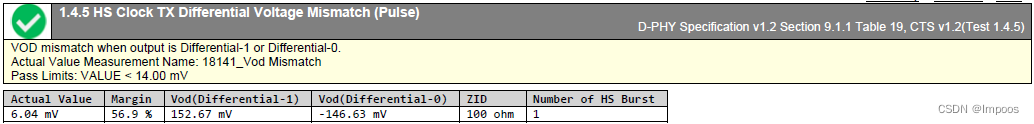

[1.4.5]HS Clock TX Differential Voltage Mismatch

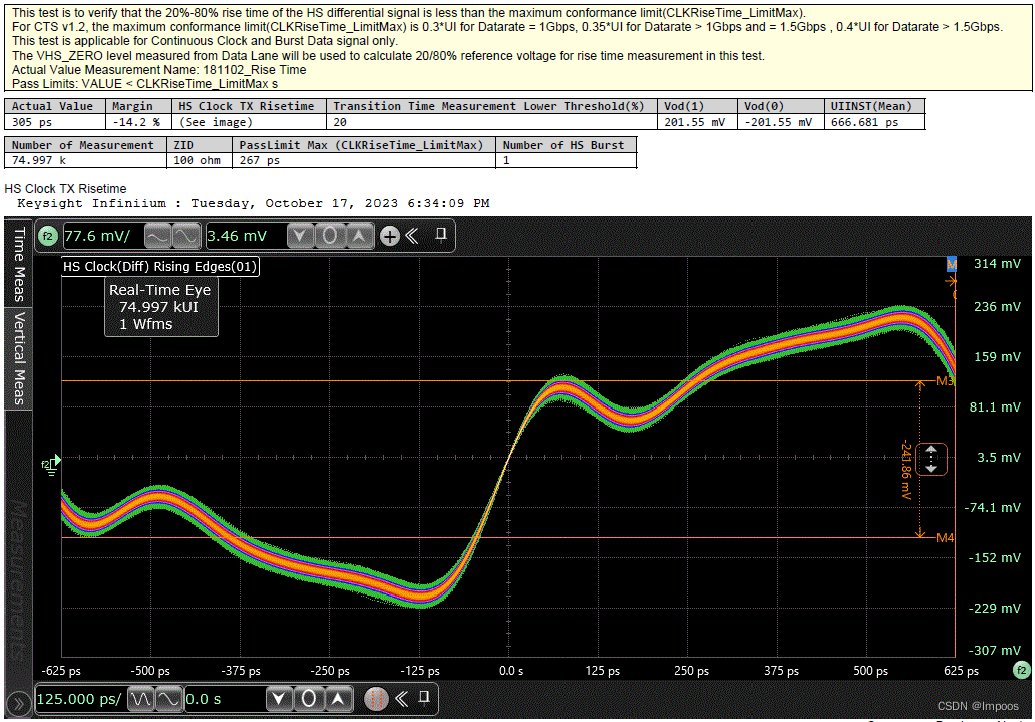

[1.4.11HS Clock TX 20%-80% Rise time(tR)[Continuous Clock,Burst Data]

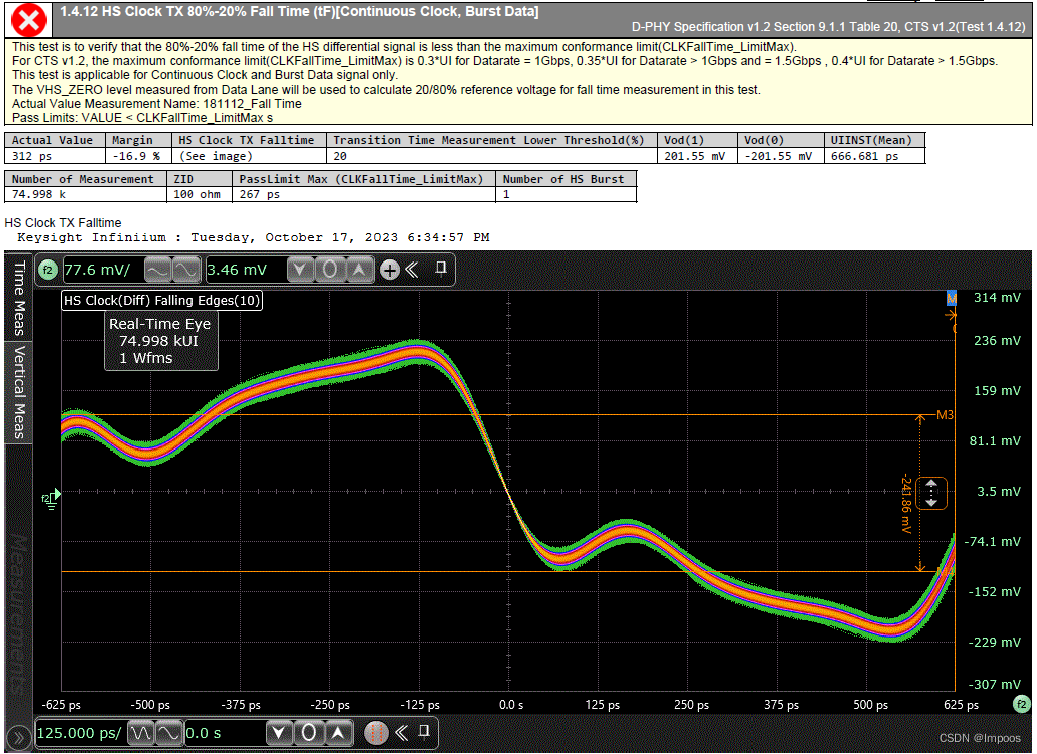

[1.4.12]HS Clock TX 80%-20% Fall time(tF)[Continuous Clock,Burst Data]

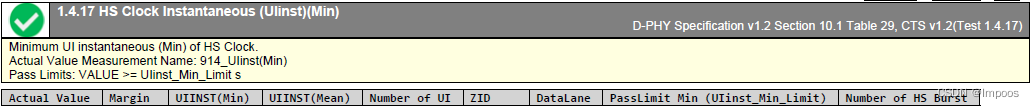

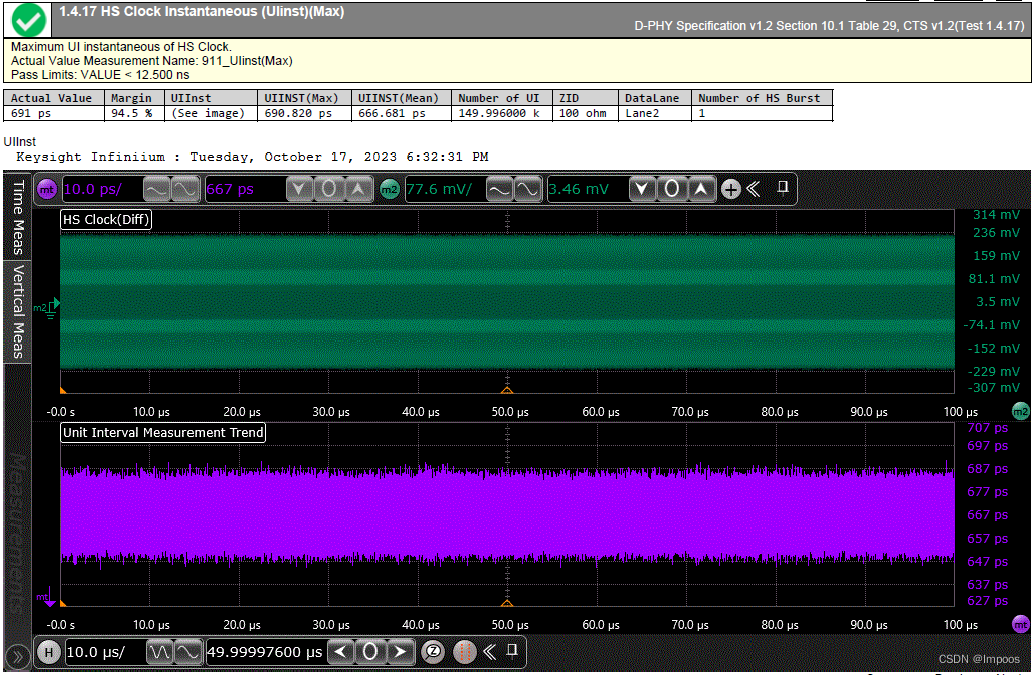

[1.4.17]HS Clock Instantaneous(UIinst)(Min/MAX)

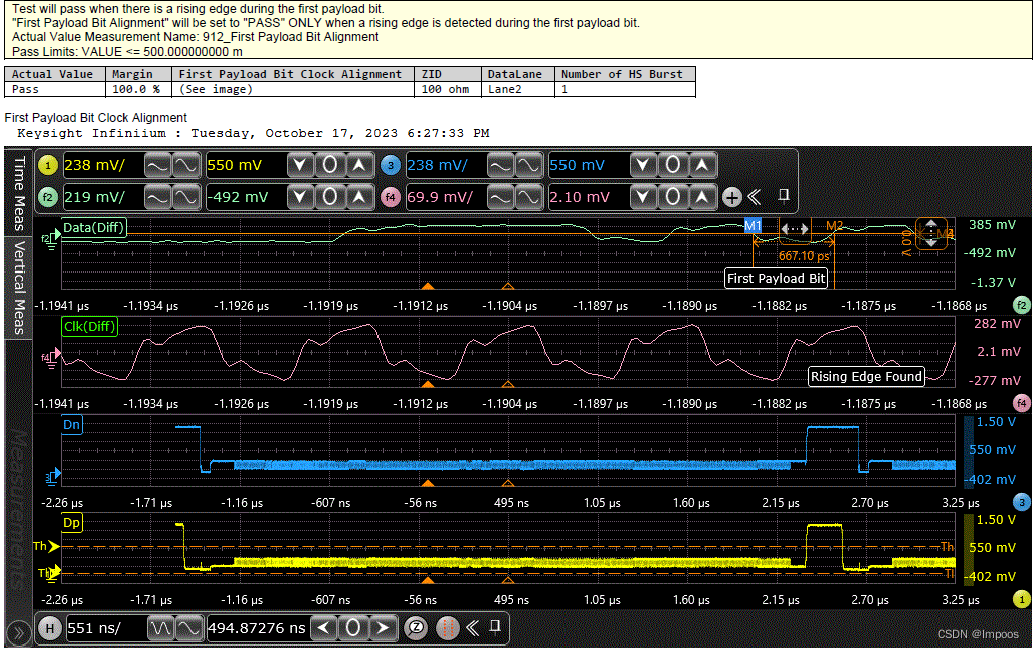

[1.5.3]HS Clock Rising Edge Alignment to First Payload bit

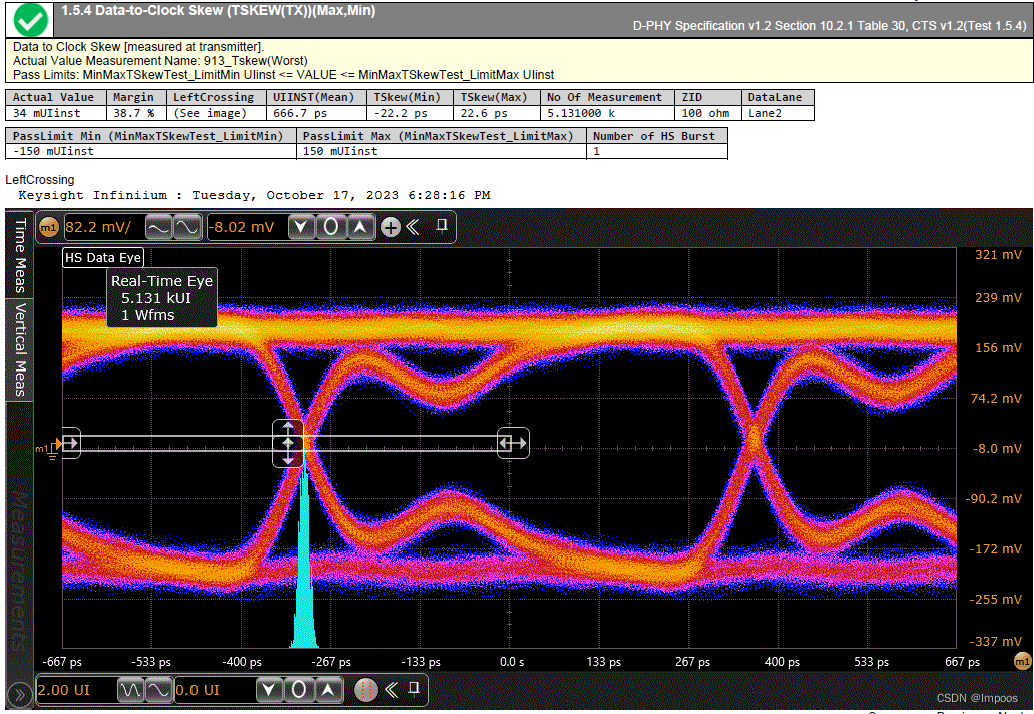

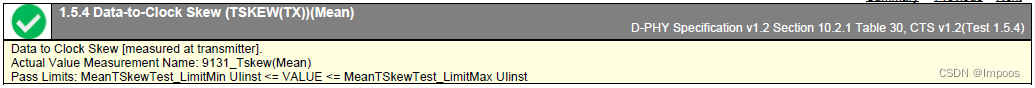

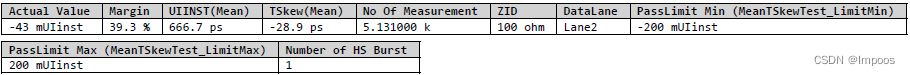

[1.5.4]Data-to-Clock Skew(TSKEW(TX)(Max/Min/Mean))

前言

本文结合测试实例对MIPI D-PHY 一致性测试进行逐项解析

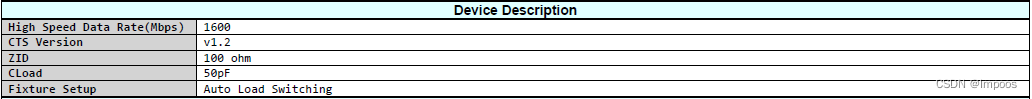

一、测试条件

二、测试标准

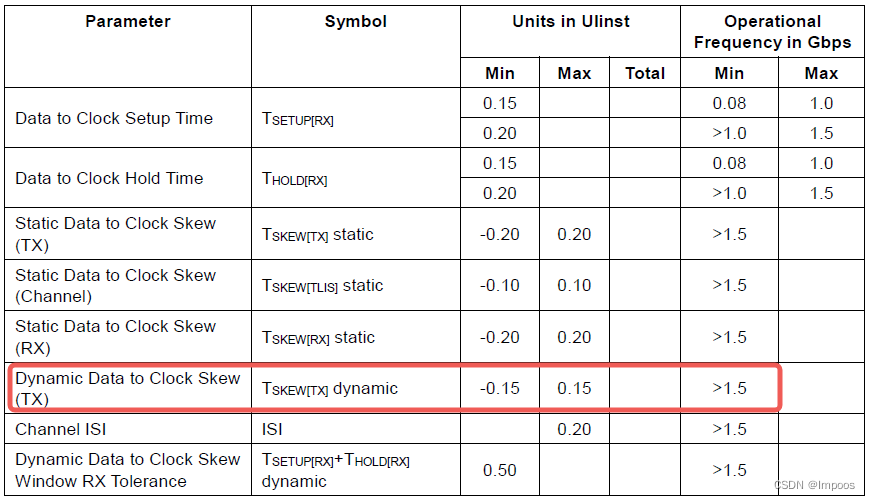

1. Summary

1.3.x,1.4.x分别描述data和clk特性,1.5.x描述data-clk关系

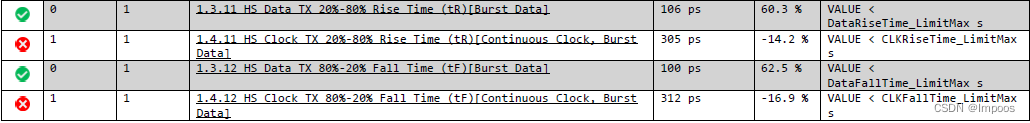

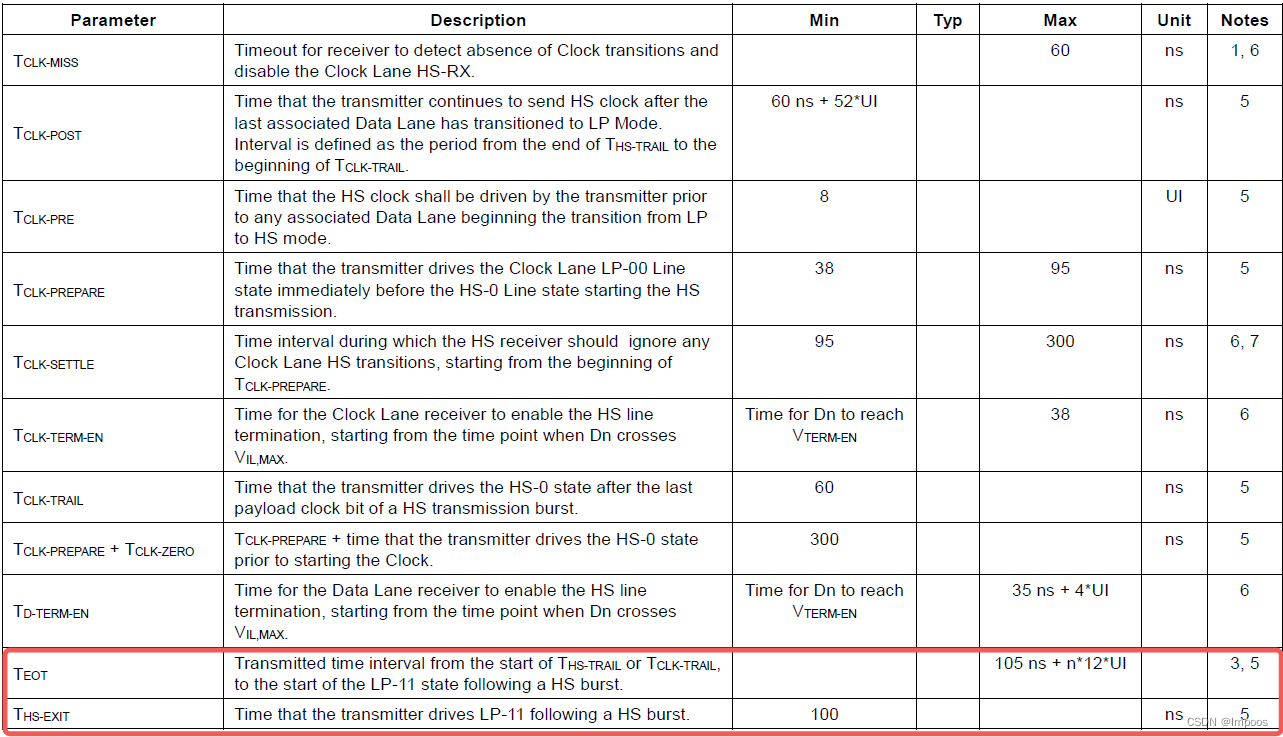

2. HS Entry&Exit

1.3.1-1.3.3 :HS mode SOT 的时序要求

1.3.13-1.3.16:HS mode EOT的时序要求

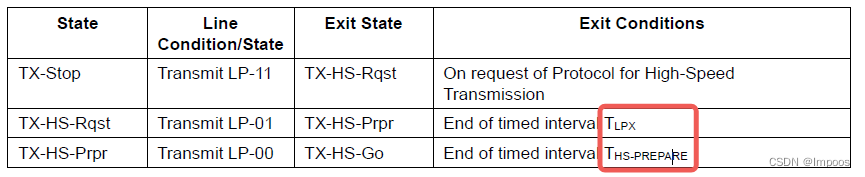

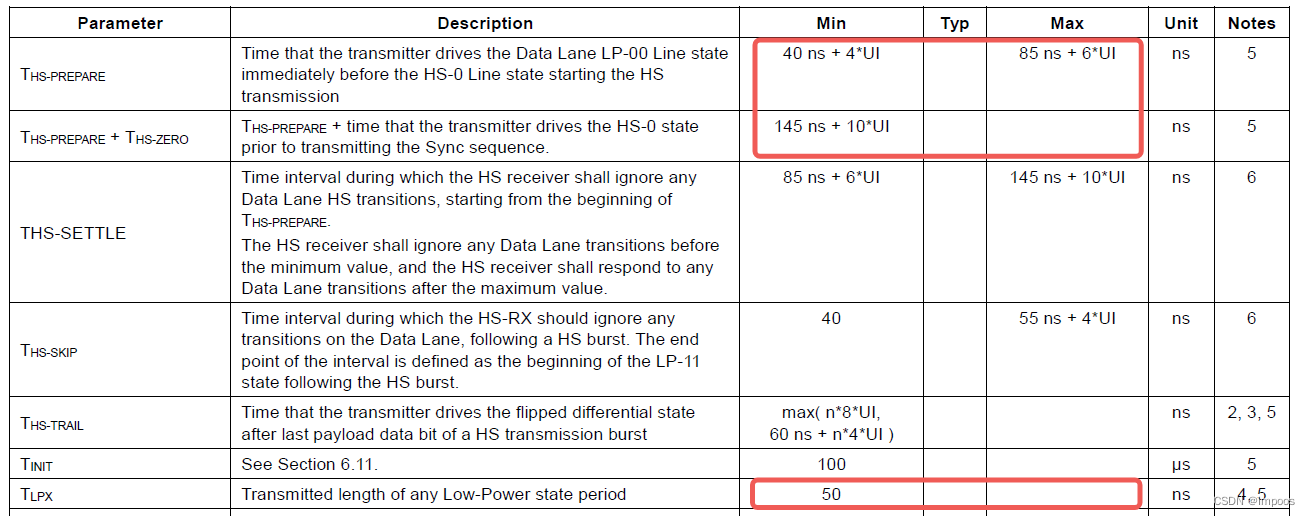

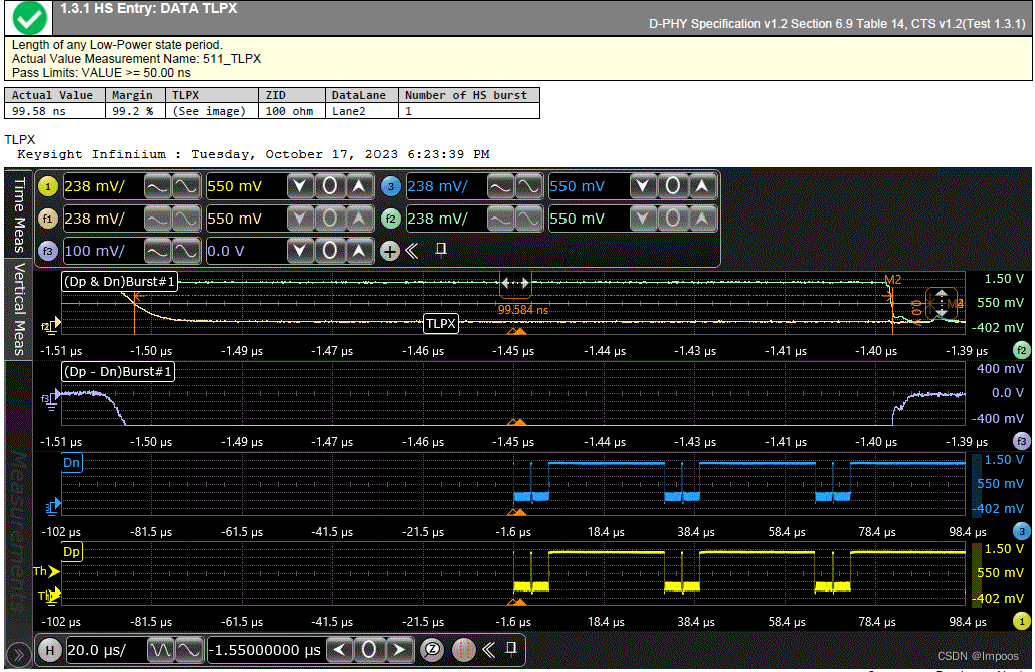

1.3.1:TLPX(LP-01)

LP-01,low power mode ,DP-Low DN-High,TLPX即LP-01的时间间隔

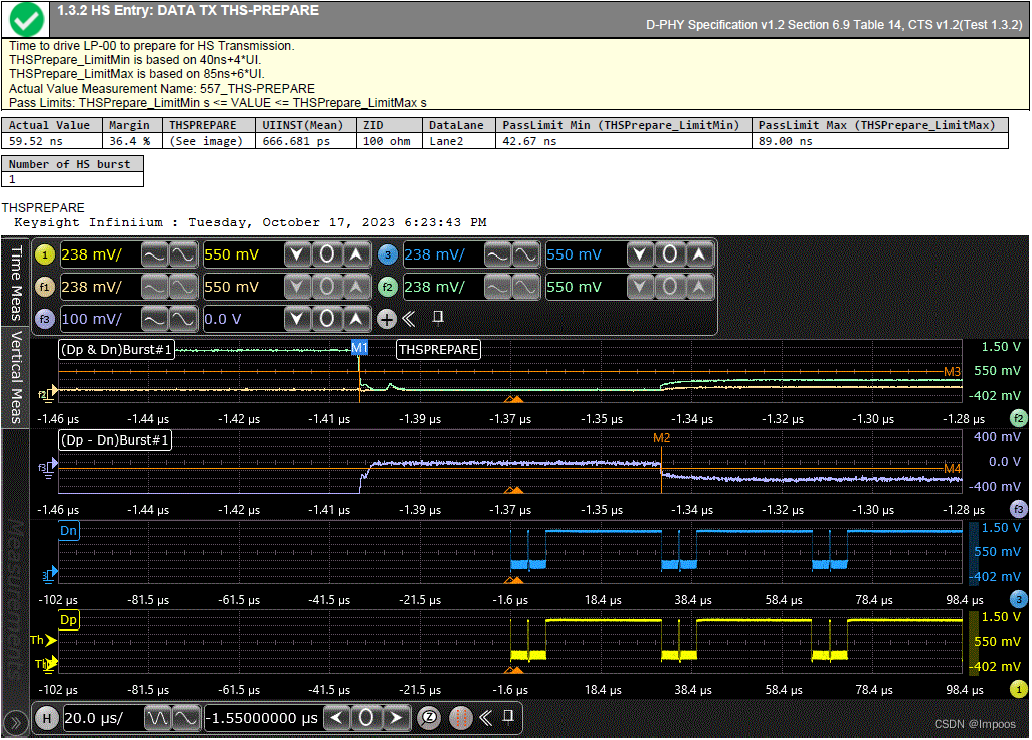

1.3.2:THS-PREPARE(LP-00)

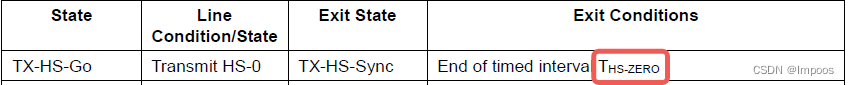

1.3.3:THSPREARE + THS-ZERO(HS-0)

注意此处是LP-00和HS-0的算数和

标准如下

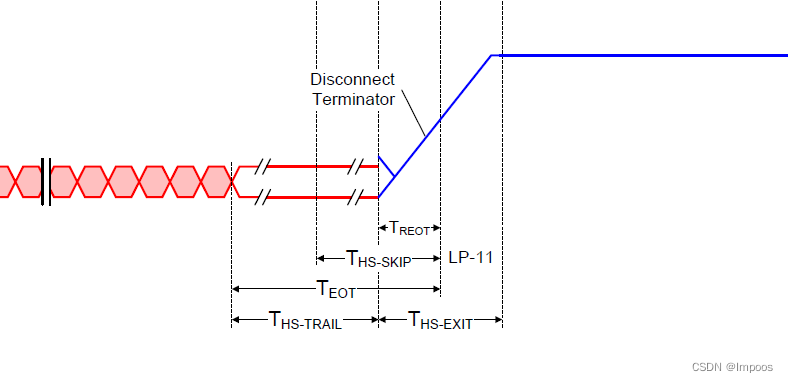

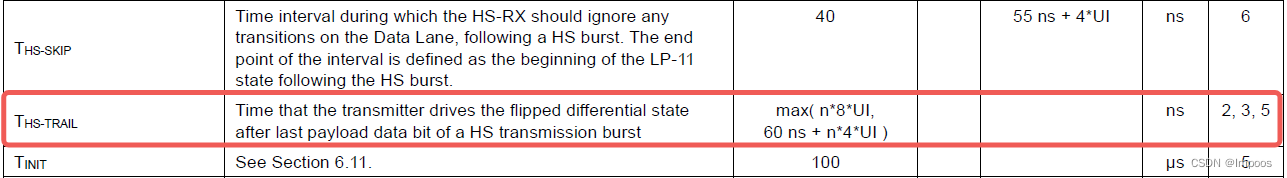

1.3.13:HS-TRAIL

HS mode最后一个payload数据位之后,到翻转差分之前的时间间隔

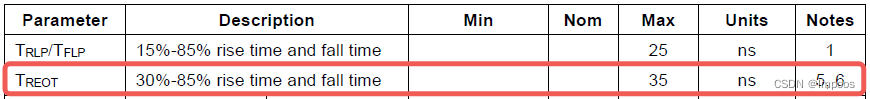

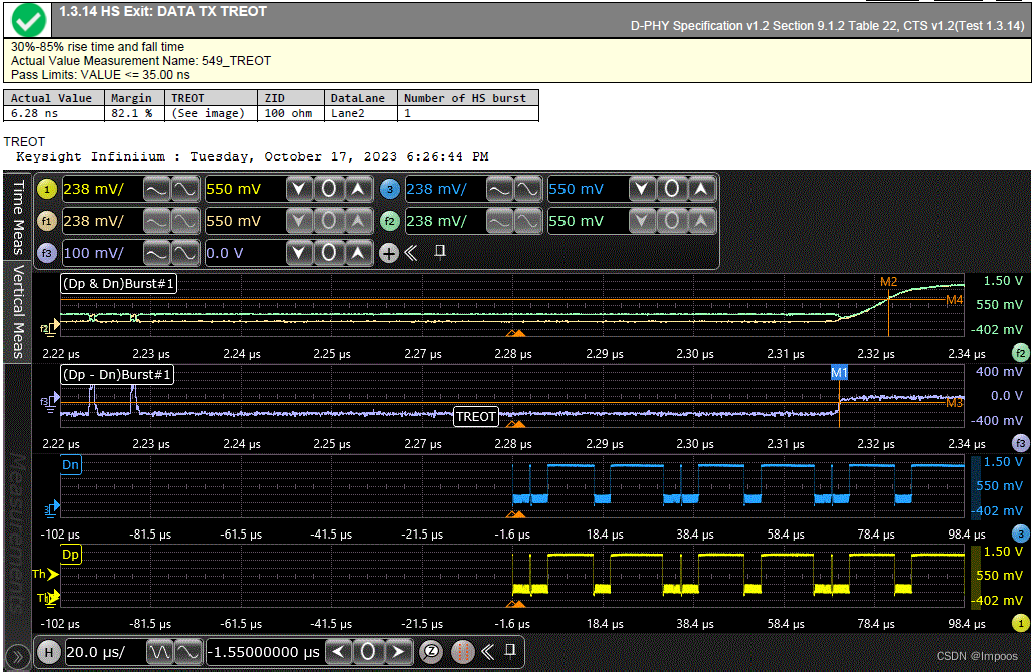

1.3.14:TREOT

进入LP-11的tR(30%-85%)

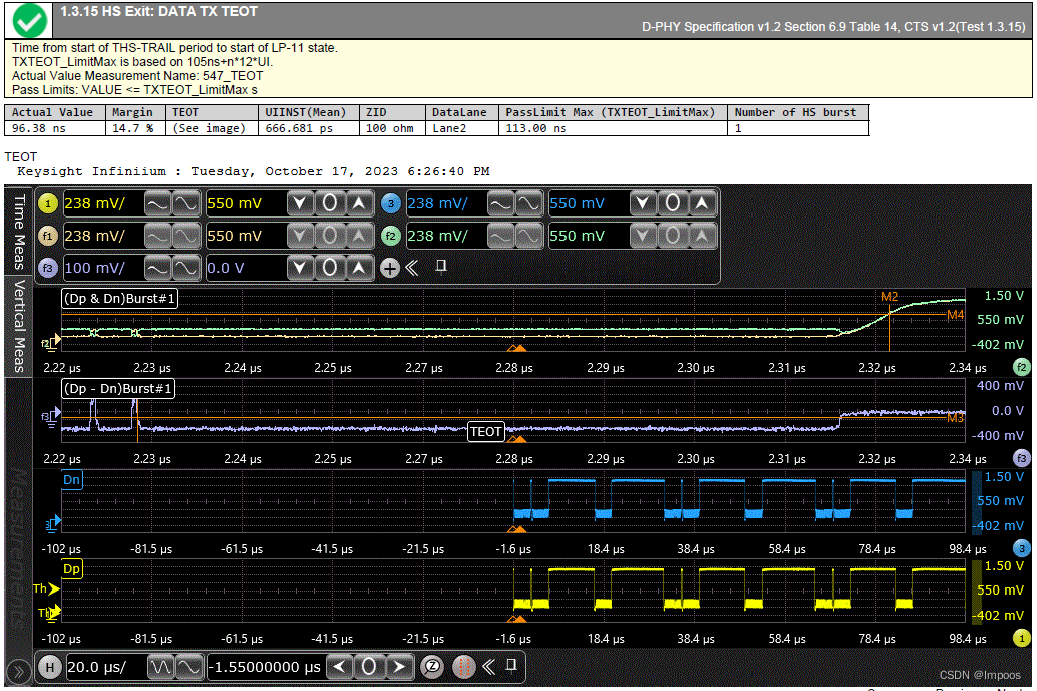

1.3.15:TEOT

TRAIL开始到LP-11的时间间隔

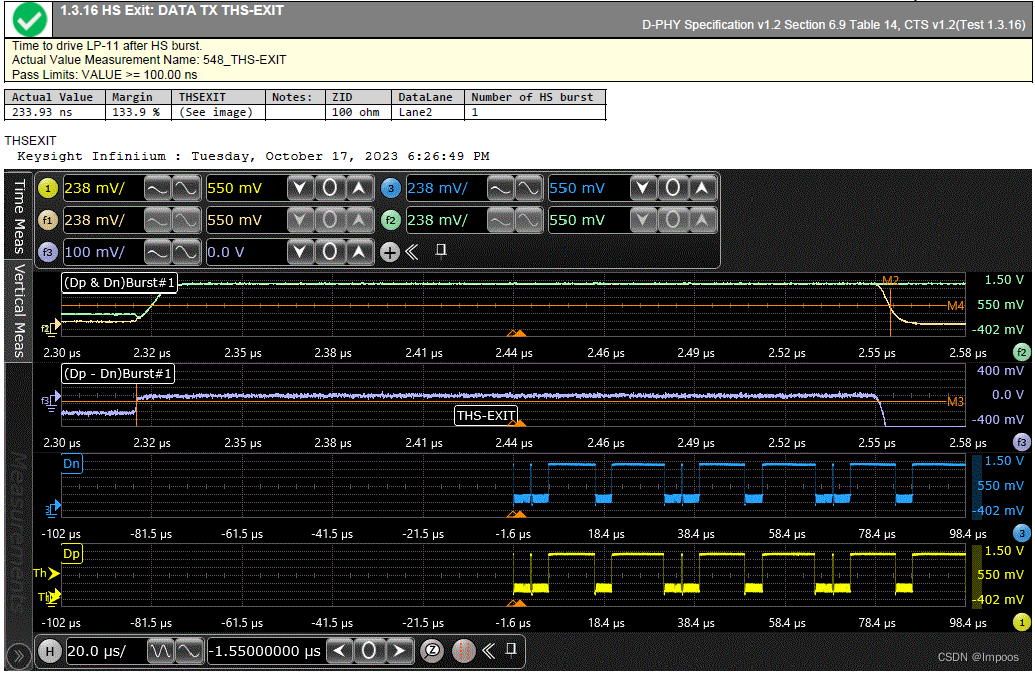

1.3.16:THS-EXIT

LP-11的驱动时间

标准如下

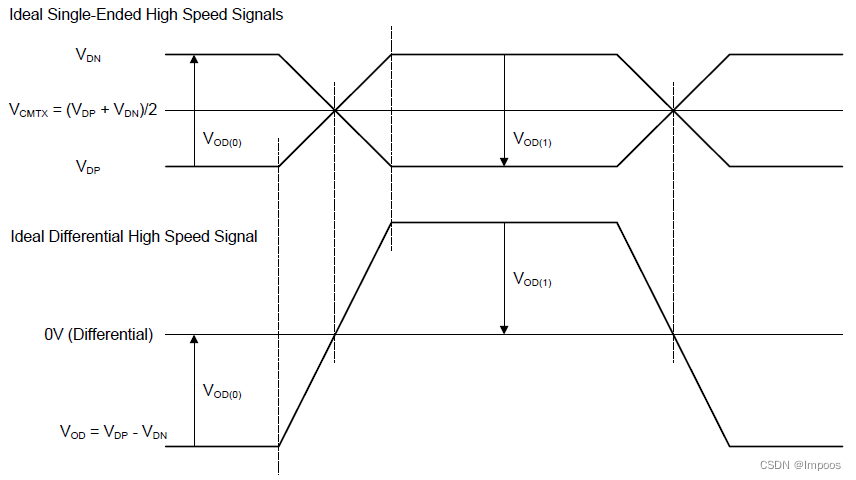

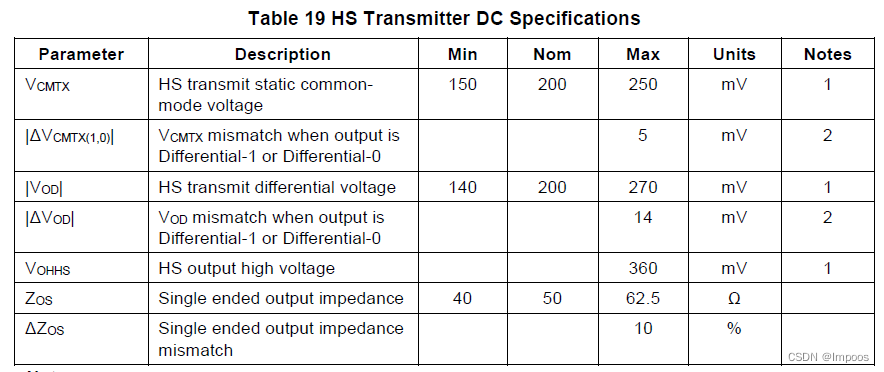

3. HS Data DC Characteristic

1.3.4:VOD=|VDP-VDN|,VOD>0定义为HS-VOD1,VOD<0定义为HS-VOD0

1.3.5:ΔVOD=|VOD1-VOD0|

1.3.6:VOHHS

此处为单端VDP/VDN VOH极值

1.3.7:VCMTX=(VDP+VDN)/2

1.3.8:ΔVCMTX|VCMTX1-VCMTX0|

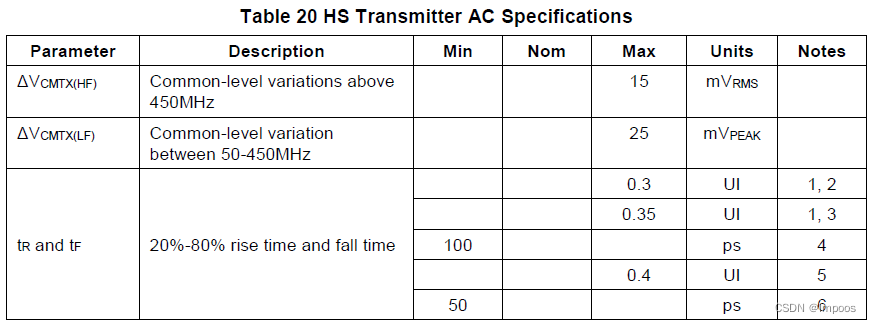

4. HS Data AC Characteristcs

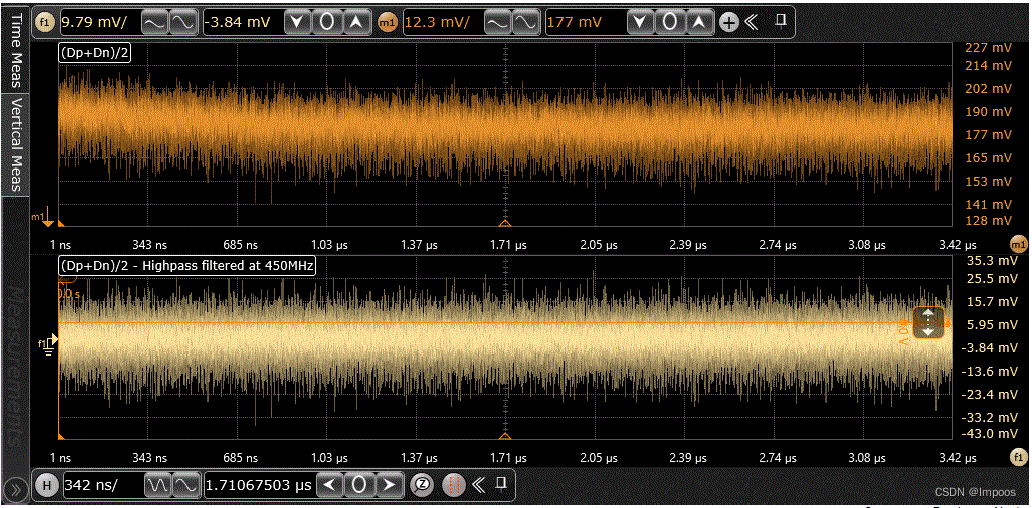

1.3.9-1.3.10:ΔVCMTX(50-450MHz,>450MHz)

不同于1.3.8的静态ΔVCMTX,此项为HS过程所有数据,并通过带通(截止频率50-450MHz)和高通(截止频率450MHz)滤波器提取

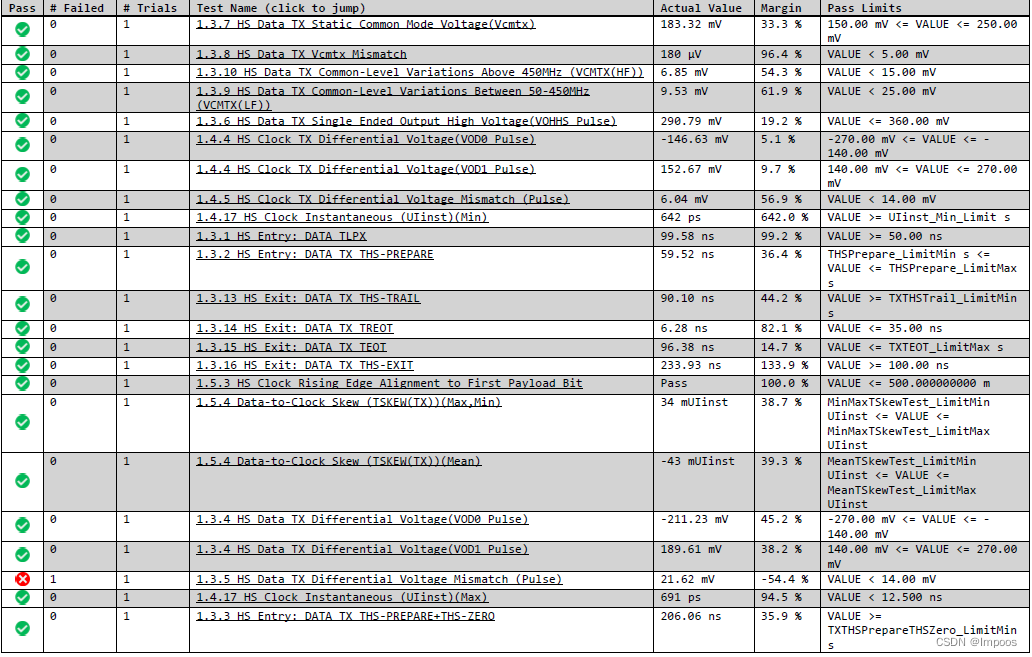

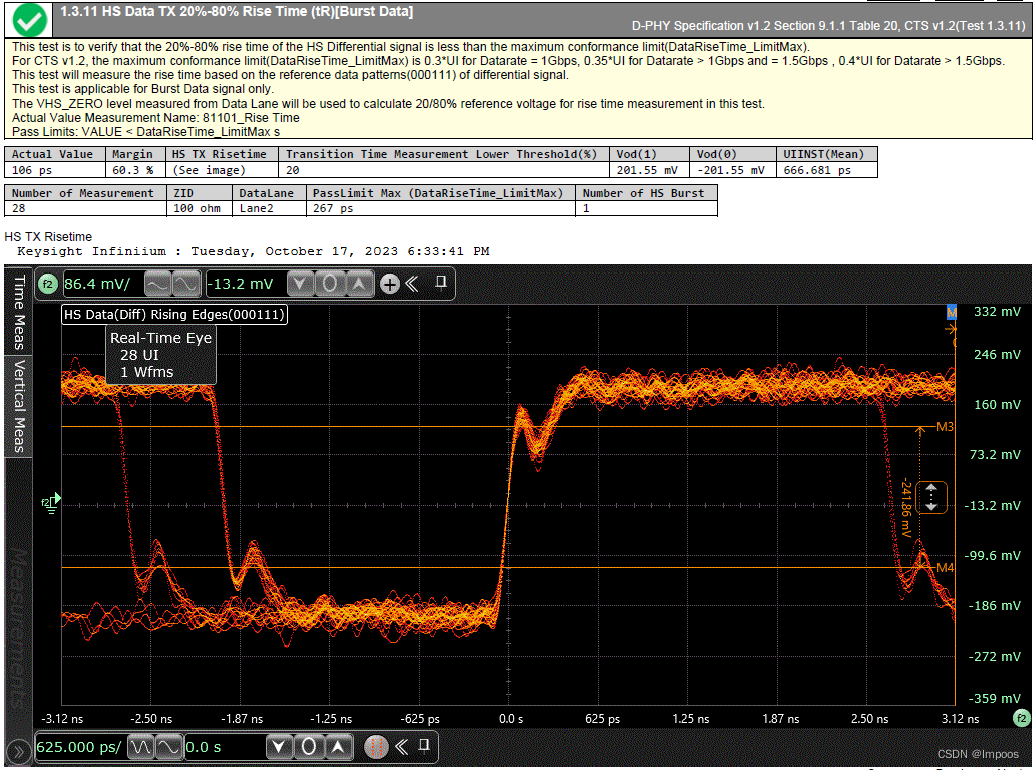

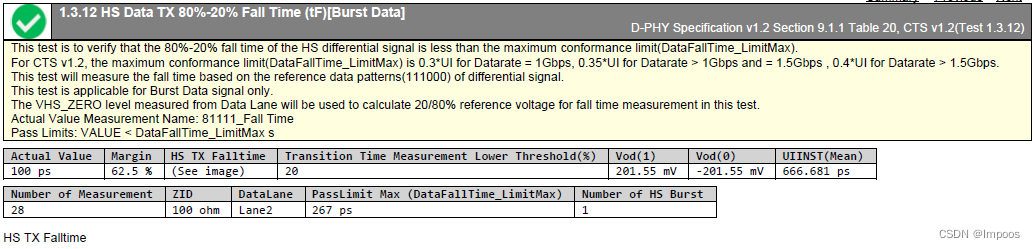

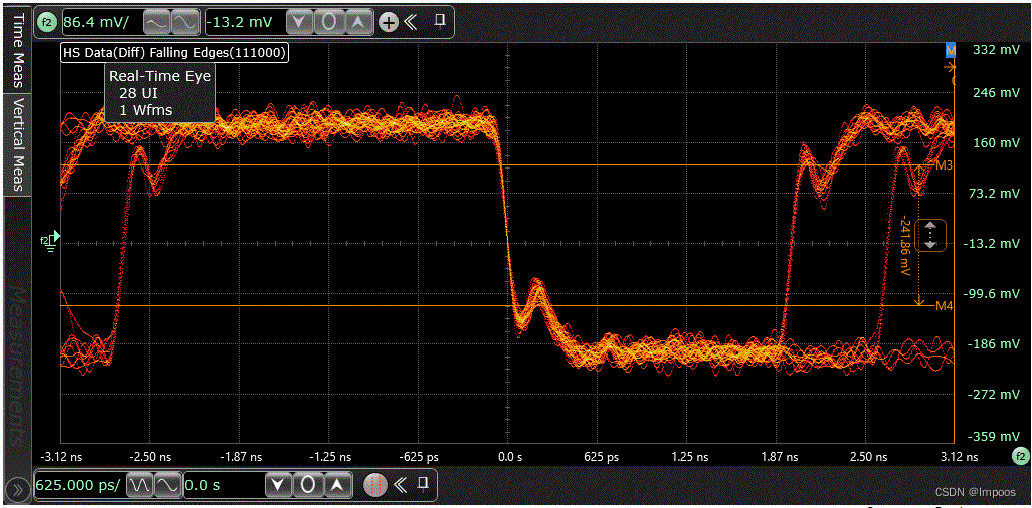

1.3.11-1.3.12:HS data tR(rise time)、tF(fall time)

tR/tF:

<0.3UI(≤1Gbps),<0.35UI(1G-1.5G),<0.4UI(>1.5G)

UI,Unit interval,时间单位,UI=1/(2*fh),fh即时钟频率,由于mipi是双边采样,故*2

为避免过度辐射,同样也有最小值的要求,即

>50ps(≤1Gbps),>100ps(1G-1.5G),>150ps(>1.5G)

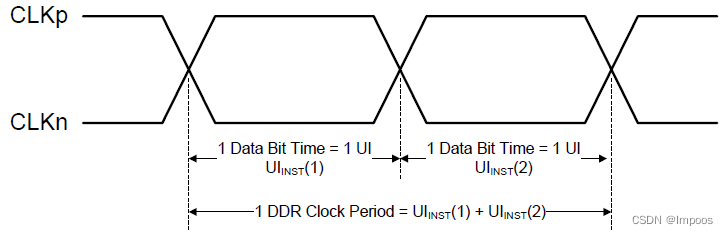

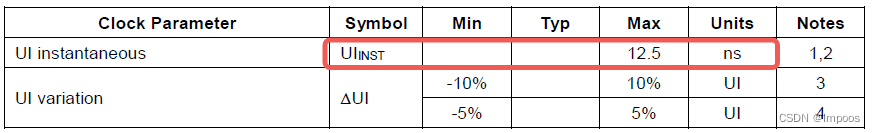

5. HS CLK Characteristic

1.4.4:CLK VOD 要求参考1.3.4

1.4.5:CLK ΔVOD要求参考1.3.5

1.4.11:CLK tR要求参考1.3.11

1.4.12:CLK tF要求参考1.3.12

1.4.17:CLK UIINST要求<12.5ns

UIINST,UI Instantaneous,连续两个瞬时UI即一个时钟周期

6. DATA to CLK Timing

1.5.3 数据的第一个payload需在时钟的上升沿

1.5.4 Data to CLK SKEW

当速率大于1.5Gbps,skew分为静态和动态两类

静态skew可以calibration(后续我们再展开介绍这部分的内容)

动态skew则描述了data和clk之间最大的skew变化

7. 测试实例读图说明

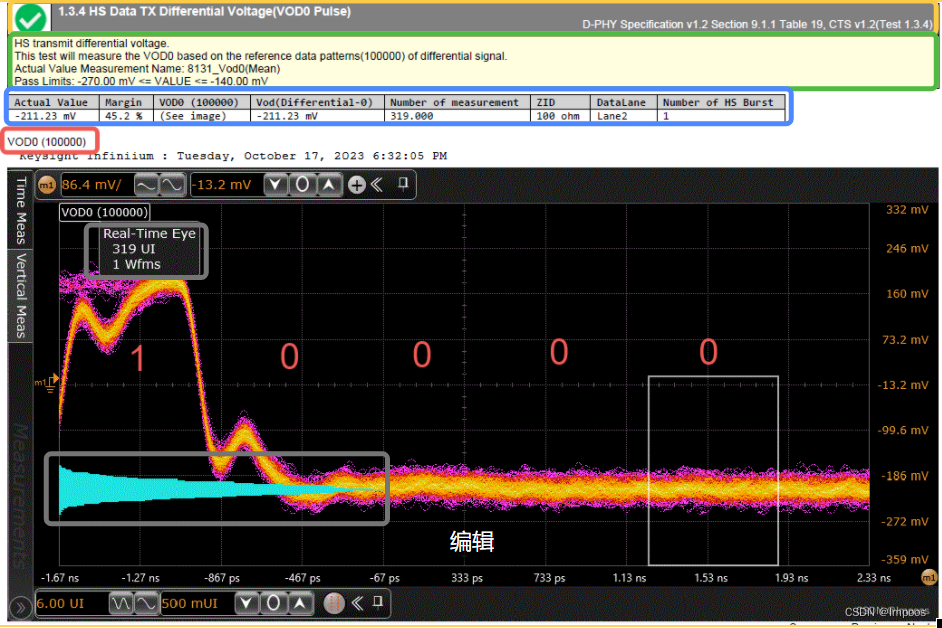

以1.3.4为例,

第一栏,测试项名称及参考标准出处

第二栏,测试项描述及标准

第三栏,测试数据

第四栏及主界面,

→VOD0使用码型“100000”测试,最后一个0即白框位置为判定值

→图中采用直方图(青色)来表达319UI的VOD0分布表现

三、测试实例

[1.3.x]HS Electrical Characteristics- HS DATA TX

[1.3.1]HS Entry:DATA TLPX

[1.3.2]HS Entry:DATA TX THS-PREPARE

[1.3.3]HS Entry:DATA TX THS-PREPARE+THS-ZERO

[1.3.4]HS DATA TX Differential Voltage(VOD0/VOD1 Pulse)

[1.3.5]HS DATA TX Differential Voltage Mismatch(Pulse)

[1.3.6]HS DATA TX Single Ended Output High Voltage(VOHHS Pulse)

[1.3.7]HS DATA TX Static Common Mode Voltage(VCMTX)

[1.3.8]HS DATA TX Static Common Mode Voltage(VCMTX)

[1.3.9]HS Data TX Common-Level Variations Between 50-450MHz(VCMTX(LF))

[1.3.10]HS DATA TX COMMON-LEVEL Variations Above 450MHz(VCMTX(HF))

[1.3.11]HS DATA TX 20%-80% Rise Time(tR)[Burst Data]

[1.3.12]HS DATA TX 80%-20% Fall time(tF)[Burst Data]

[1.3.13]HS Exit:DATA TX THS-TRAIL

[1.3.14]HS Exit:DATA TX TREOT

[1.3.15]HS Exit:DATA TX TEOT

[1.3.16]HS Exit:DATA TX THS-EXIT

[1.4.x]HS Electrical Characteristics- HS CLOCK TX

[1.4.4]HS Clock TX Differential Voltage(VOD0/VOD1 Pulse)

[1.4.5]HS Clock TX Differential Voltage Mismatch

[1.4.11HS Clock TX 20%-80% Rise time(tR)[Continuous Clock,Burst Data]

![]()

[1.4.12]HS Clock TX 80%-20% Fall time(tF)[Continuous Clock,Burst Data]

[1.4.17]HS Clock Instantaneous(UIinst)(Min/MAX)

![]()

[1.5.x]HS DATA-CLOCK TIMING

[1.5.3]HS Clock Rising Edge Alignment to First Payload bit

![]()

[1.5.4]Data-to-Clock Skew(TSKEW(TX)(Max/Min/Mean))

总结

以上,本文就DPHY v1.2 1.6Gbps为例对测试项进行逐个深入解读,不同速率测试项会有所区别(这也是本文测试项不连续的原因)不过思路是一样的

如果本文对你有帮助的话,记得给个三连哟~

4601

4601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?