参考来源:JESD209-5B

在之前的文章中介绍了LPDDR4的相关内容,LPDDR4 Initial可以跳转此处。

从这篇文章开始,会对LPDDR5相关内容进行概要分享:

LPDDR5 Initial → LPDDR5 Command Bus and WCK2CK Training →LPDDR5 Read and Training →LPDDR5 Write and Training → LPDDR5 RFM

因为不同平台的设计细节不同,因此不会对详细细节做出分析,只参考JESD规范和SIPI - Signal Integrity and Power Integrity测试规范进行介绍。

CBT - Command Bus Training

与LPDDR4类似的是,LPDDR5的Command Bus Training内容也是围绕不同频率下的Vref(CA)和SOC端的CA/CS Delay满足Rx Mask要求展开。

关于Vref(CA)和CA/CS Rx Mask Training这部分内容,实际上和LPDDR4很像,只是在信号内容上发生了一些变化,以下是基于JESD209-5B的介绍:

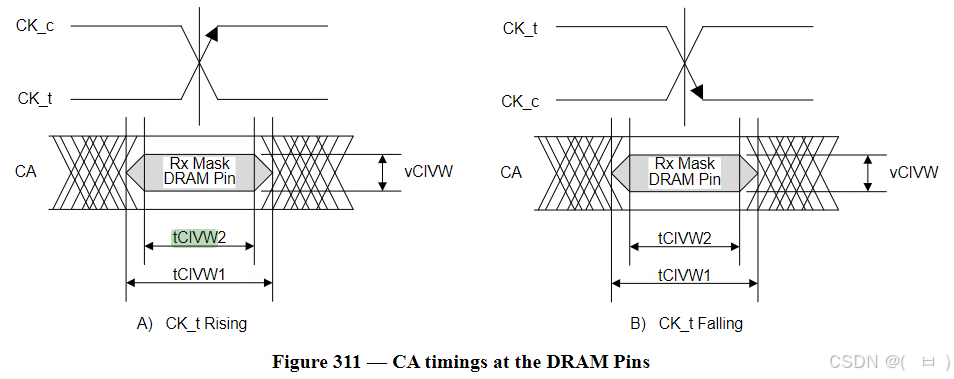

在Rx Mask区域上,LPDDR5是以一个菱形的区域代替了LPDDR4上矩形区域的描述。

tCIVW2保留了矩形Timing范围的有效宽度描述,tCIVW1则是增加了菱形区域的有效宽度描述。

vCIVW在Voltage范围的描述还是和LPDDR4一样的。

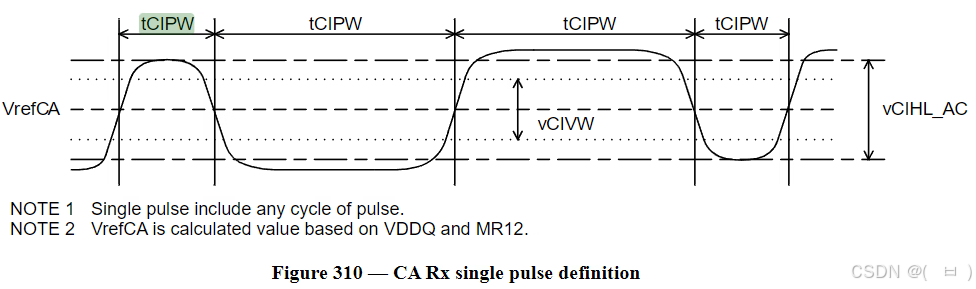

而对于CA输入信号的宽度范围要求tCIPW,也和LPDDR4类似,都需要保证在不同频率周期内足够支撑每次采样。

对于CA输入信号的幅值范围要求vCIHL_AC,不能出现幅值过低,导致无法正确区分高电平信号和低电平信。

而CBT主要变化的是LPDDR5为CBT提供了两种模式,由MR13 OP[6]选择模式,由MR16 OP[5:4]为不同FSP频点Enable CBT。同时也会收到DVFS功能的影响。

两个模式相同的是都通过DQ[7]的高低电平来切换CBT训练的开关,通过CK采样CA/CS数值,通过DQ[6:0]传输采样training的数值。

Mode1

此模式下,通过WCK和DQ[7:0]训练Delay参数。Vref的训练需要退出Mode1,训练好了Vref再重新进入Mode1训练Delay。

下面是DVFS功能关闭下的详细步骤(X为低频,Y为高频):

- 配置MR16 OP[1:0]使能FSP-WR[Y]的写入,MC控制器配置好相关的寄存器参数(latencies, termination, Vref, etc.)

- 配置MR16 OP[5:4]使能CBT[Y],MC控制器发出MRW指令开始CBT

- SOC端驱动DQ[7]为High,DRAM通过WCK采样改变CK频率为High

- 执行CBT,通过DQ[6:0]交互Delay参数训练值

- SOC端驱动DQ[7]驱动为Low,DRAM通过WCK采样结束Training,切换频率为Low,MC控制器发出MRW指令结束CBT

- MC控制器发出MRW指令存储新的FSP-OP[Y]相关Value

- 切换到FSP-OP[Y],进行下一个频点的Training或者正常运行DRAM

下面是DVFS功能开启下的详细步骤(蓝色为DVFSQ Disable,红色为DVFSQ Enable):

- 配置MR16 OP[1:0]使能FSP-WR[Y]的写入,MC控制器配置好相关的寄存器参数(latencies, termination, Vref, etc.)

- 关闭SOC ODT,开启VRCG为High Current Mode

- 配置MR16 OP[5:4]使能CBT[Y],MC控制器发出MRW指令开始CBT

- DQ[7]驱动为High,切换频率并且等待VDDQ降压到0.3V

- VDDQ降压完成后开始执行CBT,通过DQ[6:0]交互Delay参数训练值

- Training完成后,抬升VDDQ到0.5V

- DQ[7]驱动为Low,结束Training ,切换频率为Training之前的值

- 关闭VRCG High Current Mode,MC控制器发出MRW指令存储新的FSP-OP[Y]相关Value

- 切换到FSP-OP[Y],并且开启SOC ODT

- 进行下一个频点的Training或者正常运行DRAM

Mode2

此模式下,需要DMI pin参与,并且无需退出训练就可以调整Delay的同时训练Vref。

因此Mode2的主要区别就是在执行CBT,通过DQ[6:0]交互Delay参数和Vref训练值。

具体就是DRAM通过DMI[0]的上升沿对DQ[6:0]进行采样并更新Vref(CA)值。 其他Training Sequences和Mode1一致。

WCK2CK Training

LPDDR5的WCK2CK就是Write Leveling机制,目的就是为了对齐Clock信号和SOC侧的Strobe信号,在LPDDR4中是DQS,在LPDDR5中就是WCK信号。

WCK对齐CLK之后,才能对Data信号正确采样,因为DDR的机制就是在CLK信号的上升下降边沿发出对应的Data信号,详细内容可以参考此处。

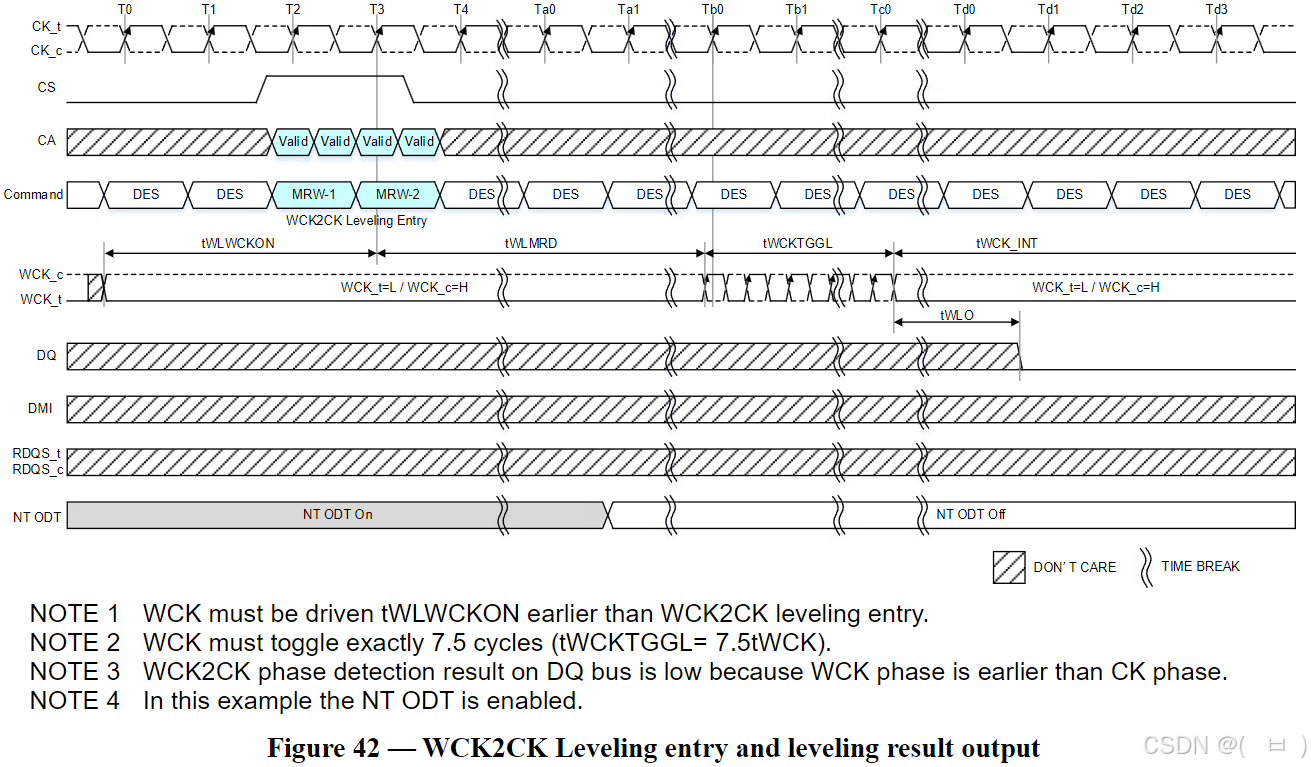

WCK2CK功能由MR18 OP[6] Enable,这个模式下,WCK:CK的比例为2:1,而WCK和CK的对齐信息会通过DQ Bus返回到MC控制器端,DQ Pin上为 Low/High Level,代表WCK早于/晚于CK。

以下是详细过程:

- 驱动WCK_t为Low,WCK_c为High

- 配置MR18 OP[6]为1,进入WCK2CK Leveling Mode

- MC控制端设置等待一定时长(tWLMRD)用于控制器端配置,再开始翻转WCK

- WCK信号翻转7.5周期(tWCKTGGL),DRAM根据CK采样WCK,获取WCK Phase早于还是晚于CK的结果,通过DQ返回到MC

- MC控制器根据DRAM返回结果来增加/减少WCK的Delay

- 再执行上两步不断重复直到Delay数据稳定

- 配置MR18 OP[6]为0,退出WCK2CK Leveling Mode

DCA - Duty Cycle Adjuster && DCM - Duty Cycle Monitor

对于WCK信号,LPDDR5在DRAM端有一个DCA + DCM的硬件模块,用于调整DRAM接收到的WCK的占空比 Duty Cycle。

为什么需要这个硬件模块?因为在LPDDR5的高频场景下,WCK信号的Toggle频率过快,导致传输过程中不同电平信号可能会出现占空比移动,从而影响DRAM端。

影响DRAM的方面包括:

- 基于WCK信号分频出来的RDQS信号的产生质量

- Read时DQ信号Launch

- Write时DQ信号Capture

而DCM就是DRAM端监控WCK信号占空比数据的硬件模块,如果存在占空比偏移,由DCA模块对WCK占空比进行调整。

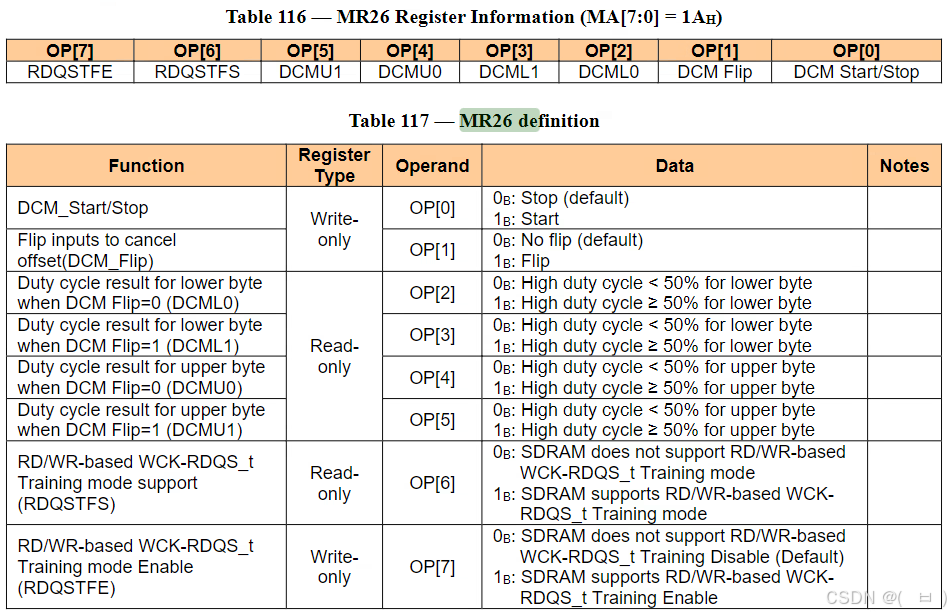

一般这部分Training在CBT和WCK2CK完成之后再进行,相关的操作由MR26寄存器控制。

而当DCM + DCA完成对WCK占空比调整后,会再进行一次WCK2CK操作,防止调整过程中影响了WCK和CK的对齐。

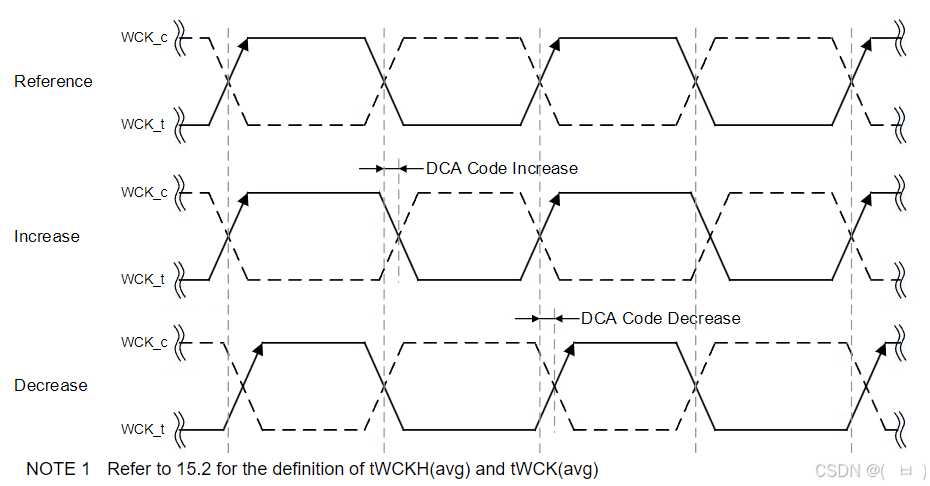

下图是WCK占空比调节的示意图,最终会影响WCK Delay Value:

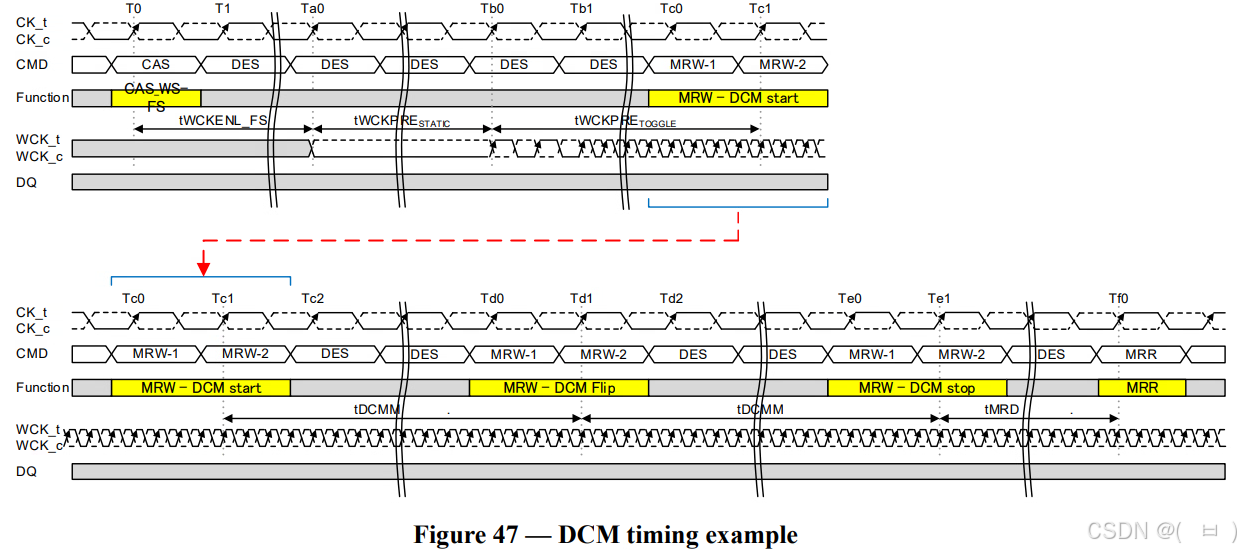

具体的DCM Training步骤如下:

- 配置FSP,让WCK切换到最高频,等待WCK产生稳定Toggle

- MC发出MRW命令,开始DCM

- 等待tDCMM时间,用于DCM完成对WCK占空比的测量

- MC发出MRW命令配置MR26 OP[1],之后MR26 OP[1] value每一次翻转会把当前DCM结果并存储到MR26

- MC发出MRW命令,DRAM也会存储最后一次DCM结果到MR26,结束DCM

- MRR命令读取DCM数值,通过DCA调整Duty Cycle再重复上述过程

具体AC Timing如下:

259

259

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?