参考来源:JESD209-5B

概念

基本概念部分

DVFSC:Dynamic Voltage and Frequency Scaling,LPDDR5针对低功耗场景提出的新功能,分为DVFSC - DVFS Core, Enhanced DVFSC 和 DVFSQ - DVFS VDDQ三种模式。三个模式都是为了能够在不同频率提供不同Power Supply来达到低功耗的目的。DVFSC由MR19 OP[1:0]控制开关,主要就是在低频场景下通过控制VDD2H和VDD2L的开关来实现DRAM Peripheral Circuit Block的供电变化。DVFSC的过程是由FSP+DVS两部分组成。FSP是改变dram工作频率的方法(DFS),改变dram工作电压的方法就是DVS。

FSP(Frequency Set Point):频点

- 在Training阶段,MC控制器会对DRAM不同频率进行Training(具体哪些频率,需要根据具体平台要求和DRAM颗粒支持的范围决定)。

- 保证后续DRAM在使用过程中切换频率时,不需要再对不同频点进行Training之后使用

Link ECC:LPDDR5中ECC机制是面向3200Mbps以上的高频传输场景下的数据异常问题,与LPDDR4不同的是Link-ECC在Write Burst场景下,每128bits数据会产生对应的ECC。

DM: 数据掩码功能,主要用屏蔽不想存入和接收的数据,为了屏蔽不需要的数据,采用了数据掩码(Data I/OMask,简称DQM)技术。通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

DBI(Data Bus Inversion,数据总线翻转):DBI引脚与DBI功能在内存技术中扮演着重要角色,主要用于优化功耗和信号完整性;

- DBI引脚用于指示数据线的反转。当DBI信号为低时,表示数据总线上的数据需要被翻转;当DBI信号为高时,则表示数据总线上的数据无需翻转。

- DBI功能:功耗优化(尽量保持更多的信号线处于高电平状态);信号完整性(更少的“0”到“1”或“1”到“0”的跳变);配置与操作(读写操作可以单独启动DBI功能)

DFE(Decision Feedback Equalization,非线性均衡器):主要是为了解决在高速率模式下,不同数据的电气信号之间容易相互影响,也就是码间串扰ISI的信号失真现象。

Data Copy:LPDDR5通过利用每8Byte数据复制粒度的数据搬运模式来降低LPDDR5 IO和Core的功耗,包括Write和Read Data Copy。

ODT:通过增加终端电阻来吸收信号达到线路末端时产生的余波,防止波形反射。

Non-Target ODT:LPDDR5上,因为颗粒密度更高,信号传输速率更高,导致在多rank场景下,DQ/RDQS/DMI这类高速信号线更容易产生余波。所以提出了Non-Target ODT的功能,通过使能非当前通信Rank上的ODT,来增强吸收高频信号余波的能力,提高信号的稳定性。由MR41配置,MR11使能。

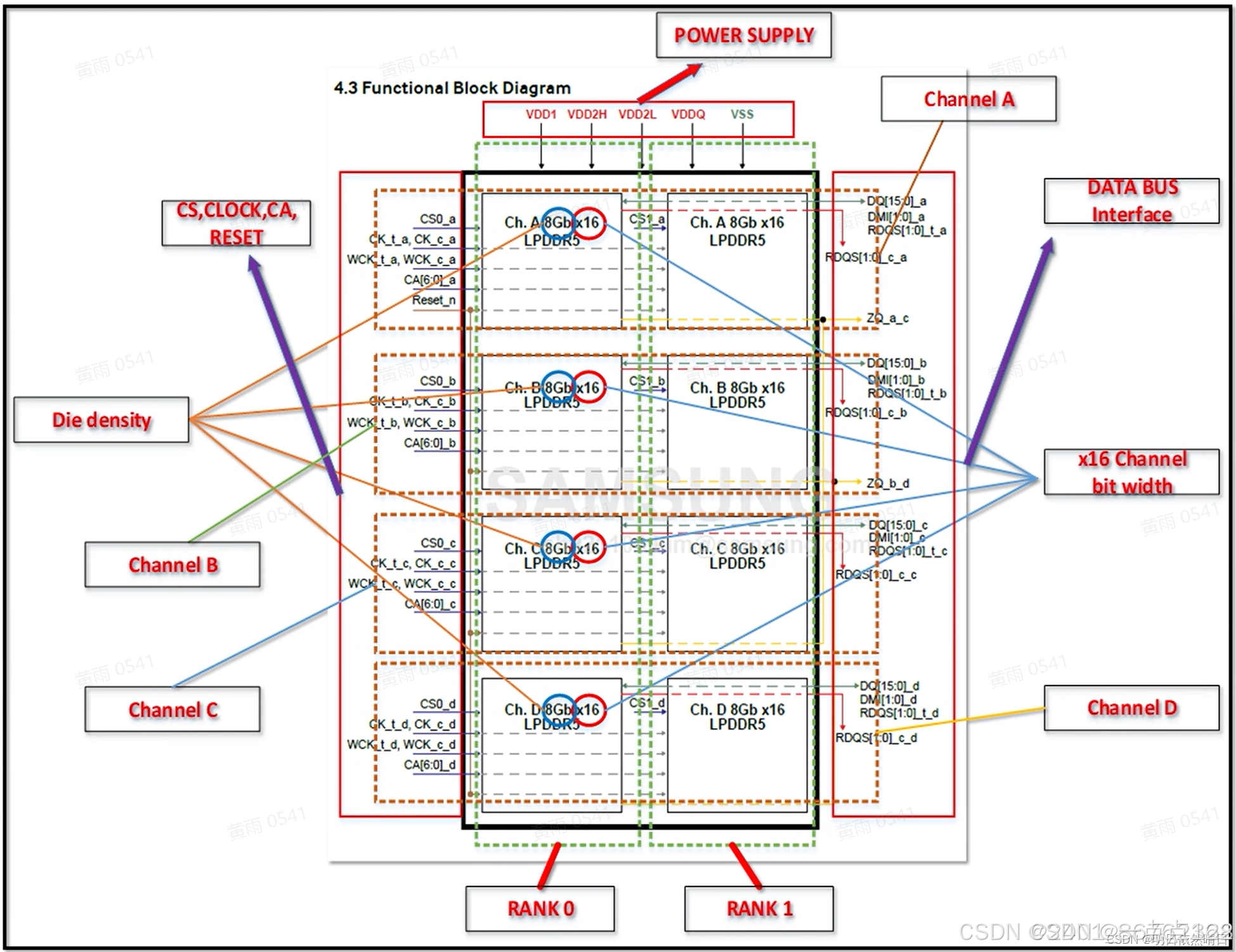

总线信号部分

VDDQ:提供数据输入输出电源1.1~1.8v

VDD1:为内存核心提供电源1.0V或者1.1V

VSS:地

VREFCA:CA参考电压

VDD2H:高压部分,1.8v或者2.5v

VDD2L:低压部分,0.7v或者1.0v

ZQ:ZQ用于校准输出驱动强度,终端电阻作为校准参考。每个管芯有一个 ZQ焊盘。 ZQ 引脚应通过一个 240Ω ±1% 的电阻连接到 VDDQ。

时序参数部分

tFC(short/middle/long):Frequency change time

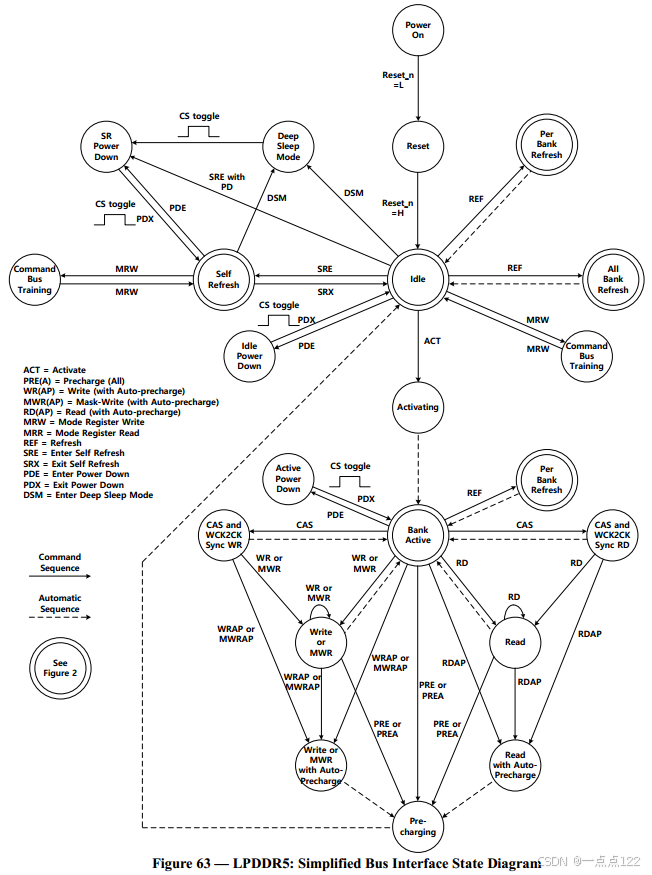

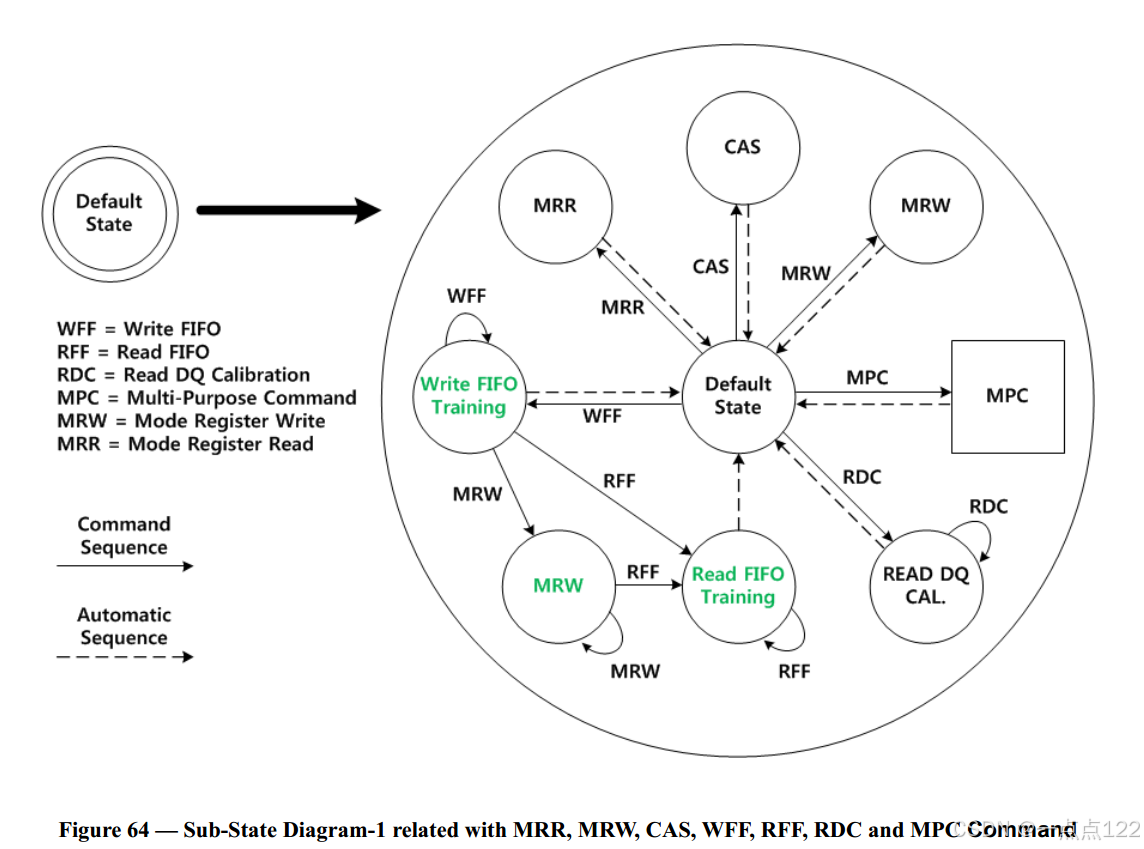

Simplified LPDDR5 State Diagram

Note1:从自刷新状态,器件可以进入掉电、 MRR、 MRW、 MPC 和深度睡眠模式状态。关于自刷新,有关更多信息,请参见 7.5.4。

Note2:在 IDLE 状态下,所有banks都已预充电。

Note3:在 MRW 命令进入训练模式的情况下,状态机不会在训练结束时自动返回 IDLE 状态。关于模式寄存器写入 (MRW),有关详细信息,请参阅 7.6.2 节。

Note4:在 MPC 命令进入训练模式的情况下,状态机可能不会在训练结束时自动返回 IDLE 状态。关于多用途命令 (MPC),有关更多信息,请参阅 7.6.13。

Note5:这个简化的状态图旨在提供可能的状态转换和控制它们的命令的概述。在涉及多个存储体的特定情况下,片上终端的启用或禁用以及一些其他事件未得到完整详细的捕获。

Note6:具有“自动返回”并且可以从多个先前状态访问的状态(例如,来自活动状态或空闲状态的 MRW)将返回到它们启动时的状态(例如,来自空闲的 MRW 将返回到空闲状态) .

Note7:RESET_n 引脚可以从任何状态置为有效,并将导致 SDRAM 进入复位状态。该图显示了从上电应用的RESET 状态作为示例,但该图不应被解释为对 RESET_n 的限制。

Note8:如果需要, Bank Active 状态可以进入“CAS and WCK2CK Sync WR”、 “CAS and WCK2CK Sync RD”状态,用于 WCK-to-CK 同步、 Non-Target ODT 设置或 Burst Length 设置。

Note9:深度睡眠模式状态可以进入自刷新掉电状态切换 CS(VDD2H 电平)。有关深度睡眠模式的更多信息,请参见 7.5.8。

Note10: “Bank Active”到“Per-Bank Refresh”的转换仅指不同的bank,而不是相同的bank。

Note11:仅 MR16 的MRW 命令 OP[1:0]: FSP-WR, OP[3:2]: FSP-OP, OP[6]: VRCG 和 MR14 OP[6:0]:VREF(DQ[7:0]) 和 MR15 OP[6:0]:VREF(DQ[15:8]) 允许从 WRITE FIFO 命令到读取 FIFO 命令。

4 初始化和训练

4.1 Power-up, Initialization and Power-off Procedure

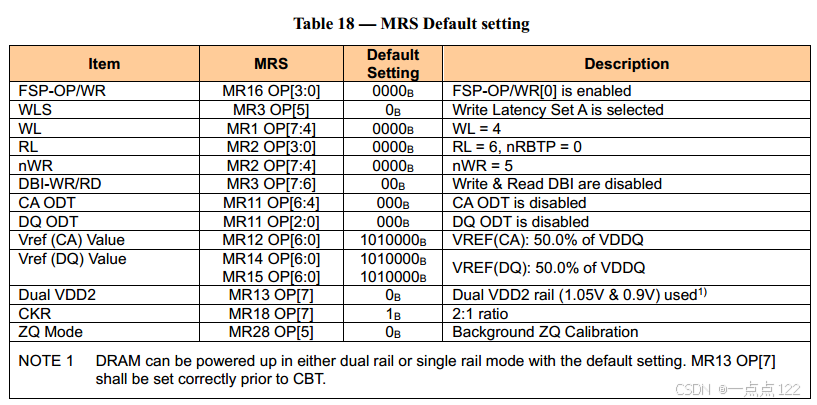

对于上电和复位初始化,为了防止DRAM不能正常工作,以下MR设置的默认值定义为表 18。

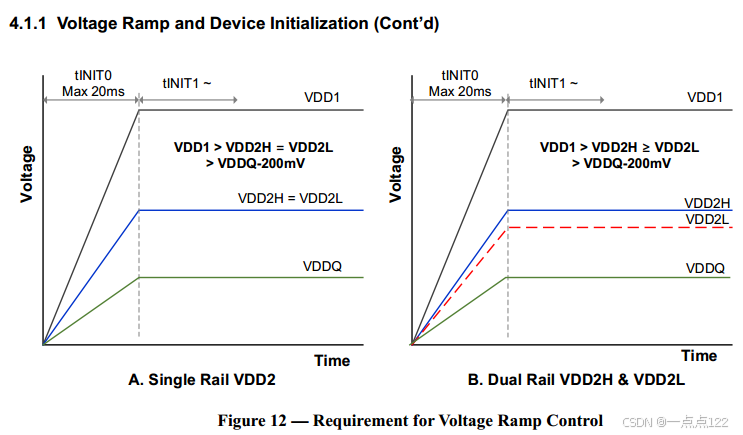

4.1.1 电压斜坡和设备初始化

应使用以下序列为 LPDDR5 SDRAM 上电。除非另有说明,否则这些步骤是强制性的。

1) 通电时(在 Ta 之后),建议 RESET_n 为低电平 (≤0.2 x VDD2H),所有其他输入应介于VILmin 和 VIHmax 之间。

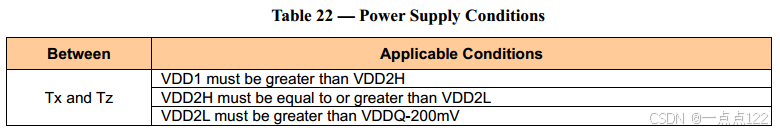

SDRAM 输出保持高阻态,而 RESET_n 保持低电平。电源电压斜坡要求在表 19。 VDD1 必须与 VDD2H 同时或早于 VDD2H。 VDD2H 必须与 VDD2L 同时或早于 VDD2L。 VDD2L 必须与 VDDQ 同时或早于 VDDQ。

2) 在电压斜坡 (Tb) 完成后, RESET_n 必须保持低电平。在电压斜坡期间, DQ、 DMI、 WCK_t和 WCK_c、 RDQS_t、 CK_t、 CK_c 和 CA 电压电平必须介于 VSS 和 VDDQ 之间,以避免闩锁。CS 电平需要等于或小于 ViLPD Max,以防止在 tINIT2 的起点之前发生故障。

3) 从 Tb 开始, RESET_n 必须保持低电平至少 tINIT1(Tc),之后 RESET_n 可以被置为高电平

(Tc)。

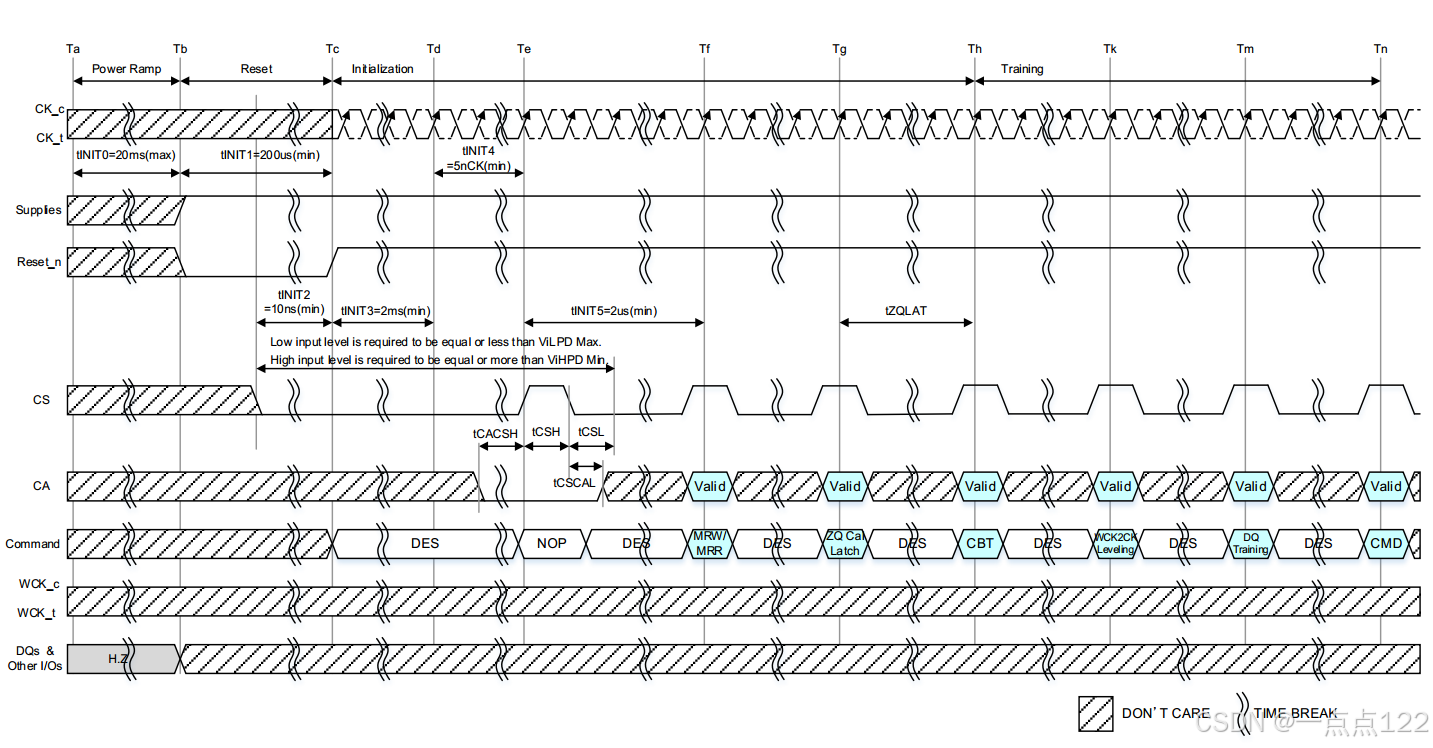

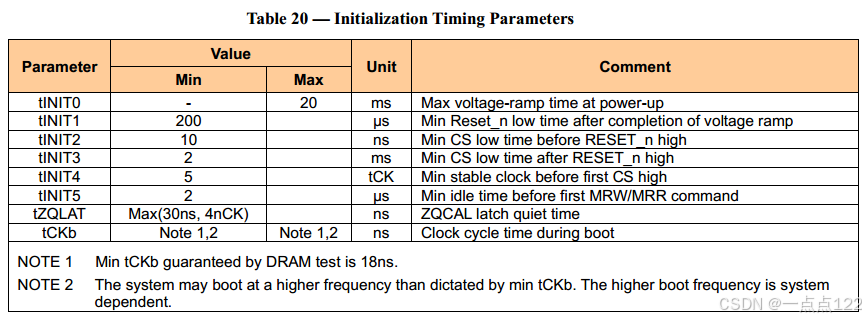

图 13 — 电源斜坡和初始化序列

Note1:训练是可选的,可以在系统架构师的指导下进行。此图中 ZQ_CAL 锁存器之后的训练序列 (Th) 是简化的建议,实际训练序列可能因系统而异。

Note2:当 RESET_n 在 tINIT1 之后变高并在 Td 之前完成时,初始 ZQ 校准由 DRAM 自动启动。

Note3:对于single VDD2 rail system,建议将 MR13 OP[7] 1B 设置为在任何 MRW/MRR 可以在 CBT 之前生效 (Tf) 后立即切换 VDD2 模式。

- 在 Td 之前的初始化/上电序列期间由所有 LPDDR5 芯片自动执行,

- ZQ校准在Td时自动启动;Tf时可改变ZQ的模式,Tg时发送ZQ Latch,Th时完成ZQ;

- Th时进行CBT(VREF(CA)、 CS 和 CA) Command Bus Training;

- Tk时进行WCK2CK leveling;

- Tm时进行DQ 总线training(内部 VREF(DQ)、 WCK 和 DQ);

- Tn时training完成。

4) 几乎在 RESET_n 被置低的同时, CK_t 和 CK_c 需要切换或有效以达到互补电平。

5) CK_t 和 CK_c 需要切换 (Td) 并在 CS 接收到一次切换 (Te) 之前稳定 tINIT4。

6) 在 tINIT4 之后,至少要等待 tINIT5 才能发出任何 MRR 或 MRW 命令 (Tf)。发出第一个命令 (Tf) 时,时钟频率必须在为 tCKb 定义的范围内。在适当配置系统之前,某些AC 参数(例如 tWCKCK)可能会放宽时序(例如 tWCKCKb)。

7) 由于 LPDDR5 初始 ZQ 校准在启动后自动完成,因此应发出 ZQ 锁存命令。在满足 tZQLAT(Th) 后,命令总线(内部 VREF(CA)、 CS 和 CA)应通过发出 MRW 命令(命令总线训练模式)进行高速操作训练。此命令用于校准 SDRAM 的内部 VREF 并将 CS/CA 与 CK 对齐以实现高速操作。 LPDDR5 SDRAM 将在为低速操作配置的接收器上电, VREF(CA) 设置为默认出厂设置。在命令总线训练完成之前,可能无法以高于 tCKb 的时钟速度正常运行 SDRAM。

Note:命令总线训练 MRW 命令使用 CA 总线作为校准数据流的输入,并在 DQ 总线上异步输出结果。看4.2.2 有关如何进入/退出训练模式的信息。

8)命令总线训练后, DRAM 控制器必须执行 WCK2CK 调平。当 MR18-OP[6] 为高电平 (Tk) 时,启用 WCK2CK 调平模式。 WCK2CK 调平进入和退出序列的详细描述见 4.2.5.2。完成WCK2CK Leveling 后, tWCK2CK 即 CK-to-WCK 关系被确定并且 WCK2CK-Sync。将以优化的裕量执行操作。

9) WCK2CK 调平后,应使用命令真值表中描述的训练命令(RD FIFO / WT FIFO / RD DQ 校准)训练 DQ 总线(内部 VREF(DQ)、 WCK 和 DQ)以进行高速操作,并通过发出 MRW 命令来调整 VREF(DQ)(Ti)。 LPDDR5 SDRAM 将在为低速操作配置的接收器和 VREF(DQ) 设置为默认出厂设置的情况下上电。在 DQ 总线训练完成之前,不应尝试以高于 tCKb 的时钟速度正常运行 SDRAM。读取 DQ 校准命令与 FIFO 写入/读取命令一起使用,以在不干扰存储器阵列内容的情况下训练 DQ 总线。有关详细的 DQ 总线训练序列,请参见 4.2.10。

10) 在 Tn, LPDDR5 SDRAM 已准备好正常运行,并准备好接受任何有效命令。此时应写入之前未为正常操作设置的任何更多寄存器。

4.1.2 双 VDD2 轨设置 (MR13 OP[7]) 及其变化

MR13 OP[7](双 VDD2)默认设置为“0B:使用双 VDD2 轨(1.05V 和 0.9V) ”。对于单 VDD2 轨系统(VDD2H 和 VDD2L = 1.05V),建议设置 MR13 OP[7]=1B 以在任何MRW/MRR 可以在 CBT 之前有效 (Tf) 之后立即切换 VDD2 模式。 MR13 OP[7] 应在 CBT 之前正确设置。

在正常操作期间更改 MR13 OP[7] 设置和 VDD2L 电压电平是非法的。在上电和初始化序列之后,有必要执行 RESET 以更改 MR13 OP[7] 和 VDD2L 电压电平。

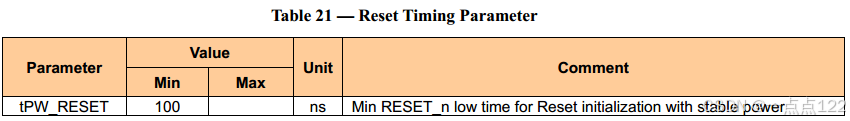

4.1.3 稳定电源复位初始化

在无电源中断初始化时, RESET 需要以下序列。

1)当需要复位时,随时将 RESET_n 置为低于 0.2 x VDD2H。 RESET_n 需要保持最小tPW_RESET。在置低 RESET_n 之前,必须将 CS 拉低 (≤VILPD) 至少 10ns。

2) 重复步骤 4 到 9在4.1.1中.

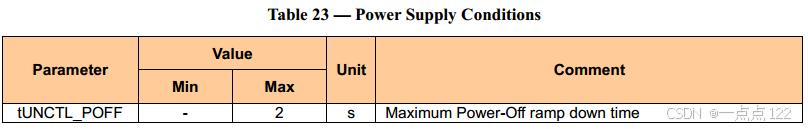

4.1.4 断电顺序

关闭 SDRAM 需要以下过程。

断电时, CS 必须保持低电平 (≤VILPD),所有其他输入必须介于 VILmin 和 VIHmax 之间。SDRAM 输出保持高阻态,而 CS 保持低电平。在电压斜坡期间, DQ、 DMI、 WCK_t 和 WCK_c、RDQS_t、 CK_t、 CK_c 和 CA 电压电平必须介于 VSS 和 VDDQ 之间,以避免闩锁。在电压斜坡期间, RESET_n 输入电平必须介于 VSS 和 VDD2H 之间,以避免闩锁。

Tx 是任何电源低于指定最小值的点。

Tz 是所有电源都低于 300mV 的点。 Tz后, SDRAM断电。

4.1.5 不受控制的断电顺序

当发生失控断电时,必须满足以下条件:

在 Tx 时,当电源低于指定的最小值时,必须关闭所有电源并且所有电源电流容量必须为零,系统中剩余的任何静电荷除外。

在 Tz(所有电源首先达到 300mV 的点)之后, SDRAM 必须断电。在 Tx 和 Tz 之间,电源之间的相对电压不受控制。 VDD1、 VDD2H 和 VDD2L 必须在 Tx 和 Tz 之间以低于 0.5V/μs 的斜率下降。

在 SDRAM 的整个生命周期中,不受控制的断电序列最多可发生 400 次。

4.2 training

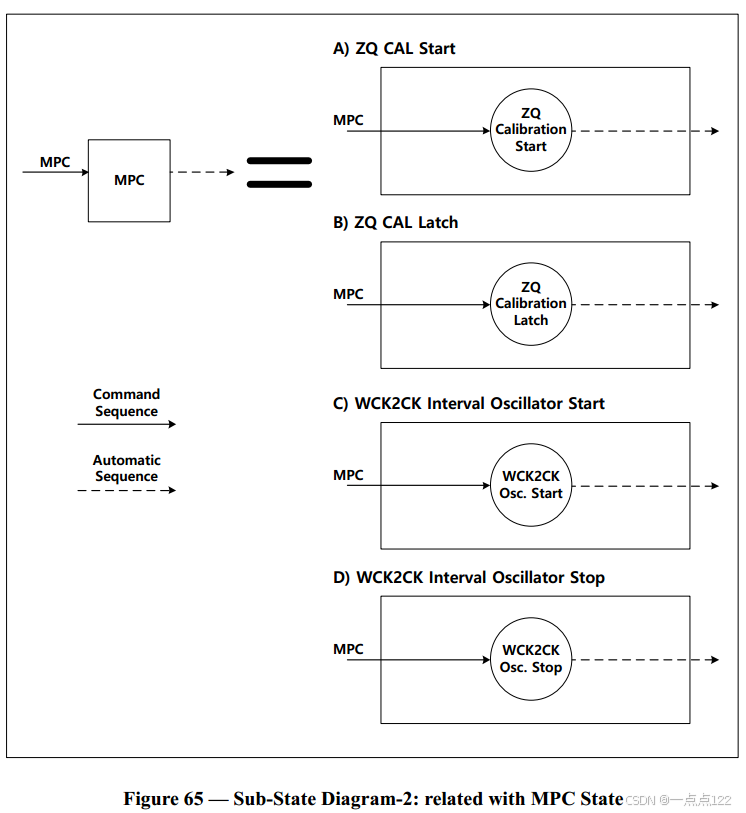

4.2.1 ZQ 校准

支持两种 ZQ 校准模式——后台校准 or Command-Based 校准。在后台校准模式下,输出驱动器和CA/DQ ODT 阻抗跨过程、温度和电压的校准发生在设备操作的后台,旨在消除通道之间的任何协调需求(即,它允许通道独立性) 在一个通道内。系统还可以选择Command-Based的校准模式,其运行方式类似于 LPDDR4 设备。通过设置 MR28 OP[5]=1B 选择Command-Based的校准模式。

由于系统环境的变化导致 LPDDR5 SDRAM 电压和/或温度发生变化,因此可能需要重新校准 ZQ。ZQ 校准只能在 VDDQ 电压设置为标称 0.5v DC 或更高时执行(即,当 DVFSQ 未激活时)。在后台校准模式下,当 VDDQ 设置为低于 0.5v 的标称 DC 电平时或当 VDDQ 在电平之间转换时(即,当 DVFSQ 处于活动状态时),应通过内存控制器设置 ZQ 停止来停止校准。在基于命令的模式下,除非设置了 ZQ 停止,否则当 DVFSQ 处于活动状态时, ZQCal 启动命令是非法的。看4.2.1.2 了解更多信息。更改 CA ODT 值 (MR11-OP[6:4]) 和/或 DQ ODT 值 (MR11-OP[2:0]) 不会改变现有的重新校准方案,因此无需立即重新校准。

4.2.1.1 上电和初始化期间的校准

ZQ 校准在 Td 之前的初始化/上电序列期间由所有 LPDDR5 芯片自动执行,如中所示图 13.无论ZQUF 的状态如何,都应在 Tg 或之后向所有 LPDDR5 芯片发出 ZQCal Latch 命令。 ZQ 校准模式选择可以在 Tf 之后随时更改。

有关更改 ZQ 校准模式的更多详细信息,请参阅4.2.1.1.7.

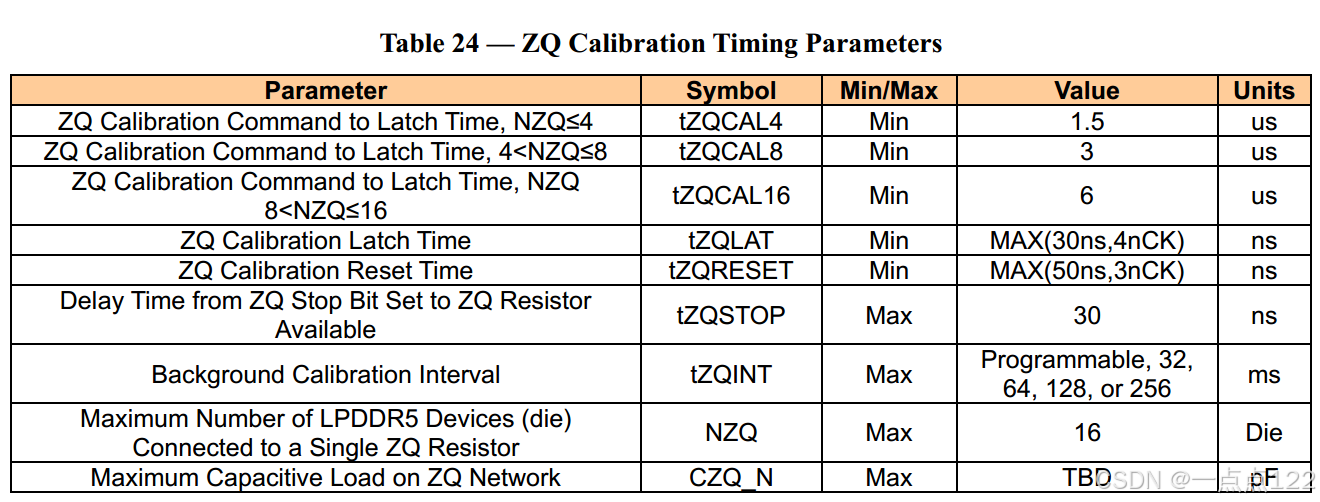

看表 24用于校准延迟和时序。

置位 ZQ Reset 会将校准值设置为其默认设置。

启用 ZQ Stop 后, ZQ Source可供其他设备使用。看4.2.1.2 了解更多信息。

在 Command-Based的校准模式下,当 MR28 OP[1]=1B 时, ZQCal Start 命令将被忽略。

ZQ Interval 和 ZQ Mode MR 设置仅适用于 ZQ Initiator die。 ZQ Target die 将忽略这些设置。

上电初始化和复位序列完成后, ZQUF MR4 OP[5]=0B。

在 Command-Based的校准模式下,只需向 ZQ Initiator die 或 dice 发出 ZQCal Start 命令即可保持精确校准。非 ZQ Initiator die 接收到的 ZQCal Start 命令将被忽略。所有与接收有效ZQCal Start 命令的 ZQ Initiator die 共享 ZQ 资源的 die 都将被校准。在满足 tZQCAL4、tZQCAL8 或 tZQCAL16 之后, ZQCal 锁存器命令可以发送到这些管芯中的每一个。

具有多个 ZQ 引脚的 LPDDR5 封装可能包含多个 ZQ Initiator die。

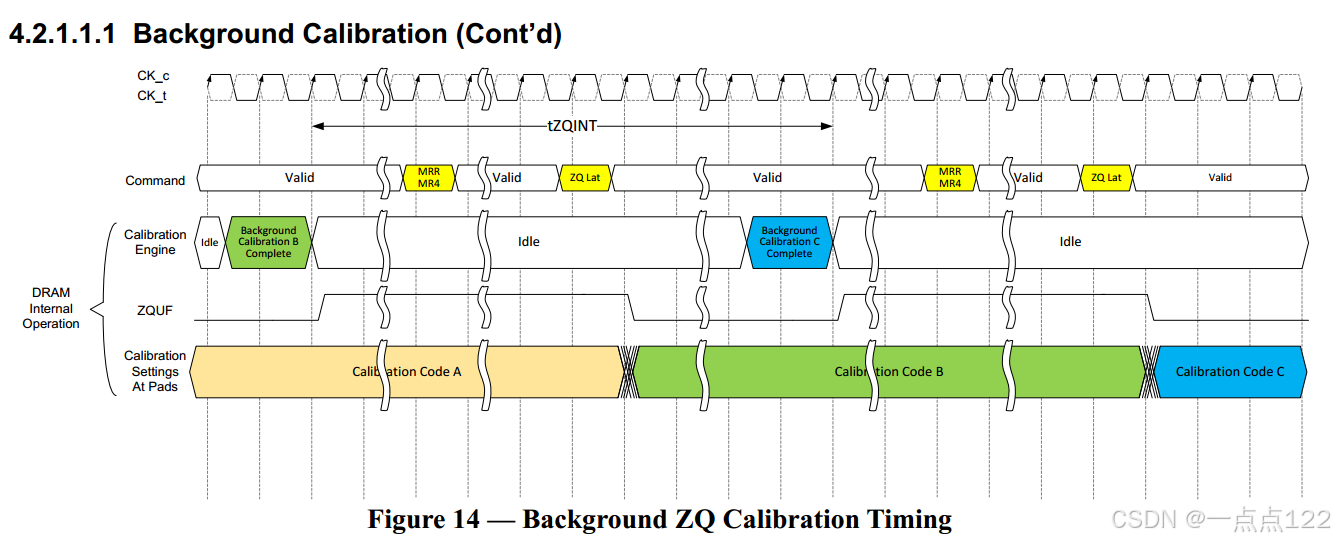

4.2.1.1.1 后台校准

在此模式下,下拉/ODT 和上拉/Voh 校准将在后台执行并由 DRAM 保持最新。 LPDDR5 SDRAM将在 MR28 OP[3:2] 中指定的时间间隔 tZQINT 内执行重新校准。不需要 ZQCal Start 命令,并且 DRAM 接收到的任何 ZQCal Start 命令都将被忽略。

下拉/ODT 校准由每个 DRAM 芯片使用连接在 VDDQ 和封装球或引脚(ZQ 资源)之间的外部 ZQ电阻器控制。这些 ZQ 资源可以在最多 NZQ 的多个 DRAM 芯片之间共享。校准将作为上电/初始化的一部分以及在 RESET_n 置位后自动执行。随后的重新校准将由 DRAM 保持最新。 DRAM 的自仲裁确保封装内最多 NZQ 裸片可以共享一个公共外部 ZQ 电阻器并避免冲突。共享外部 ZQ校准电阻时,抗噪性不会受到影响。

当自动下拉/ODT 校准完成后,上拉/Voh 校准将自动开始。在下拉/ODT 和上拉/Voh 校准完成时,如果新校准代码与当前锁存代码不匹配, MR4 OP[5] 位 (ZQUF) 将被设置。该位的 MRR 将通知系统新的校准结果可用,并且应发出 ZQCal Latch 命令(遵循 ZQCal Latch 时序约束)以确保始终保持 Pull-down、 ODT 和 Voh 的准确校准。 ZQUF 的设置对于每个裸片都是唯一的,与 ZQ引脚或多个引脚的配置或共享无关。或者,内存控制器可以选择不监视 ZQUF 并定期发出 ZQCal Latch 命令。

设置 MR28 OP[1]=ZQ Stop 将停止所有后台校准活动。将 MR28 OP[1] 重新设置为零将立即启动校准序列,其中共享 ZQ 资源的所有 DRAM 芯片将以串行方式重新校准。当退出无法进行重新校准的 DVFSQ 活动模式时,这可以实现快速重新校准。

4.2.1.1.2 在后台校准模式下锁存 ZQ 校准结果

锁存 ZQ 校准结果是通过 MPC ZQCal Latch 命令完成的。此命令将新的校准结果加载到下拉

/ODT 设备和上拉驱动器中。

当没有待处理或正在进行的 DQ 操作时,可以在断电之外的任何时间发出 ZQCal Latch 命令。最近完成的校准结果将始终与每个 ZQCal Latch 命令一起锁存。如果启用 CA ODT, CA 总线应在 tZQLAT 期间保持取消选择状态,以允许更新 CA ODT 校准设置。在任何情况下,在 tZQLAT期间始终不允许启动 DQ 操作的操作。

在执行 ZQCal Latch 命令并满足 tZQLAT 之前,不会更新 DQ 和 CA ODT 校准值,以下情况除外:

ZQ 校准将在上电/初始化时以及 Reset_n 引脚断言后针对每个 LPDDR5 芯片自动进行。应在 Tg 或之后向所有 LPDDR5 芯片发出 ZQCal Latch 命令。当执行 ZQCal Latch 命令时, ZQUF 位将在 tZQLAT 到期之前重置为 0。

4.2.1.1.3 Command-Based 校准

当选择Command-based校准后,ZQCal Start命令将会周期性地发送到ZQ触发器 die或者dice在每个DRAM package以保证精确的校准. ZQCal Start 命令只能在 DVFSQ 未激活时发出。存储器控制器可以读取 MR4 OP[6] 以确定封装中的哪个 DRAM 管芯被指定为 ZQ 启动器。 ZQ Initiator 的名称由DRAM 供应商硬编码。向未指定 ZQ 启动器的 DRAM 芯片发出的 ZQCal 启动命令将被忽略。

当 ZQ Initiator die 处于掉电或深度睡眠模式时, ZQCal Start 命令将被忽略,并且不会对共享 ZQ 资源的所有 die 进行重新校准。仅当 ZQ Initiator die 退出掉电或深度睡眠模式并接收到后续的 ZQCal Start 命令时,所有 die 才会被重新校准。

当 ZQ Initiator die 保持活动模式并接收到有效的 ZQCal Start 命令时,任何共享 ZQ 资源且处于断电或深度睡眠模式的 Target die 也将正常重新校准。共享 ZQ 资源的 DRAM 芯片可以以混合方式运行的系统(一些芯片运行,一些处于掉电或深度睡眠模式)在确定配置时如果需要在混合模式下重新校准,应注意 ZQ 启动器芯片指定。

4.2.1.1.4 在Command-based的校准模式下锁存 ZQ 校准结果

在基于命令的校准模式下,在满足 tZQCAL4、 tZQCAL8 或 tZQCAL16 后,应在 ZQCal Start 命令之后向每个芯片发出 ZQCal Latch 命令。 tZQCAL4 适用于 LPDDR5 DRAM 芯片,其中 ZQ 资源由四个或更少的 DRAM 芯片共享。 tZQCAL8 适用于 LPDDR5 DRAM 芯片,其中 ZQ 资源由四个和最多八个 DRAM 芯片共享。 tZQCAL16 适用于 LPDDR5 DRAM 裸片,其中 ZQ 资源由八个以上的DRAM 裸片共享,最多为十六个 (NZQ)。

ZQCal Latch 命令会将最新的校准结果加载到 LPDDR5 输出驱动器和 ODT 设备。如果未满足正确的 tZQCAL4、 tZQCAL8 或 tZQCAL16 延迟时间, LPDDR5 DRAM 可能会锁定先前的有效校准结果,但在任何情况下都不会锁定无效结果。与后台校准模式一样, 当没有待处理或正在进行的DQ 操作时, ZQCal Latch 命令可以在断电之外的任何时间发出。选择基于命令的校准模式时,ZQUF 的值未定义。

如果启用 CA ODT, CA 总线应在 tZQLAT 期间保持取消选择状态,以允许更新 CA ODT 校准设置。在任何情况下,启动 DQ 操作的操作在 tZQLAT 期间始终是不允许的。

在执行 ZQCal Latch 并满足 tZQLAT 之前,不会更新 DQ 和 CA ODT 校准值,以下情况除外:

- ZQ 校准将在上电/初始化时以及 Reset_n 引脚断言后针对每个 LPDDR5 芯片自动进行。应在 Tg 或之后向所有 LPDDR5 芯片发出 ZQCal Latch 命令。

4.2.1.1.5 保持准确校准 - 后台校准模式

要在 DVFSQ 未激活时保持下拉/ODT 校准和 Voh 校准:

- 基于 tZQINT,定期向 MR4 发出 MRR,以检查每个 LPDDR5 芯片的 ZQUF OP[5] 位状态。

- 如果 MR4 OP[5]=1,发出 ZQCal Latch 命令。

根据需要重复 1-2。或者,内存控制器可以选择不监视 ZQUF 并定期发出 ZQCal Latch 命令。在这种情况下,最近完成的校准结果将始终被锁存并且不会早于 tZQINT。

如果满足以下两个条件,则可能允许内存控制器忽略 ZQUF 并且不发出 ZQCal Latch 命令:

- CA ODT 已禁用

- LPDDR5 SDRAM 处于空闲状态,或处于自刷新或掉电模式

重新校准仍将在后台进行,以确保在需要时提供准确的驱动程序/ODT 设置。在这种情况下,如果设置了 ZQUF,内存控制器应确保在恢复数据流量之前执行 ZQCal Latch 命令。

当 DVFSQ 处于活动状态时,应为每个 LPDDR5 芯片设置 MR28 OP[1] ZQ 停止,以确保禁止重新校准。当 DVFSQ 不再处于活动状态时, ZQ Stop 可能会被取消断言,这将立即开始重新校准并启用后续的定期背景校准。当内存控制器取消声明 ZQ 停止时,它应在 100ns 内将共享 ZQ 资源的所有芯片的 MR28 OP[1] 重置为零,如中所述4.2.1.2.2. 在满足适当的 tZQCAL 时间(tZQCAL4、 tZQCAL8 或 tZQCAL16)后,将更新 ZQUF 并锁存重新校准的结果。

4.2.1.1.6 保持精确校准——Command-based校准模式

要在 DVFSQ 未激活时保持下拉/ODT 校准和 Voh 校准:

- 在系统条件允许的情况下,定期向 ZQ Initiator die 发出 ZQCal Start 命令

- 在适当的 tZQCAL 时间(tZQCAL4、 tZQCAL8 或 tZQCAL16)到期后,向每个芯片发出ZQCal Latch 命令。

根据需要重复 1-2。

当 DVFSQ 处于活动状态时,不会执行任何重新校准。

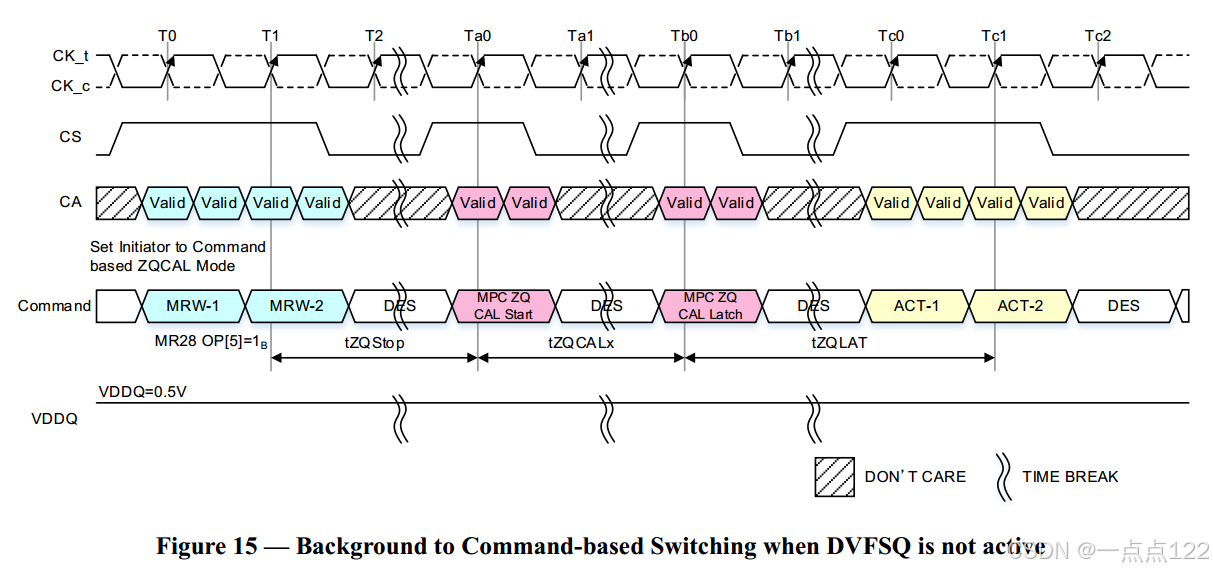

4.2.1.1.7 在校准模式之间切换

当设备不处于掉电或深度睡眠模式时,可以在上电和初始化时间 Tf 后的任何时间执行校准模式之间的更改。

4.2.1.1.7.1 DVFSQ 未激活时在校准模式之间切换

要在 DVFSQ 未激活时将共享 ZQ 资源的所有芯片从后台校准模式更改为基于命令的校准模式:

- 写入 ZQ Initiator die MR28 OP[5] = 1B。 MR28 OP[5] 也可以在 ZQ Target die 上更新,但这不是必需的,因为 LPDDR5 ZQ Target die 会忽略该位。

- 等待 tZQCALx

- 开始向 ZQ Initiator die 发出 ZQCal Start 命令,并向所有 die 发出后续 ZQ Latch 命令,以开始周期性的基于命令的校准,如中所述4.2.1.1.6.

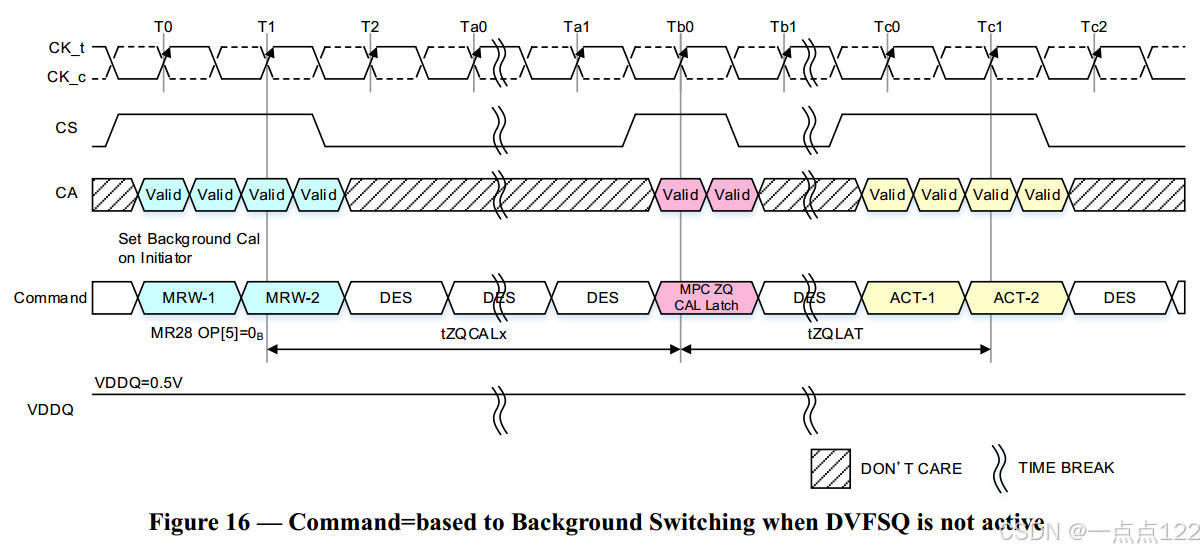

要在 DVFSQ 未激活时从基于命令的校准模式更改为所有裸片共享 ZQ 资源的后台校准模式:

- 确保之前的任何 ZQCal Start 命令都已满足 tZQCALx。

- 写入 ZQ Initiator die MR28 OP[5] = 0B。如果需要, MR28 OP[5] 也可以在 ZQ 目标裸片上设置为 0B。

- 按照中所述发出 ZQCal Latch 命令4.2.1.1.5.

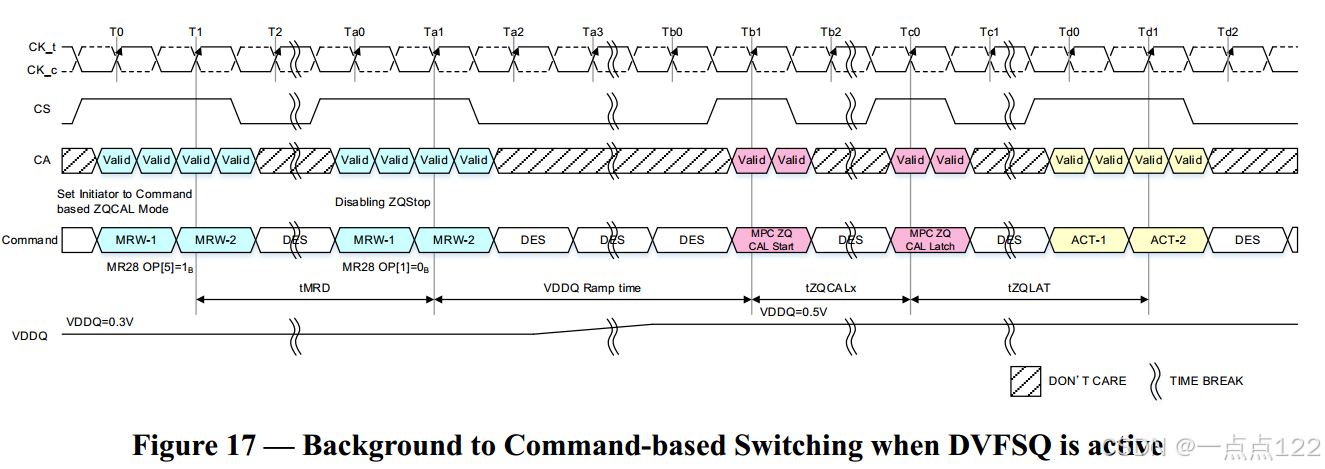

4.2.1.1.7.2 当 DVFSQ 处于活动状态时在校准模式之间切换

要在 DVFSQ 处于活动状态时将共享 ZQ 资源的所有芯片从后台校准模式更改为基于命令的校准

模式:

- 写入 ZQ Initiator die MR28 OP[5] = 1B。 MR28 也可以在 ZQ Target die 上更新,但这不是必需的,因为 LPDDR5 ZQ Target die 会忽略该位。

- MR28 OP[1] ZQ Stop 应写入 0B,用于共享 ZQ 资源的所有管芯。这可能与写入 MR28 OP[5]同时发生,或者在 ZQCal Start 命令可能被发送到 ZQ Initiator die 之前的至少tZQSTOP 的任何时间发生(当 DVFSQ 不再处于活动状态时)。

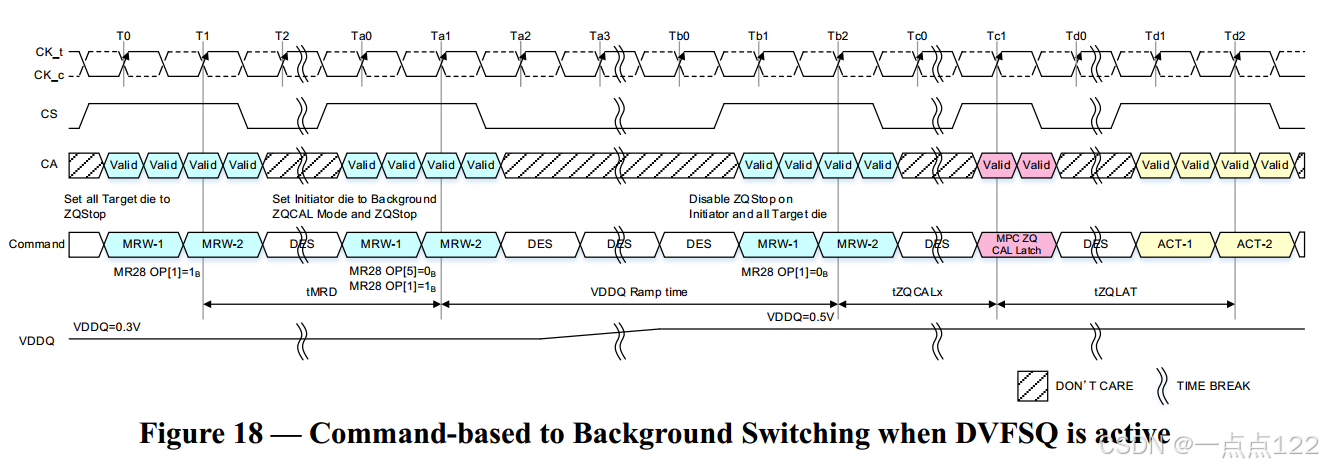

要在 DVFSQ 处于活动状态时将所有裸片共享 ZQ 资源的基于命令的校准模式更改为后台校准模

式:

- 写入所有 ZQ Target die MR28 OP[1] = 1B。

- 写入 ZQ Initiator die MR28 OP[5] = 0B 和 MR28 OP[1] = 1B。这些写操作应该同时发生——如果不是同时发生, MR28 OP[1] 应该首先被写入。

- 在 DVFSQ 不再活跃后, MR28 OP[1] 应写入 0B,用于共享 ZQ 资源的所有裸片。

4.2.1.2 ZQ 停止功能

4.2.1.2.1 其他设备共享 ZQ 电阻

4.2.1.2.1.1 后台校准模式下的 ZQ 电阻共享

在后台校准模式下,提供了 ZQ 停止功能,使另一台或多台设备共享 ZQ 电阻。此功能由 MR28 OP[1]=ZQ Stop 启用。当另一个设备需要使用 ZQ 电阻时,对于共享 ZQ 资源的所有 LPDDR5 设

备, MR28 OP[1] 应设置为 1。这将在延迟时间 tZQSTOP 内停止后台校准操作(参见表 24) 对于每个 LPDDR5 设备。一旦共享 ZQ 资源的所有 LPDDR5 设备的 tZQSTOP 都已过期,另一个设备可能会使用该资源。当其他设备不再需要 ZQ 资源时, ZQ 停止 MR 位应重置为 0 以允许后台校准正常继续。当 ZQ Stop MR 位重置为 0 时,将重新启动定期后台校准。

由于 ZQ Stop 禁止 LPDDR5 设备重新校准,请注意,在设置 ZQ Stop MR 位时更改系统条件可能会导致 LPDDR5 ZQ 校准精度偏离规范。为了确保持续准确的校准,如在4.2.1.1.5 和4.2.1.1.6, 当设置为后台校准模式时, ZQ 停止 MR 位的设置时间不应长于 tZQINT,或者当设置为基于命令的校准模式时, ZQ 停止 MR 位的设置时间不应长于 tZQINT 或正常的特定应用 ZQCal 启动命令间隔。

4.2.1.2.1.2 基于命令的校准模式下的 ZQ 电阻共享

在基于命令的校准模式下,除非设置了 ZQ 停止,否则在任何其他设备使用 ZQ 电阻器时,不得向 ZQ 启动器芯片发出 ZQCal 启动命令。除非设置了 ZQ 停止位,否则内存控制器应确保在允许任何设备使用 ZQ 电阻器之前满足来自最近的 ZQCal 启动命令的 tZQCAL4、 tZQCAL8 或tZQCAL16。当 MR28 OP[1] ZQ Stop 设置为 1B 时, LPDDR5 设备将忽略接收到的 ZQCal Start

命令。

4.2.1.2.2 当 DVFSQ 处于活动状态时停止背景校准

在后台校准模式下,应在进入 DVFSQ 之前通过设置 ZQ 停止来停止校准。当 DVFSQ 不再处于活动状态时(当 VDDQ 返回到 0.5v 标称电平时), ZQ Stop 可能会重置为 0。重置 ZQ Stop 将立即开始背景校准。在从 ZQ 启动器芯片上的 ZQ 停止重置开始的适当 tZQCAL 时间(tZQCAL4、tZQCAL8 或 tZQCAL16)到期后,内存控制器可以检查 ZQUF 标志,或者可以向共享 ZQ 资源的所有芯片发出 ZQCal Latch 命令。为保证在 tZQCAL 内重新校准所有共享 ZQ 资源的裸片, MR28 OP[1] ZQ 停止位应在 MR28 OP[1] ZQ 之前或之后不迟于 100ns 为共享 ZQ 资源的所有目标裸片重置ZQ Initiator die 上的停止位被重置。

4.2.1.2.3 VDDQ 断电时停止背景校准

在后台校准模式下,在进入掉电模式之前,应在 VDDQ 将要关闭时通过设置 ZQ Stop 停止校准。当退出掉电模式时, ZQ Stop 应重置为 0 以重新启用背景校准。重置 ZQ Initiator die 上的

ZQ Stop 将立即开始背景校准。在从 ZQ 停止重置开始的适当 tZQCAL 时间(tZQCAL4、 tZQCAL8或 tZQCAL16)到期后,内存控制器可以检查 ZQUF 标志,或者可以向共享 ZQ 资源的每个芯片发出 ZQCal Latch 命令。为保证在 tZQCAL 内重新校准所有共享 ZQ 资源的裸片, MR28 OP[1] ZQ 停止位应在 MR28 OP[1] ZQ 之前或之后不迟于 100ns 为共享 ZQ 资源的所有目标裸片重置

ZQ Initiator die 上的停止位被重置。

4.2.1.3 ZQ复位

设置 ZQ Reset MR 位可将输出阻抗校准重置为 ±30% 的默认精度(跨过程、电压和温度)。 ZQ复位命令通过写入 MR28-OP[0] = 1b 来执行。 ZQ 重置命令还将 ZQ 停止 MR28 OP[1] 和 ZQUF

MR4 OP[5] 位重置为 0。 ZQ 重置不会更改 ZQ 模式或 ZQ 间隔 MR 位 MR28 OP[5] 或 OP[ 3:2]。如果启用 CA ODT, CA 总线应在 tZQRESET 期间保持取消选择状态,以允许更新 CA ODT 校准设置。在任何情况下,在 tZQRESET 期间始终不允许启动 DQ 操作的操作。 ZQ 复位 MR 位应在tZQRESET 后由 DRAM 复位为 0b。要重置多管芯封装中的 ODT 和输出阻抗,无论 ZQ 启动器或ZQ 目标指定如何,都应向所有管芯发出 ZQ 复位功能。

Note1:WRITE 和 PRECHARGE 操作仅供说明之用。在锁存结果之前,可以在 tZQCAL 时间内执行任何单个或多个有效命令。

Note2:在执行 ZQCal Latch 命令之前, 任何先前使用 DQ 总线的命令都应该已经完成。在发出 ZQCal Latch 命令之前,应给予带有 DQ 终止的 WRITE 命令足够的时间来关闭 DQ ODT。请

参阅 7.6.4 ODT 部分了解 ODT 时序。

4.2.1.4 多管芯封装注意事项

单个封装内最多 NZQ LPDDR5 设备可以连接到同一个 ZQ 电阻器。 ZQCal Start 命令(当处于基于命令的校准模式时)是 Initiator die 所必需的,并且可以异步或同时向共享 ZQ 资源的其他

内存 die 发出。 ZQCal Start 命令到非启动器裸片被忽略。 ZQCal Latch 命令在需要时对每个芯片都是必需的。当多个裸片共享一个 ZQ 资源并且 ZQ 启动器裸片正在管理校准时(当 DVFSQ处于非活动状态时,无论是在后台模式下还是通过接受 ZQCal 启动命令), MR28 OP[1] ZQ 停止位应为所有 ZQ 设置为 0B Target die 共享 ZQ 资源。不需要其他仲裁注意事项。

4.2.1.4.1 背景校准模式中的其他注意事项

每个 LPDDR5 裸片都包含一个 ZQ 引脚和相关的 ZQ 校准电路。该电路的校准值将根据以下协议生成和使用:

- ZQ 停止位的设置始终优先于后台校准过程

- 如果在进行后台 ZQ 校准时 ZQ 停止 MR 位设置为 1,则后台校准将被中断

- 当 ZQ Stop MR 位重置为 0 时,后台校准将立即开始

- 当 ZQ Stop MR 位设置为 1 时,后台校准不会启动

- 将 ZQ 停止位设置为 1 不会重置 ZQUF 位

- ZQUF 位将仅通过 ZQCal Latch 命令或 ZQ Reset 复位

- 如果校准代码与当前锁存的代码不匹配,即使设备处于自刷新或掉电模式, ZQUF 位也会被设

置,前提是未设置 ZQ 停止

4.2.1.4.2 基于命令的校准模式中的其他注意事项

封装包括一个或多个 ZQ 引脚和相关的 ZQ 校准电路。将根据以下协议生成和使用来自该电路或电路的校准值:

不符合相应 tZQCAL4、 tZQCAL8 或 tZQCAL16 的 ZQCal 锁存命令可能会锁存最近完成的 ZQ校准的结果

4.2.1.5 ZQ 外部电阻器、公差和电容负载

要使用 ZQ 校准功能,应在 ZQ 引脚和 VDDQ 之间连接一个 240 欧姆、 ±1% 容差的外部电阻。

ZQ 引脚上的总容性负载应限制为 CZQ_N。

4.2.1.6 流程图示例

图 20–24 中的流程图仅代表一组共享单个 ZQ 资源的 LPDDR5 芯片。这些只是例子;可能还有其他有效的操作方法。

略.

4.2.2 命令总线training

LPDDR5 SDRAM 命令总线必须在为高频或中频操作启用终端之前进行训练。 LPDDR5 SDRAM 提供适用于未端接、低频操作的内部 VREF(CA) 默认电平,但是必须对 VREF(CA) 进行培训,以实现适合端接、高频或中频的接收器电压余量手术。此处描述的训练模式将内部 VREF(CA) 置于 CA数据眼中,同时允许对 CS 和 CA 信号进行时序调整以满足其 Rx Mask 要求。对于训练序列的简单性和难以在训练 CA 输入之前捕获 CA 输入,此处描述的训练模式使用最少的外部命令来进

入、训练和退出命令总线训练。

一旦 LPDDR5 SDRAM 通过 MRW 进入 CBT 模式,则仅允许用于退出 CBT 模式的 DES 和 MRW。

LPDDR5 SDRAM支持两种Command Bus Training模式,其特点如下: CBT模式由MR13 OP[6]选择(CBT模式1: MR13 OP[6] = 0B, CBT模式2: MR13 OP[6] =1B)

在共享 CA 总线的多级/通道系统中,应首先训练端接芯片,然后是非端接芯片。有关更多信息,请参见 7.6.4。对于multirank/channel系统中的WCK ODT设置,只有一个连接到公共WCK信号的SDRAM可以设置为CBT模式;非 CBT 训练的 SDRAM(s) 的 MR 需要设置 MR18 OP[2:0]=000B。

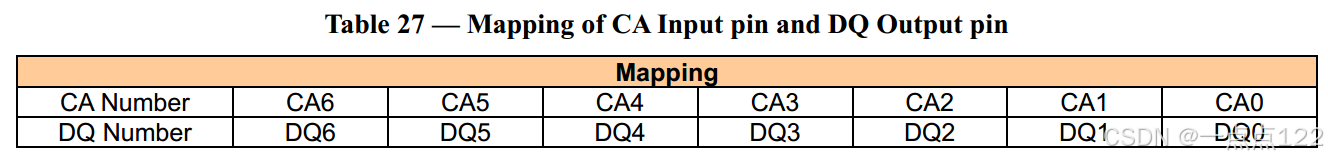

此定义中相应的 DQ 引脚可能因封装配置而异。例如,对于包含字节模式设备的封装,DQ[15:8] 和 DMI[1] 球可以连接到字节模式设备的 DQ[7:0] 和 DMI[0] 焊盘。

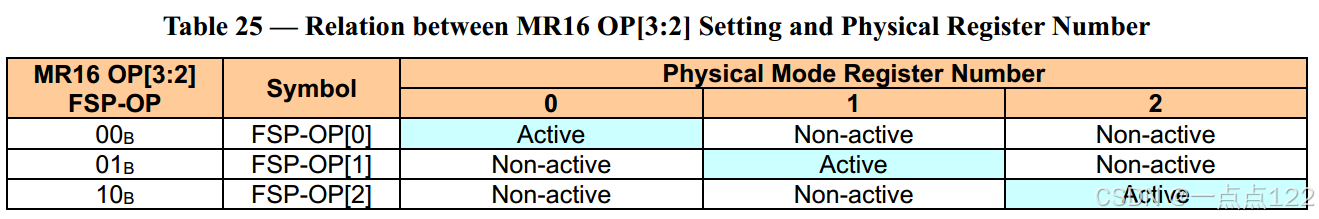

4.2.2.1 三个物理模式寄存器

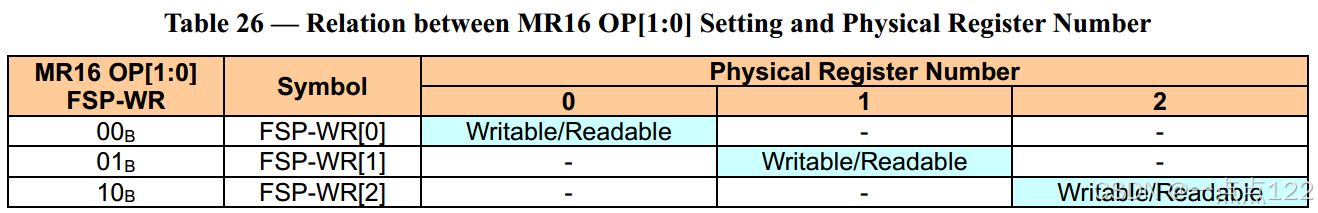

LPDDR5 SDRAM 具有三个物理模式寄存器,以减少改变工作频率时的 MR 设置时间。模式寄存器的活动或非活动状态由 MR16 OP[3:2]: FSP-OP (Frequency Set Point Operation Mode) 选择。可以在 MR16 OP[3:2] 中指定的设置是 FSP-OP[0]、 FSP-OP[1] 和 FSP-OP[2]。

启用对每个模式寄存器的写入/读取由 MR16 OP[1:0] FSP-WR(频率设置点写入/读取启用)选择。 MR 数据可以通过 FSP-WR 从/写入所选模式寄存器。

FSP-OP 和 FSP-WR 功能完全独立运行。

4.2.2.2 命令总线训练模式1

LPDDR5 SDRAM 使用频率设置点为芯片启用多个操作设置。 LPDDR5 SDRAM 在上电时启动到FSP-OP[0],其默认设置可在未端接的低频环境中运行。在训练之前,应通过为 FSP-WR(频率

设置点写入/读取启用)设置 MR16 OP[1:0],为 FSP-OP(频率设置点操作模式)设置所有其他模式寄存器位来配置模式寄存器设置) 进行高频或中频操作所需的设置,并设置 MR16 OP[5:4]以选择命令总线训练模式。

在进入命令总线训练之前, LPDDR5 SDRAM 将从 FSP-OP[x] 运行。在 DQ[7] 被驱动为高电平时进入命令总线训练时, LPDDR5 SDRAM 将根据 MR16 OP 自动切换到活动 FSP 寄存器集 FSPOP[x]、 FSP-OP[y] 或 FSP-OP[z] [5:4] 并在训练期间使用活动寄存器设置。当 DQ[7] 被驱动为低电平时命令总线训练退出时, LPDDR5 SDRAM 将自动切换回原始 FSP 寄存器组 FSPOP[x],返回到训练前运行的“已知良好”状态。

LPDDR5 SDRAM可以通过MR16 OP[7]设置来选择Command Bus Training CA阶段。如果 MR16 OP[7] = 0B, DQ 输出由 CK_t 上升沿锁存的 CA 模式。如果 MR16 OP[7] =1B, DQ 输出由CK_t 下降沿锁存的 CA 模式。

CBT 模式期间需要差分 WCK 输入。因此, MR20 OP[3:2] 需要将 00B 设置为在进入 CBT 模式之前使用 CBT 训练的两个 FSP 集。此外, VRCG 应在使用 DVFSQ 的 CBT 模式期间打开。

- 为命令总线训练模式 1 设置 MR13 OP[6]=0B。

- 要进入命令总线训练模式,发出 MRW-1 命令,然后发出 MRW-2 命令以设置 MR16 OP[5:4]以选择 CBT 模式。无论 MR18 设置如何, WCK ODT 值固定为 40ohm,并且 DQ ODT 和 NTODT 状态在 CBT 模式期间关闭。 WCK 输入需要为有效电平(WCK_t = Low 和 WCK_c =High)并且 DQ7 需要在 MRW-2 命令输入之前为低电平。在 tCBTWCKPRE_static 之后,WCK 信号可以被切换。在 DQ7 变高之前需要满足 tWCK2DQ7H。

- DQ[7] 被驱动为高电平,当 LPDDR5 SDRAM 通过 WCK 采样 DQ[7] 的高电平时, LPDDR5 SDRAM 从 FSP-OP[x] 切换到由 MR16 OP[5:4] 定义的 FSP 集,完成进入命令总线训练模式。在这种情况下, WCK 不需要同步时钟 (CK) 信号。在 tDQ7HWCK 之后, WCK 可以是有效电平(WCK_t = Low 和 WCK_c = High)或改变 WCK 频率。

- 在 tCAENT 之后, LPDDR5 SDRAM 可以接受通过 CA 总线输入 CA 训练模式。

- 为验证接收器是否具有正确的 VREF(CA) 设置并进一步训练 CA 眼相对于时钟 (CK),锁存在 CA 总线上接收器的值异步输出到 DQ 总线。

- 要退出命令总线训练模式,将 DQ[7] 驱动为低电平并在 tDQ7LWCK + tVREFCA_LONG 时间后发出 MRW 命令以设置 MR16 OP[5:4] = 00B。在时间 tMRD 之后, LPDDR5 SDRAM 准备好进行正常操作。训练退出后, LPDDR5 SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器。

命令总线训练可以从空闲或自刷新状态进入。进入 CBT 时, SDRAM 不得处于掉电状态或深度睡眠模式。无论启动 CBT 的 SDRAM 状态如何,命令总线训练的进入和退出都是相同的。

single-rank systems的训练序列

请注意,此处显示的示例假设初始低频、未终止操作点,训练高频或中频、终止操作点。蓝色文字是低频,红色文字是高频。可以从任何已知的良好操作点训练任何操作点。此示例假设以下条

件。低频操作的频率设置点“X”和高频操作的频率设置点“Y”。

1) 设置 MR16 OP[1:0] 以启用写入频率设置点“Y”(FSP-WR[y])。

2) 为所有通道写入 FSP-WR[y] 寄存器以设置高频操作参数。

3) 设置 MR16 OP[5:4] 以选择 CBT 模式 (CBT[y])。

4) 发出 MRW-1 和 MRW-2 命令进入命令总线训练模式。

5) 将 DQ[7] 驱动为高电平,然后将 CK 频率更改为高频工作点。

6) 执行命令总线培训(CS 和 CA)。

7) 通过将 DQ[7] 驱动为低电平来退出训练,在将 DQ[7] 驱动为低电平之前将 CK 频率更改为低频工作点,然后发出 MRW-1 和 MRW-2 命令以退出命令总线训练模式。当 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器。

8) 通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将训练值写入 FSP-WR[y]。

9) 发出MRW-1和MRW-2命令切换到FSP-OP[y]开启终端,改变CK频率到高频工作点。此时Command Bus已经训练完成,可以执行其他训练或正常操作。

multiple-rank systems的训练序列

请注意,此处显示的示例假设初始低频、未终止操作点,训练高频或中频、终止操作点。蓝色文字是低频,红色文字是高频。可以从任何已知的良好操作点训练任何操作点。此示例假设以下条

件。低频操作的频率设置点“X”和高频操作的频率设置点“Y”。 FSP-WR[x] 和 FSP-OP[x] 是终止秩和非终止秩的初始状态。在开始命令总线训练之前,需要使用 FSP-OP[x] 和 FSP-OP[y] 禁用

终止等级和非终止等级的 WCK ODT 和 NT-ODT: WCK ODT: MR18 OP[2 :0]=000B, NT-ODT: MR11 OP[3]=0B 或 MR41 OP[7:5]=000B。

WCK ODT 和 NT-ODT 设置将被禁用,以确保 WCK 和 DQ[7] 输入有足够的幅度。这些信号引脚在CBT 模式期间应用于多种功能,例如控制进入/退出 CBT 模式和捕获 DQ[7] 输入电平。

1) 设置 MR16 OP[1:0] 以启用写入两个级别的频率设置点“Y”(FSP-WR[y])。

2) 为所有通道写入 FSP-WR[y] 寄存器以设置两个等级的高频操作参数。

3) 发出 MRW-1 和 MRW-2 命令以在终端列上进入命令总线训练模式 (CBT[y]):设置MR16 OP[5:4] 以选择 CBT 模式 (CBT[y])。

4) 在终止等级(或所有等级)上将 DQ[7] 驱动为高电平,然后将 CK 频率更改为高频工作点。

5) 在终止等级(CS 和 CA)上执行命令总线训练。

6) A 将 CK 频率更改为低频工作点,然后在终止等级(或所有等级)上将 DQ[7] 驱动为低电平。当 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器(即,训练值不被保留内存)

7) 发出 MRW-1 和 MRW-2 命令以退出终端列上的命令总线训练模式(正常操作):设置 MR16 OP[5:4] 以选择正常操作。

8) 通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将训练值写入终止等级的 FSP-WR[y]。

9) 发出 MRW-1 和 MRW-2 命令以在非终止列上进入命令总线训练模式 (CBT[y]):设置 MR16 OP[5:4] 以选择 CBT 模式 (CBT[y])。但是,保持 DQ[7] 为低电平。

10)发出 MRW-1 和 MRW-2 命令将终止等级切换到 FSP-OP[y] 以打开终止。然后改变CK频率到高频工作点。

11)在非终止(或所有)等级上将 DQ[7] 驱动为高电平。非终止等级现在将使用 FSP-OP[y]。

12)在非终止等级(CS 和 CA)上执行命令总线训练。

13)发出 MRW-1 和 MRW-2 命令将终止等级切换到 FSP-OP[x] 以关闭终止。

14)通过在非终止等级上将 DQ[7] 驱动为低电平来退出训练,将 CK 频率更改为低频工作点,并发出 MRW-1 和 MRW-2 命令以退出命令总线训练模式。当 DQ[7] 被驱动为低电平并且SDRAM 通过 WCK 采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器。

15)通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将非终止等级的训练值写入 FSP-WR[y]。

16)发出MRW-1和MRW-2命令将terminating rank切换到FSP-OP[y]开启termination,改变CKfrequency到高频工作点。此时命令总线已针对两个等级进行训练,并且可以执行其他训练或正常操作。

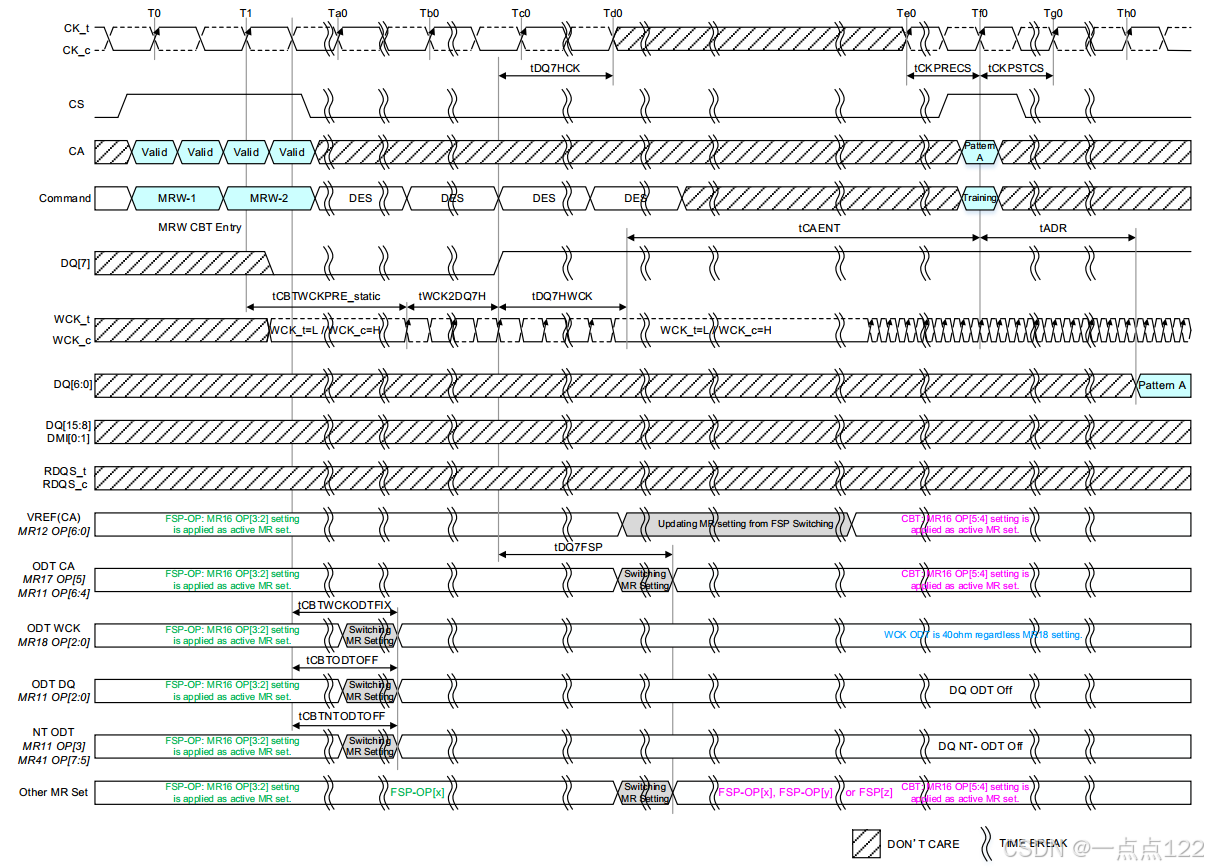

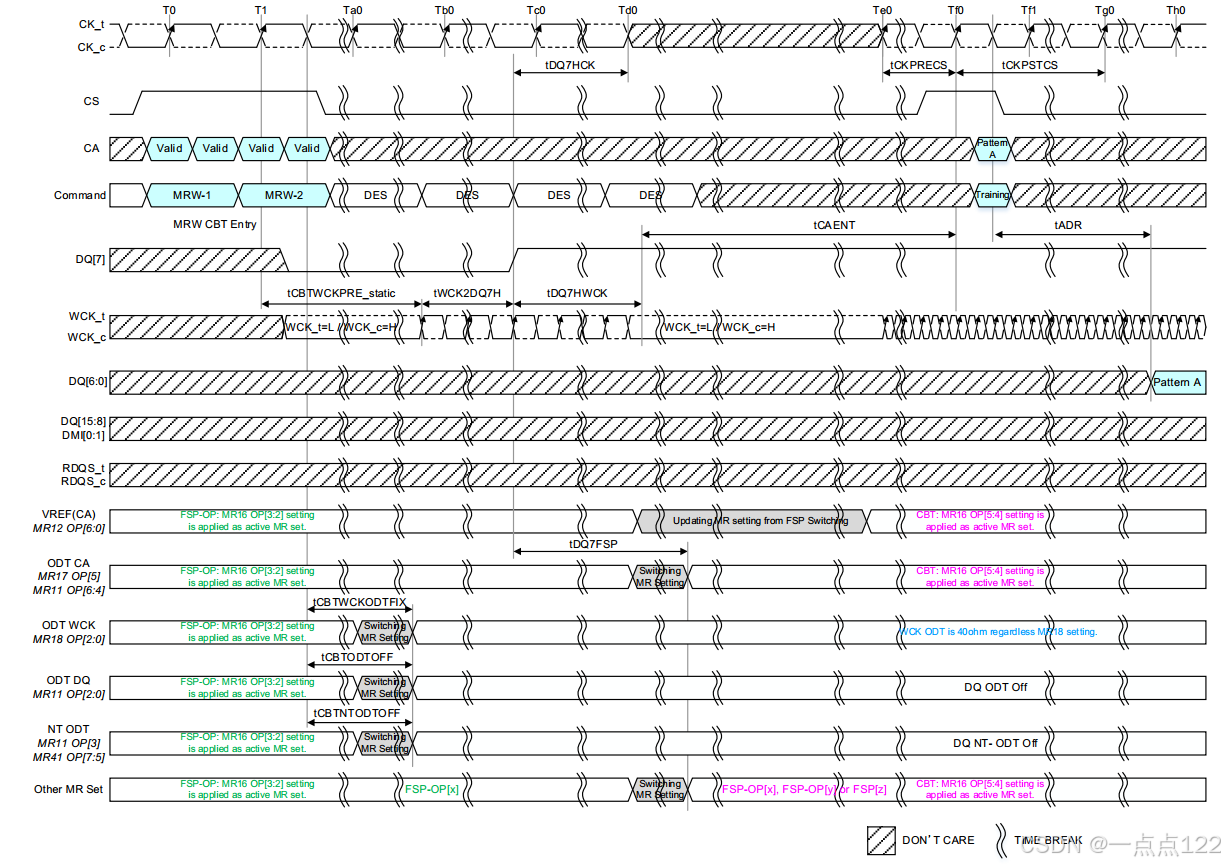

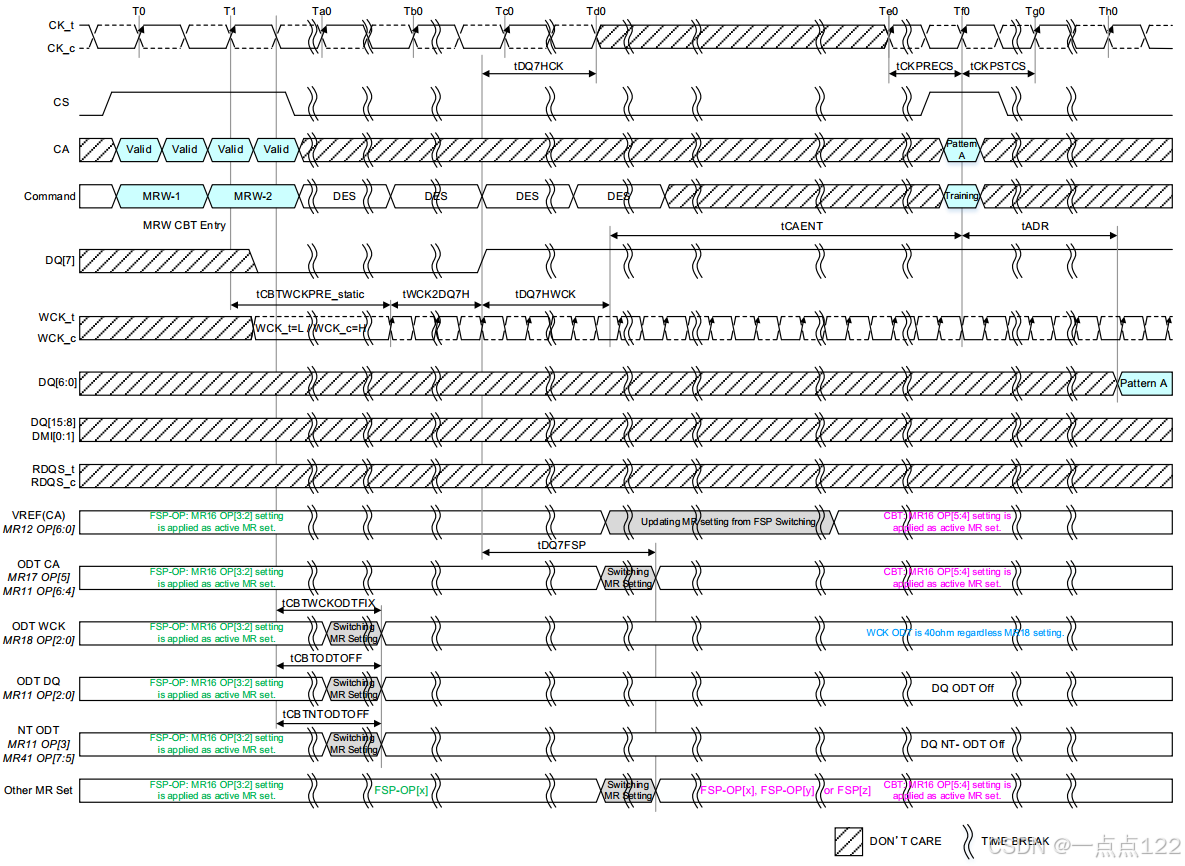

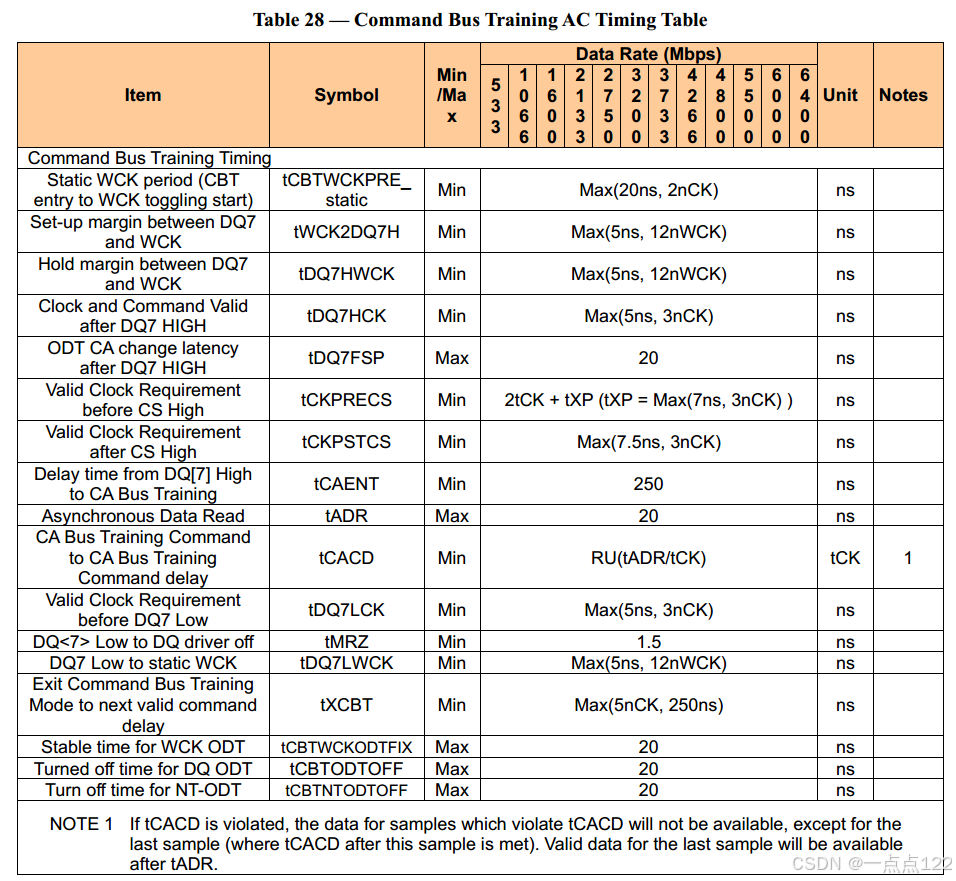

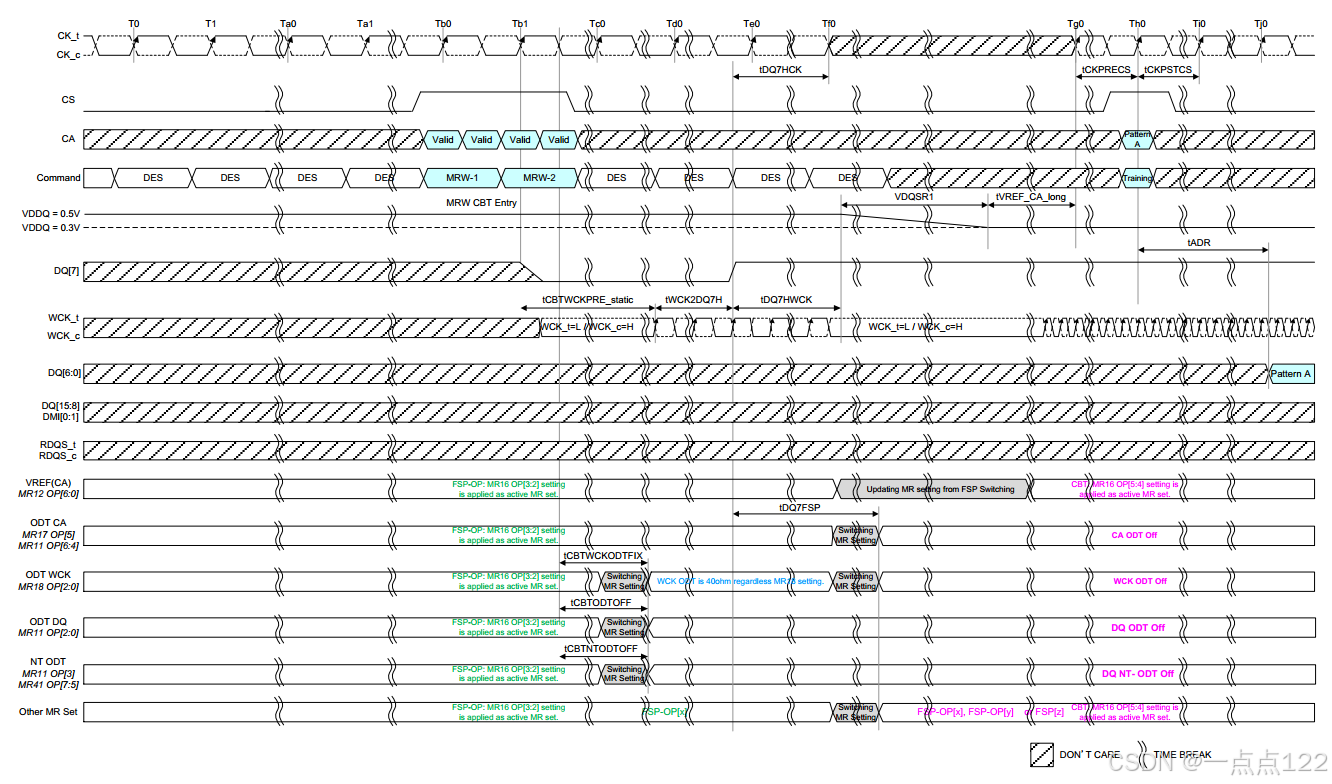

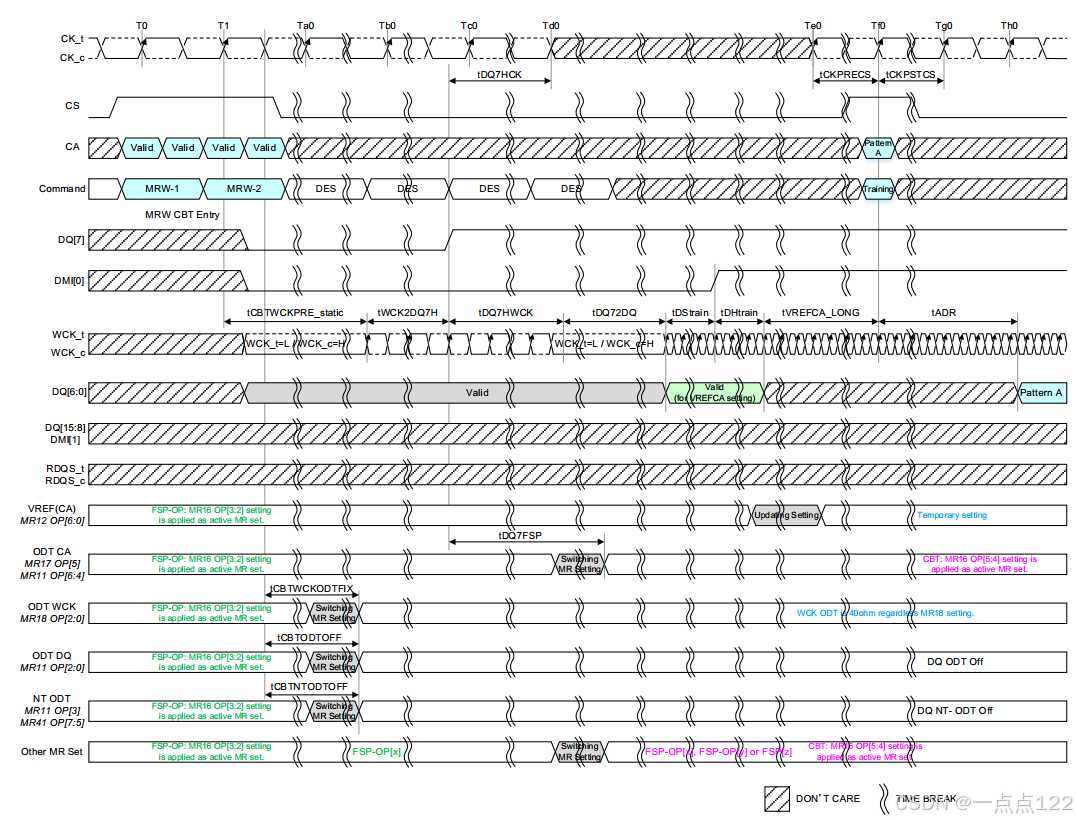

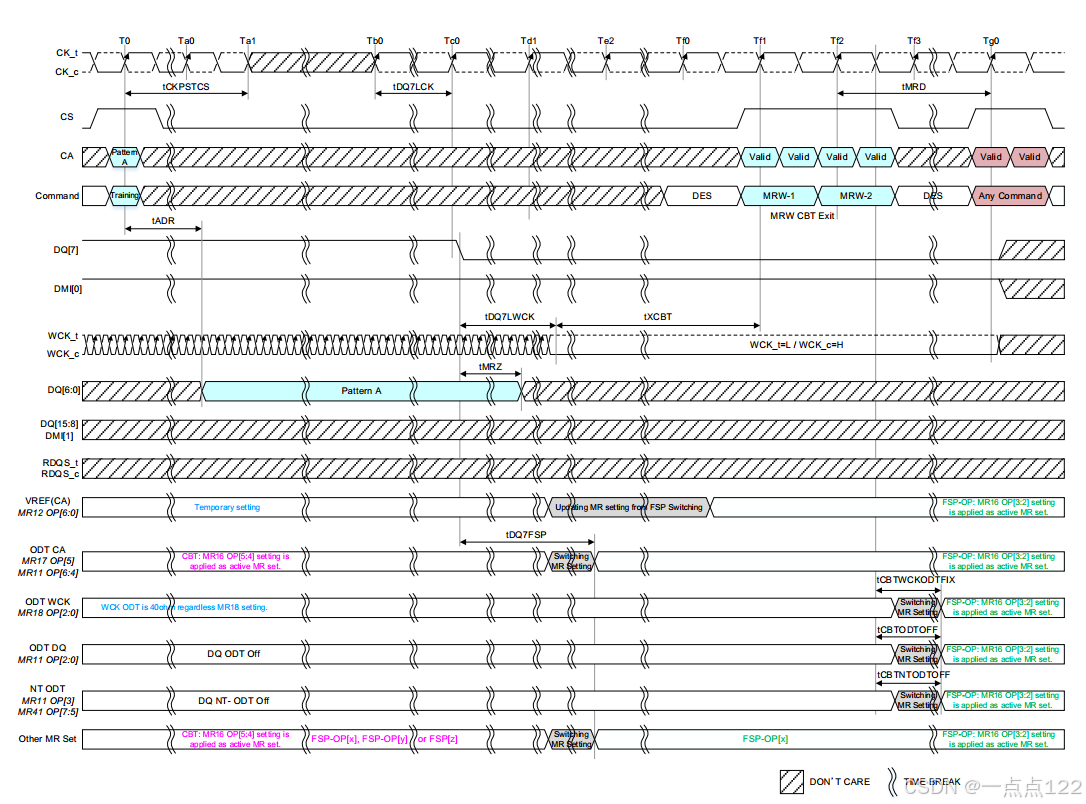

命令总线训练模式 1 的基本时序图如下图 25-28 所示。

图 25 — 进入命令总线训练模式和 CA 训练模式输入和输出(WCK 频率变化)

Note1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

Note2 输入时钟条件应满足tCKPRECS。

Note3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

Note4 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。如果交替FSP-OP 禁用了 ODT CA,那么终止将不会在 CA 总线训练模式下启用。

Note5 WCK ODT 状态设置为固定值, DQ ODT/NT-ODT 在 CBT 操作期间关闭。

注 6 在命令总线训练进入之前和

之后可以使用相同的 FSP 和时钟频率。

注 7 CBT 阶段: MR16 OP[7] = 0B

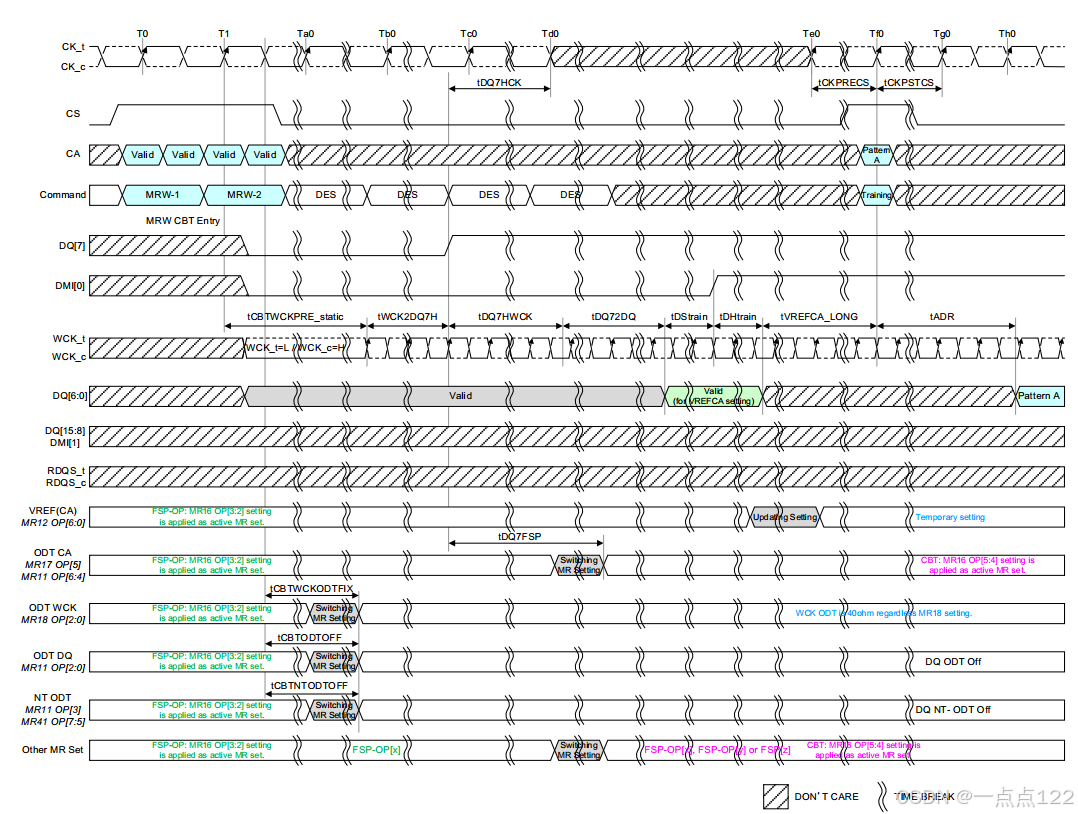

图 25 — 进入命令总线训练模式和 CA 训练模式输入和输出(WCK 频率变化)

图 26 — 进入命令总线训练模式和 CA 训练模式输入和输出(WCK 频率变化:下降沿训练)

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。如果交替FSP-OP 禁用了 ODT CA,那么终止将不会在 CA 总线训练模式下启用。

注 5 WCK ODT 状态设置为固定值, DQ ODT/NT-ODT 在 CBT 操作期间关闭。

注 6 WCK 频率在 CBT 操作期间无关紧要,只要频率在每个频率模式 (MR18 OP[3]) 的允许范围内即可。 WCK 切换可能会在 tDQ7HWCK 之后停止,但 WCK 对应在静态电平驱动(WCK_t/c =低/高)。在 DQ[7] 再次改变之前, WCK 应该切换以满足 tWCK2DQ7H。

注 7 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。

注 8 CBT 阶段: MR16 OP[7] = 1B

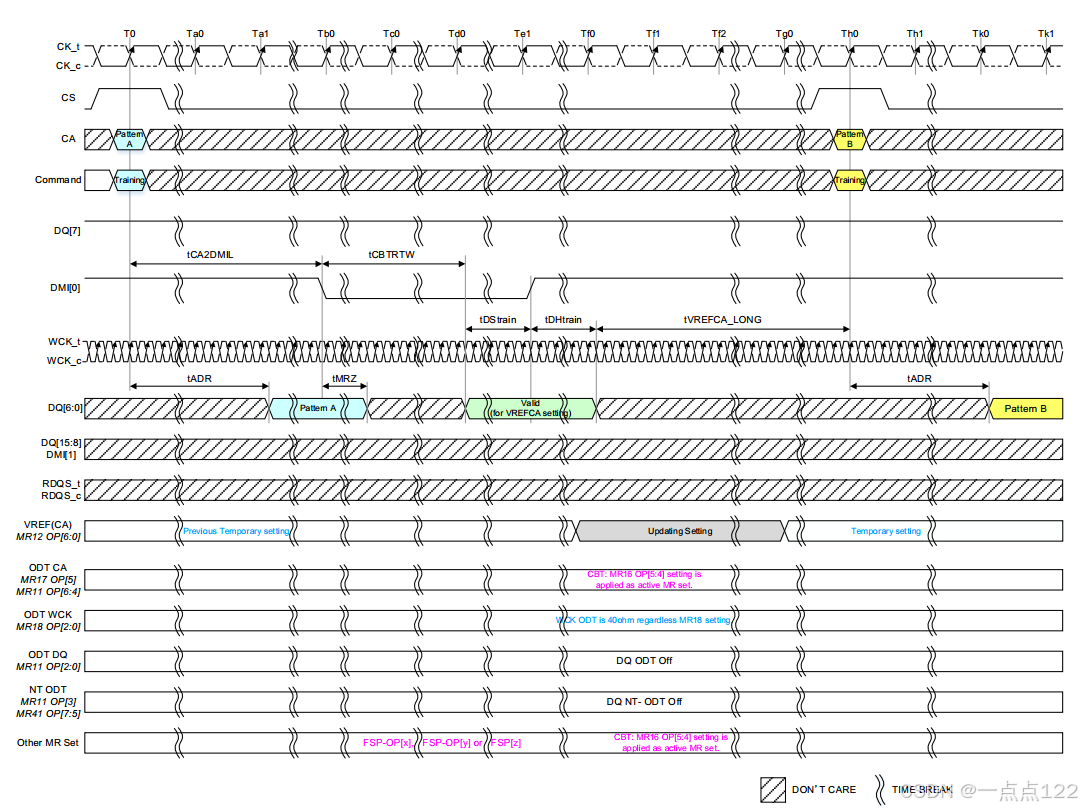

图 27 — 进入命令总线训练模式和 CA 训练模式输入和输出(固定 WCK 频率)

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。如果交替FSP-OP 禁用了 ODT CA,那么终止将不会在 CA 总线训练模式下启用。

注 5 WCK ODT 状态设置为固定值, DQ ODT/NT-ODT 在 CBT 操作期间关闭。

注 6 无论 CK:WCK 比率如何,在CBT 操作期间设置固定 WCK 频率。只要频率在每个频率模式 (MR18 OP[3]) 的允许范围内, WCK 频率在 CBT 操作期间无关紧要。 WCK 切换可能会在 tDQ7HWCK 之后停止,但 WCK 对应在静态电平驱动(WCK_t/c = 低/高)。在 DQ[7] 再次改变之前, WCK 应该切换以满足 tWCK2DQ7H。

注 7 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。

注 8 CBT 阶段: MR16 OP[7] = 0B

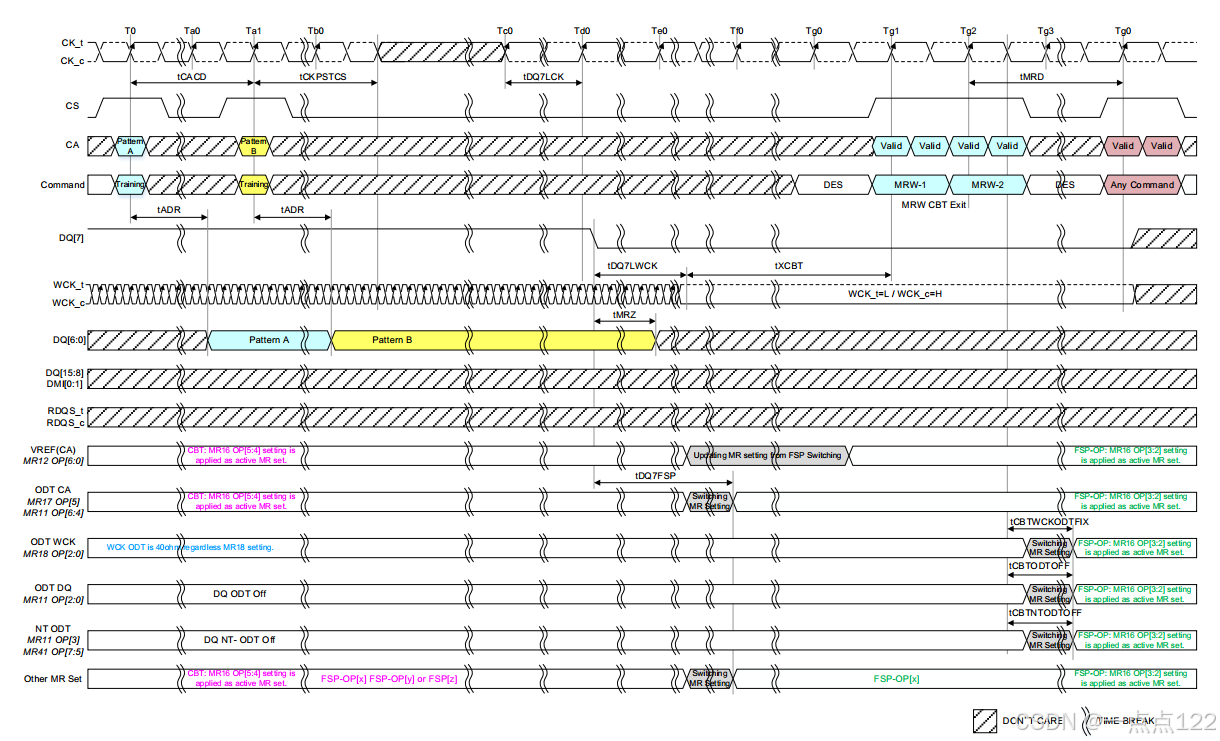

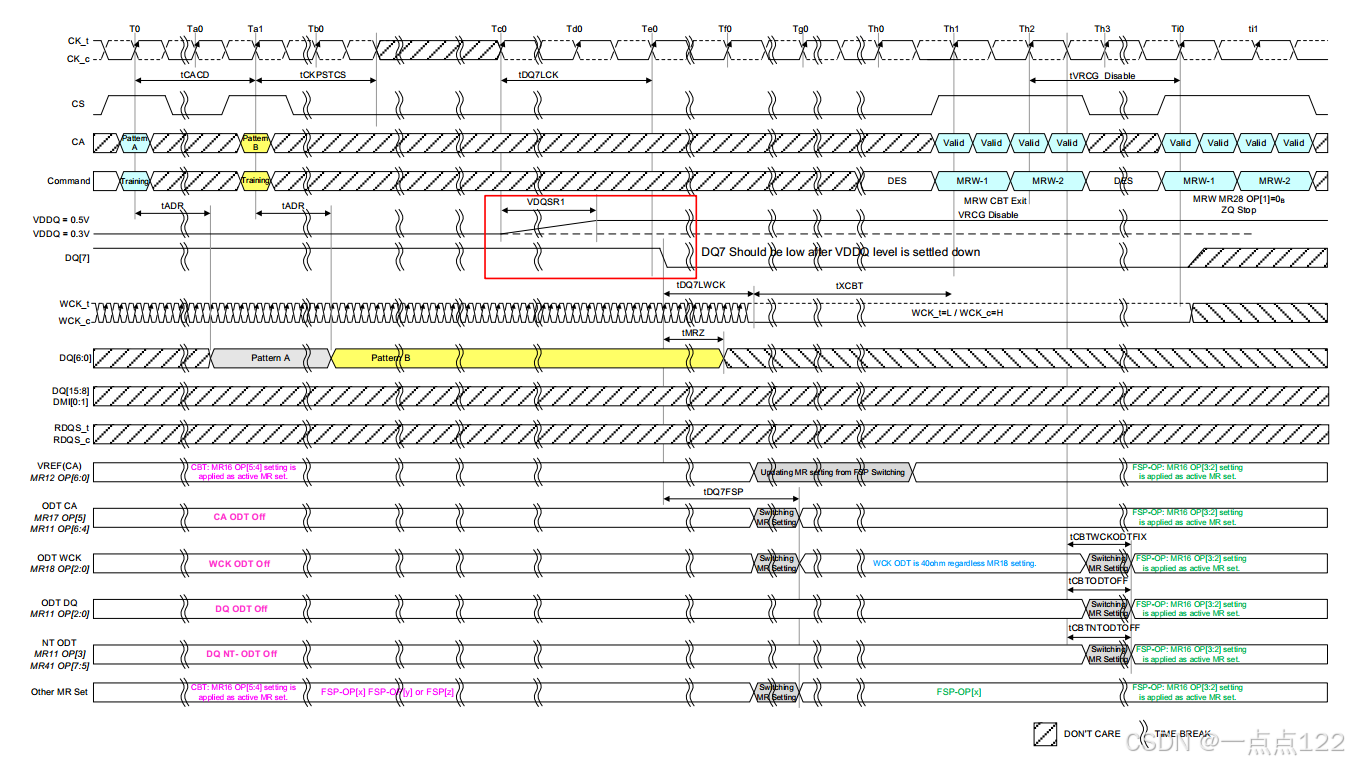

图 28 — 连续 CA 输入和退出命令总线训练模式

注 1 CK 需要在 DQ[7] 被驱动为低电平之前满足 tDQ7LCK。不关心 休息时间

注 2 要求DQ[7]和WCK信号为有效电平,直到满足MRW命令退出该模式引起的tMRD。

注 3 在 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 切换采样 DQ[7] 的低电平之后, SDRAM ODT_CA 将恢复到命令总线训练模式进入之前由 FSP-OP 定义的状态/值,即。 , 原始频率设定点 (FSP-OP)。示例: 如果 SDRAM 使用 FSP-OP[x]、 FSP-OP[y] 或 FSP-OP[z] 进行训练,那么它将在 DQ[7] 被驱动为低电平后切换到 FSP-OP[x],并且通过 WCK 切换采样低电平。

注 4 WCK 在 CBT 模式下不需要与时钟信号同步。

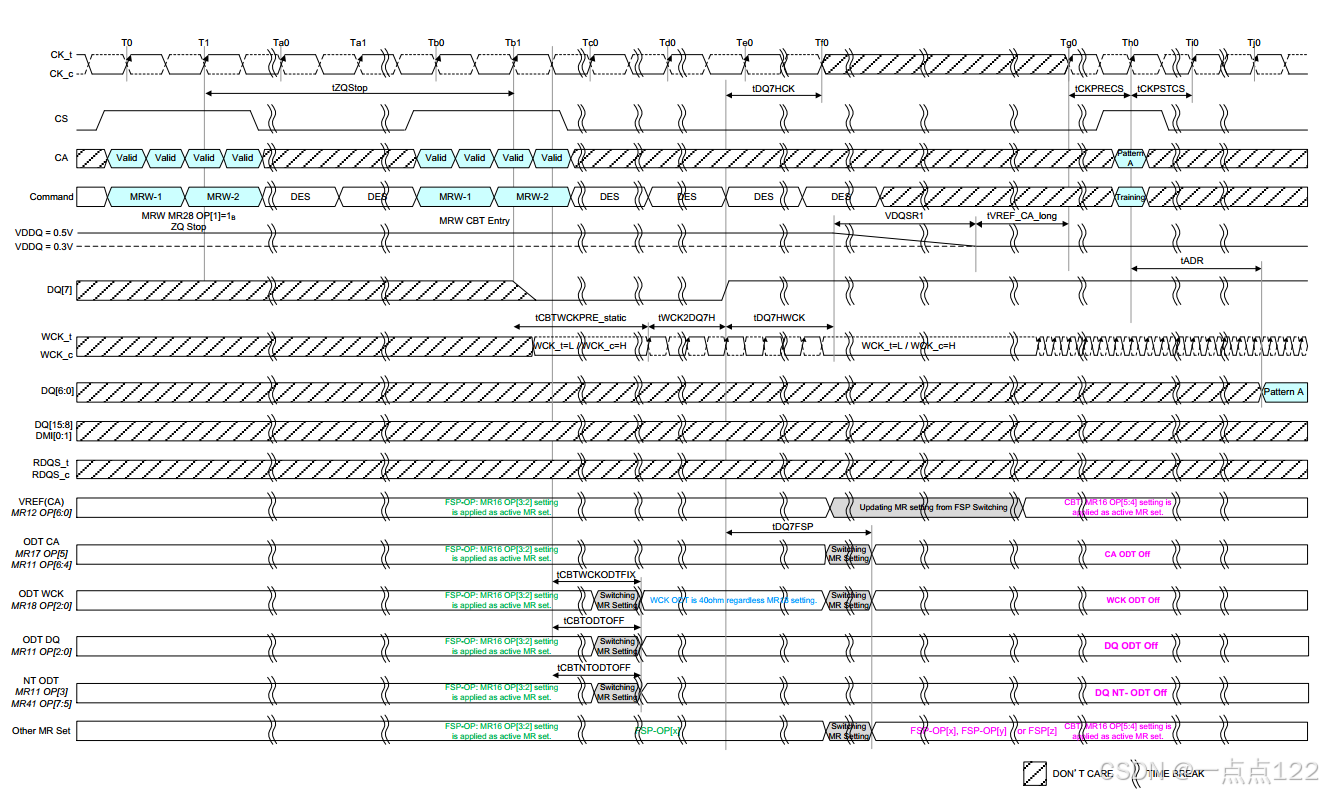

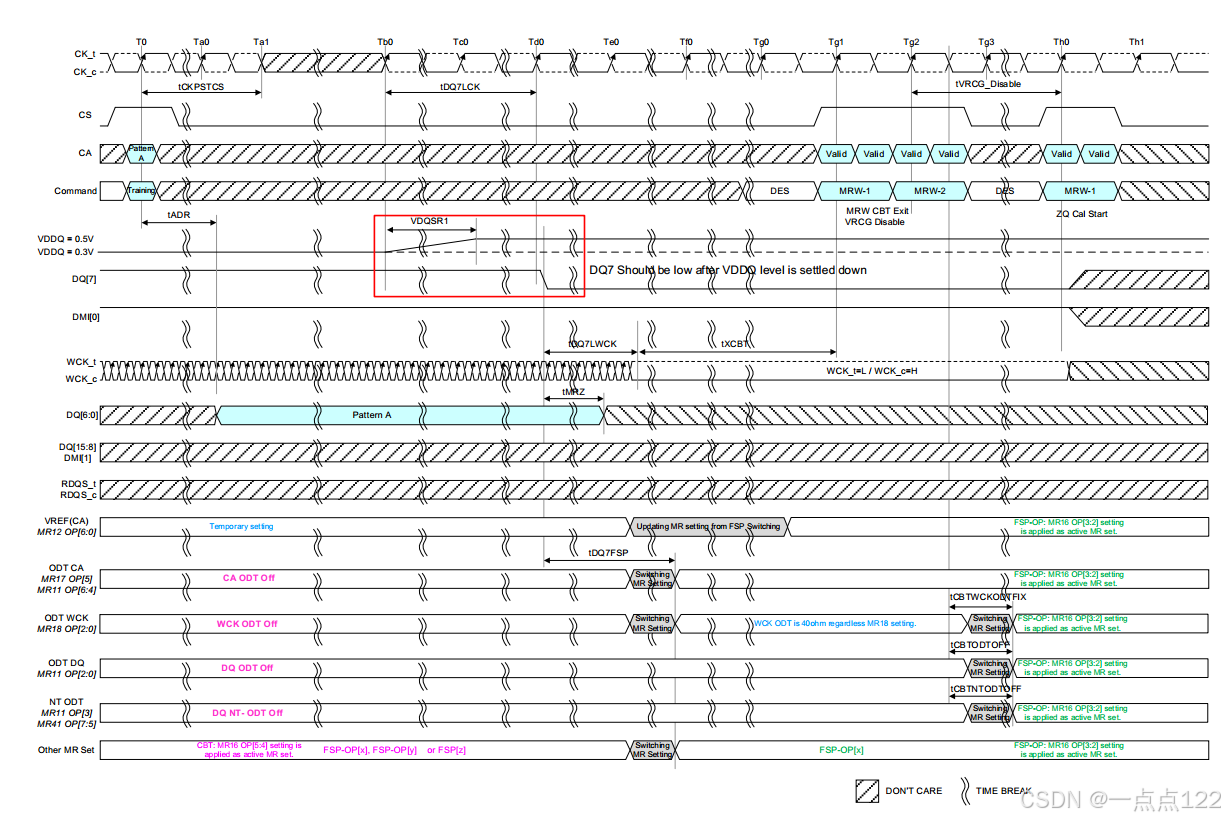

4.2.2.3 命令总线训练模式 1(启用 DVFSQ 的 FSP)

启用 DVFSQ 的 FSP 的 CBT (MR19 OP3[3:2]=01B),请按照以下步骤操作。本节适用于支持 DVFSQ 功能的 SDRAM。红色文本是 DVFSQ 禁用模式,蓝色文本是 DVFSQ 启用模式。

1) 设置 MR16 OP[1:0] 以启用写入频率设置点“Y”(FSP-WR[y])。

2) 为所有通道写入 FSP-WR[y] 寄存器以设置启用 DVFSQ 的操作参数。

3) 禁用 SoC ODT 并设置 MRW MR17 OP[2:0]=000 B.

4) 在背景 ZQ 校准模式的情况下,发出 MRW MR28 以设置 ZQ_STOP(MR28 OP[1]=1B)并等待 tZQSTOP。

5) 设置为 VRCG VREF 高电流模式: MR16 OP[6]=1B 并等待 tVRCG 启用

6) 通过 MRW-1 和 MRW-2 命令设置 MR16 OP[5:4] 以选择 CBT 模式 (CBT[y]):进入 CBT模式。

7) 将 DQ[7] 驱动为高电平,然后将 VDDQ 斜坡下降至标称值 0.3V。 (请勿在此处训练!)对于 VDDQ 转换率 VDQSR1,请参阅“DVFSQ 模式”规范。

8) VREFCA更新时序, VDDQ斜降完成后需要tVREF_CA_long。

9) 执行命令总线培训(CS 和 CA)。

10) 在 CBT 退出之前,将 VDDQ 斜升至 0.5V 标称值。对于 VDDQ 转换率 VDQSR1,请参阅“DVFSQ 模式”规范。在将 DQ[7] 驱动为低电平之前,将 CK 频率更改为 FSP[x] 频率工作点

11) 通过将 DQ[7] 驱动为低电平来退出训练。当 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器(即,训练值不被保留内存)。

12) 等待 tXCBT

13) 发出 MRW-1 和 MRW-2 命令以退出命令总线训练模式并根据需要设置 VRCG VREF 高电流模式禁用。发布 ZQ_Stop(设置 MR28 OP[1]=0B)以启动背景 ZQ 校准。

14) 等待 tZQCALx 并发出 ZQCal Latch 命令。

15) 通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将训练值写入 FSP-WR[y]。

16) 发出MRW-1和MRW-2命令切换到FSP-OP[y]开启终端,改变CK频率和VDDQ电平到FSP-OP[y]工作点。此时Command Bus已经训练完成,可以执行其他训练或正常操作。

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。

注 5 CA ODT、 WCK ODT 和 DQ ODT/NT-ODT 在 CBT 和 DVFSQ 操作期间关闭。

注 6 在命令总线训练进入之前

和之后可以使用相同的 FSP 和时钟频率。

注 7 CBT 阶段: MR16 OP[7] = 0B

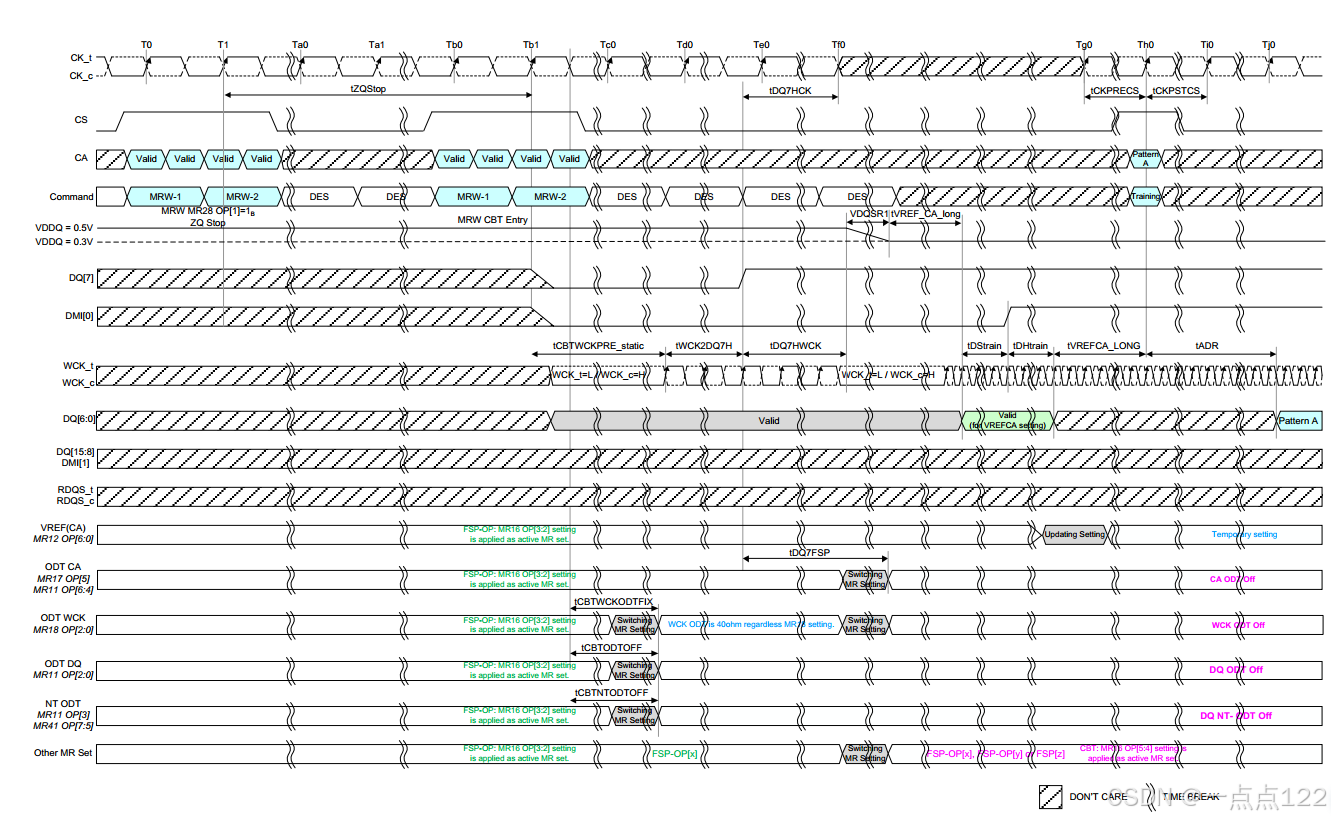

图 29 — 进入命令总线训练模式和 CA 训练模式输入和输出(后台 ZQ 校准)

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。

注 5 CA ODT、 WCK ODT 和 DQ ODT/NT-ODT 在 CBT 和 DVFSQ 操作期间关闭。

注 6 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。

注 7 CBT 阶段: MR16 OP[7] = 0B

图 30 — 进入命令总线训练模式和 CA 训练模式输入和输出(基于命令的 ZQ 校准)

注 1 CK 需要在 DQ[7] 被驱动为低电平之前满足 tDQ7LCK。

注 2 要求DQ[7]和WCK信号为有效电平,直到满足MRW命令退出该模式引起的tMRD。

注 3 在 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 切换采样 DQ[7] 的低电平之后, SDRAM ODT_CA 将恢复到命令总线训练模式进入之前由 FSP-OP 定义的状态/值,即。 , 原始频率设定点 (FSP-OP)。示例: 如果 SDRAM 使用 FSP-OP[x]、 FSP-OP[y] 或 FSP-OP[z] 进行训练,那么它将在 DQ[7] 被驱动为低电平后切换到 FSP-OP[x],并且通过 WCK 切换采样低电平。

注 4 WCK 在 CBT 模式下不需要与时钟信号同步。

图 31 — 连续 CA 输入和退出命令总线训练模式(后台 ZQ 校准)

注 1 CK 需要在 DQ[7] 被驱动为低电平之前满足 tDQ7LCK。

注 2 要求DQ[7]和WCK信号为有效电平,直到满足MRW命令退出该模式引起的tMRD。

注 3 在 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 切换采样 DQ[7] 的低电平之后, SDRAM ODT_CA 将恢复到命令总线训练模式进入之前由 FSP-OP 定义的状态/值,即。 , 原始频率设定点 (FSP-OP)。示例: 如果 SDRAM 使用 FSP-OP[x]、 FSP-OP[y] 或 FSP-OP[z] 进行训练,那么它将在 DQ[7] 被驱动为低电平后切换到 FSP-OP[x],并且通过 WCK 切换采样低电平。

注 4 WCK 在 CBT 模式下不需要与时钟信号同步。

图 32 — 连续 CA 输入和退出命令总线训练模式(基于命令的 ZQ 校准)

4.2.2.4 命令总线训练模式2

LPDDR5 SDRAM 使用频率设置点为芯片启用多个操作设置。 LPDDR5 SDRAM 在上电时启动到FSP-OP[0],其默认设置可在未端接的低频环境中运行。在训练之前,应通过为 FSP-WR(频率

设置点写入/读取启用)设置 MR16 OP[1:0],为 FSP-OP(频率设置点操作模式)设置所有其他模式寄存器位来配置模式寄存器设置) 进行高频或中频操作所需的设置,并设置 MR16 OP[5:4]以选择命令总线训练模式。

在进入命令总线训练之前, LPDDR5 SDRAM 将从 FSP-OP[x] 运行。在 DQ[7] 被驱动为高电平时进入命令总线训练时, LPDDR5 SDRAM 将根据 MR16 OP 自动切换到活动 FSP 寄存器集 FSPOP[x]、 FSP-OP[y] 或 FSP-OP[z] [5:4] 并在训练期间使用活动寄存器设置。当 DQ[7] 被驱动为低电平时命令总线训练退出时, LPDDR5 SDRAM 将自动切换回原始 FSP 寄存器组 FSP-OP[x],返回到训练前运行的“已知良好”状态。 VREF(CA) 的训练值不由 DRAM 保留在 FSP-OP[y] 或FSP-OP[z] 寄存器中,必须在训练退出后写入寄存器。

LPDDR5 SDRAM可以通过MR16 OP[7]设置来选择Command Bus Training CA阶段。如果 MR16 OP[7] =0B, DQ 输出由 CK_t 上升沿锁存的 CA 模式。如果 MR16 OP[7] =1B, DQ 输出由CK_t 下降沿锁存的 CA 模式。

CBT 模式期间需要差分 WCK 输入。因此, MR20 OP[3:2] 需要将 00B 设置为在进入 CBT 模式之前使用 CBT 训练的两个 FSP 集。此外, VRCG 应在使用 DVFSQ 的 CBT 模式期间打开。

1) 为命令总线训练模式 2 设置 MR13 OP[6]=1B。

2) 要进入命令总线训练模式,发出 MRW-1 命令,然后发出 MRW-2 命令以设置 MR16 OP[5:4]以选择 CBT 模式。无论 MR18 设置如何, WCK ODT 值固定为 40ohm; DQ ODT 和 NT-ODT

状态被关闭。 WCK_t 和 WCK_c 是用于通过切换捕获 DQ[7]、 DMI[0] 电平的输入引脚,而DMI[0] 是用于在 CBT 模式期间从 DQ[6:0] 捕获 VrefCA 设置的专用引脚。 WCK输入要求

为有效电平(WCK_t= Low and WCK_c = High),要求DQ[6:0]为有效电平,要求DQ[7]和DMI[0]在MRW-2命令输入前为低电平。在 tCBTWCKPRE_static 之后, WCK 信号可以切换并且在 DQ7 变高之前需要满足 tWCK2DQ7H。DQ[7] 被驱动为高电平,当 LPDDR5 SDRAM 通过 WCK 采样 DQ[7] 的高电平时, LPDDR5SDRAM 从 FSP-OP[x] 切换到 MR16 OP[5:4] 定义的 FSP 集,完成进入命令总线训练模式。进入命令总线训练模式时:

- DQ[6:0]成为设置VREF(CA)电平的输入引脚, VREF(CA)电平在内部DMI[0]上升沿被捕获,LPDDR5 SDRAM通过WCK采样DMI[0]的高电平。 DQ[6:0] 的输入电平需要在 tDStrain +

tDHtrain 期间保持不变,并且 DMI[0] 应在 tDHtrain 期间保持“高”,完成特定模式的锁存。

- DQ[6:0]成为输出引脚,通过命令地址总线从CS HIGH信号反馈捕获的值,直到DMI[0]的低电平被WCK采样。

- DMI[0] 用作通过 DQ[6:0] 更新 VREF(CA) 设置的选通引脚,也用作 DQ[6:0] 输出模式关闭开关。 LPDDR5 SDRAM 通过内部 DMI[0] 上升沿对 DQ[6:0] 电平进行采样,然后更新其 VREF(CA) 设置。

- 当DMI[0]的LOW电平被WCK采样时, DQ[6:0]输出模式关闭,输入模式开启。

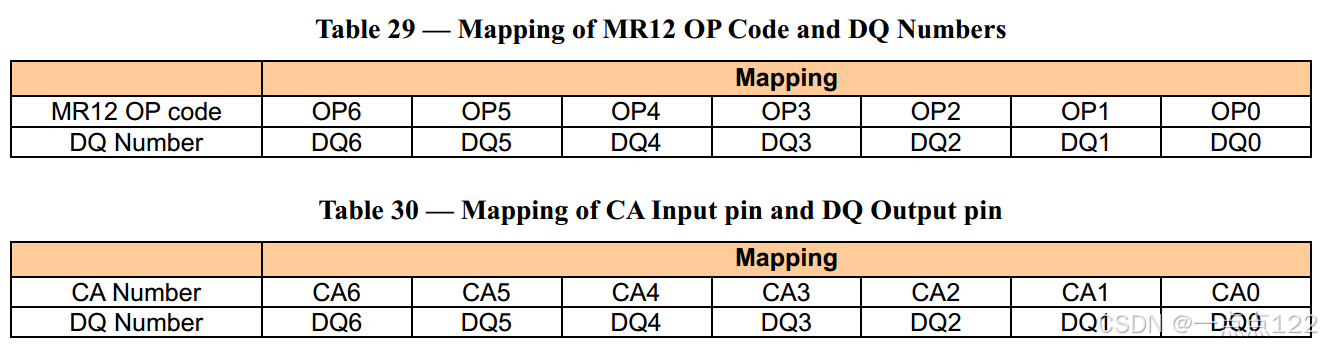

3) 在 DQ[7] 上升沿的 tDQ7HWCK 和 tDQ72DQ 之后, LPDDR5 SDRAM 可以使用 DQ[6:0] 的输入信号接受其 VREF(CA) 值变化。 LPDDR5 SDRAM 通过内部 DMI[0] 上升沿对 DQ[6:0] 进

行采样,然后更新通过 MR12 OP[6:0] 设置的现有值。 MR12 OP 代码和 DQ 之间的映射显示在表 29。 在进行下一训练步骤之前,至少需要一个 VREF(CA) 设置。

4) 在尝试锁存 CA 信息之前,新的 VREF(CA) 值必须“稳定”时间 tVREF_LONG。

5) 为验证接收器是否具有正确的 VREF(CA) 设置并进一步训练 CA 眼相对于时钟 (CK),锁存在 CA 总线上接收器的值异步输出到 DQ 总线。

6) 要退出命令总线训练模式,将 CK 频率更改为低频工作点,然后将 DQ[7] 驱动为低电平。在时间 tDQ7LWCK + tXCBT 之后发出 MRW 命令以设置 MR16 OP[5:4] = 00B。在时间 tMRD之后, LPDDR5 SDRAM 准备好进行正常操作。训练退出后, LPDDR5 SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器。命令总线训练可以从空闲或自刷新状态进入。在自刷新状态下进入 CBT 时, SDRAM 不需要处于掉电状态或深度睡眠模式。无论启动 CBT 的 SDRAM 状态如何,命令总线训练的进入和退出都是相同的。

命令总线训练可以从空闲或自刷新状态进入。进入 CBT 时, SDRAM 不得处于掉电状态或深度睡眠模式。无论启动 CBT 的 SDRAM 状态如何,命令总线训练的进入和退出都是相同的。

single-ranks 系统的训练序列

请注意,此处显示的示例假设初始低频、未终止操作点,训练高频或中频、终止操作点。蓝色文字为低频,红色文字是高频。可以从任何已知的良好操作点训练任何操作点。此示例假设以下条件。低频操作的频率设置点“X”和高频操作的频率设置点“Y”。

1) 设置 MR16 OP[1:0] 以启用写入频率设置点“Y”(FSP-WR[y])。

2) 为所有通道写入 FSP-WR[y] 寄存器以设置高频操作参数。

3) 设置 MR16 OP[5:4] 以选择 CBT 模式 (CBT[y])。

4) 发出 MRW-1 和 MRW-2 命令进入命令总线训练模式。

5) 将 DQ[7] 驱动为高电平,然后将 CK 频率更改为高频工作点。

6) 执行命令总线训练(VREF(CA)、 CS 和 CA)。

7) 通过将 DQ[7] 驱动为低电平来退出训练,在将 DQ[7] 驱动为低电平之前将 CK 频率更改为低频工作点,然后发出 MRW-1 和 MRW-2 命令以退出命令总线训练模式。当 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器(即,训练值不被保留内存)。

8) 通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将训练值写入 FSP-WR[y]。

9) 发出MRW-1和MRW-2命令切换到FSP-OP[y]开启终端,改变CK频率到高频工作点。此时Command Bus已经训练完成,可以执行其他训练或正常操作。

multiple-ranks 系统的训练序列

请注意,此处显示的示例假设初始低频、未终止操作点,训练高频或中频、终止操作点。蓝色文字是低频,红色文字是高频。可以从任何已知的良好操作点训练任何操作点。此示例假设以下条件。低频操作的频率设置点“X”和高频操作的频率设置点“Y”。 FSP-WR[x] 和 FSP-OP[x] 是终止秩和非终止秩的初始状态。在开始命令总线训练之前,需要使用 FSP-OP[x] 和 FSP-OP[y] 禁用终止等级和非终止等级的 WCK ODT 和 NT-ODT: WCK ODT: MR18 OP[2 :0]=000B, NT-ODT: MR11 OP[3]=0B或 MR41 OP[7:5]=000B。

之所以建议禁用 WCK ODT 和 NT-ODT 设置,是为了确保 WCK、 DQ[7:0] 和 DMI 输入有足够的幅度。由于这些信号引脚在 CBT 模式期间应用了多种功能,例如控制进入/退出 CBT 模式和捕获DQ[7] 输入电平。

1) 设置 MR16 OP[1:0] 以启用写入两个级别的频率设置点“Y”(FSP-WR[y])。

2) 为所有通道写入 FSP-WR[y] 寄存器以设置两个等级的高频操作参数。

3) 发出 MRW-1 和 MRW-2 命令以在终端列上进入命令总线训练模式 (CBT[y]):设置MR16 OP[5:4] 以选择 CBT 模式 (CBT[y])。

4) 在终止等级(或所有等级)上将 DQ[7] 驱动为高电平,然后将 CK 频率更改为高频工作点。

5) 在终端等级(VREF(CA)、 CS 和 CA)上执行命令总线训练。

6) A 将 CK 频率更改为低频工作点,然后在终止等级(或所有等级)上将 DQ[7] 驱动为低电平。当 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器(即,训练值不被保留内存)

7) 发出 MRW-1 和 MRW-2 命令以退出终端列上的命令总线训练模式(正常操作):设置 MR16 OP[5:4] 以选择正常操作。

8) 通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将训练值写入终止等级的 FSP-WR[y]。

9) 发出 MRW-1 和 MRW-2 命令以在非终止列上进入命令总线训练模式 (CBT[y]):设置 MR16 OP[5:4] 以选择 CBT 模式 (CBT[y])。但是,保持 DQ[7] 为低电平。

10)发出 MRW-1 和 MRW-2 命令将终止等级切换到 FSP-OP[y] 以打开终止。然后改变CK 频率到高频工作点。

11)在非终止(或所有)等级上将 DQ[7] 驱动为高电平。非终止等级现在将使用 FSP-OP[y]。

12)在非终止等级(VREF(CA)、 CS 和 CA)上执行命令总线训练。

13)发出 MRW-1 和 MRW-2 命令将终止等级切换到 FSP-OP[x] 以关闭终止。

14)通过在非终止等级上将 DQ[7] 驱动为低电平来退出训练,将 CK 频率更改为低频工作点,并发出 MRW-1 和 MRW-2 命令以退出命令总线训练模式。当 DQ[7] 被驱动为低电平并且SDRAM 通过 WCK 采样 DQ[7] 的低电平时, SDRAM 将自动切换回训练前使用的 FSP-OP 寄存器(即,训练值不被保留内存)。

15)通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将非终止等级的训练值写入 FSP-WR[y]。

16)发出MRW-1和MRW-2命令将terminating rank切换到FSP-OP[y]开启termination,改变CKfrequency到高频工作点。此时命令总线已针对两个等级进行训练,并且可以执行其他训练或正常操作。

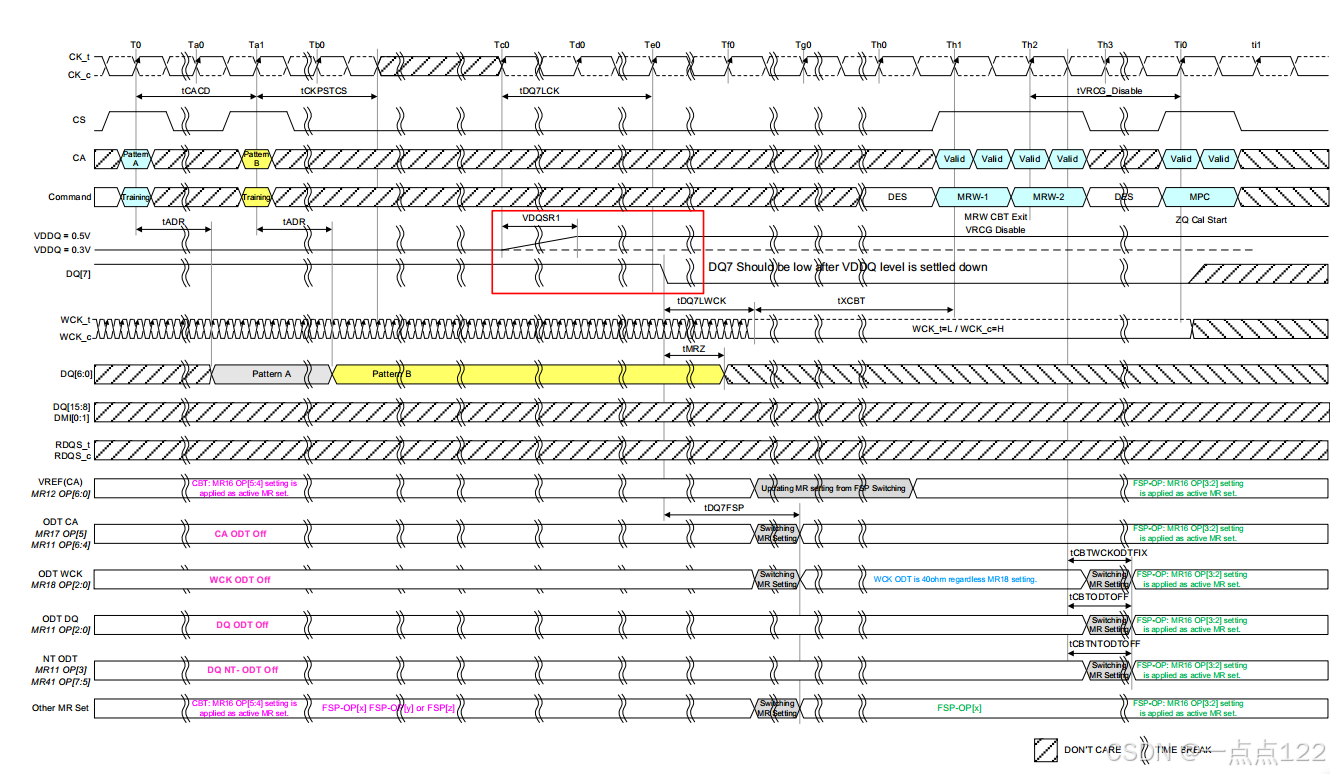

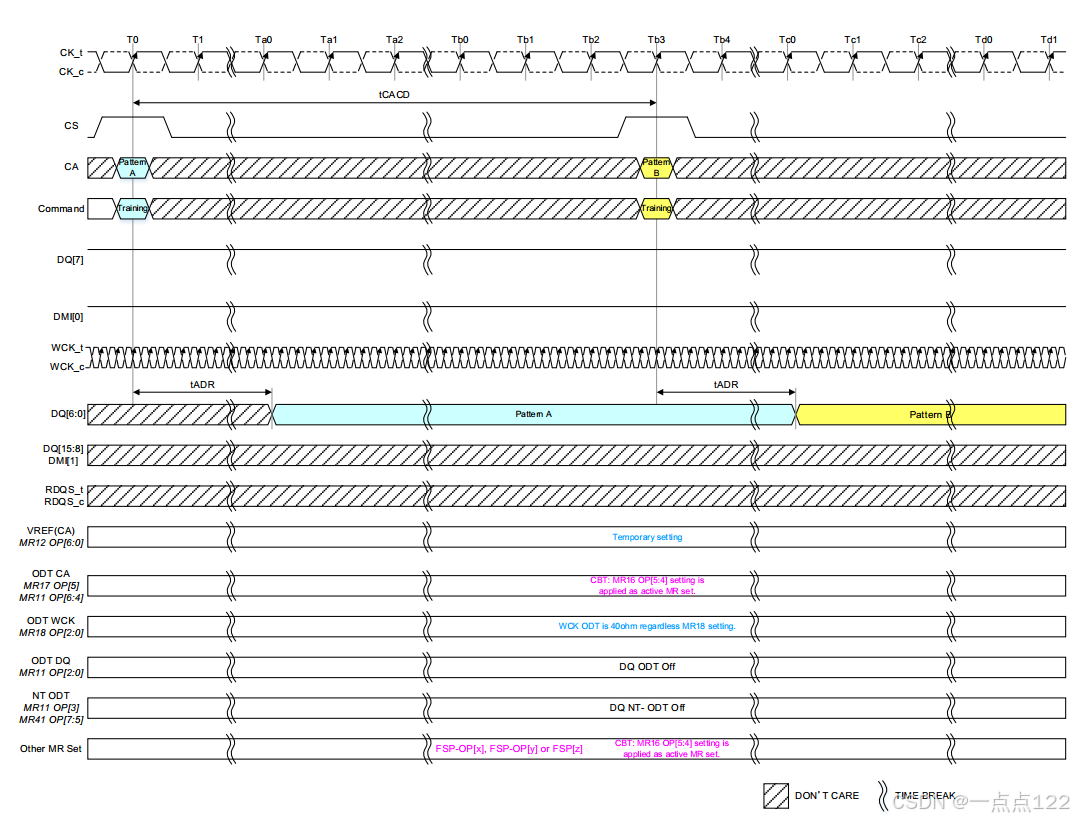

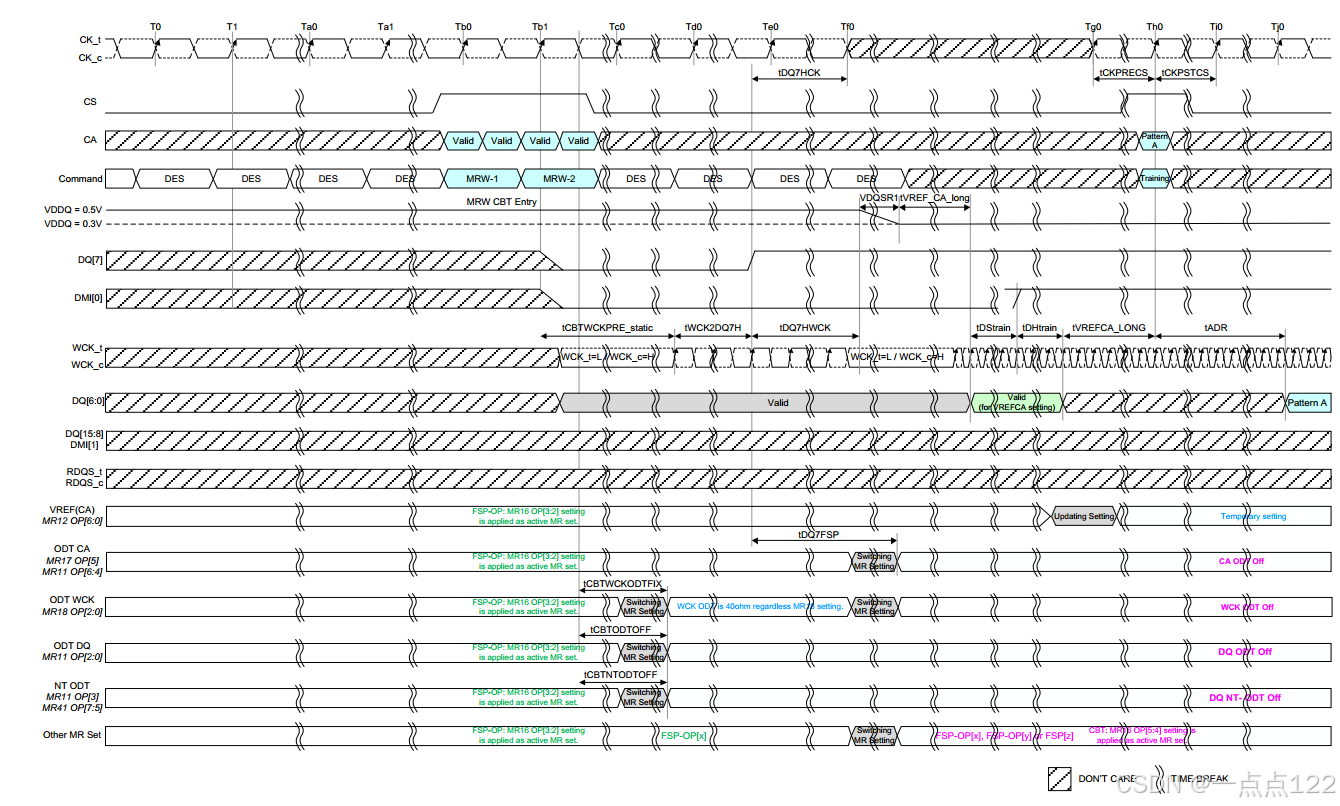

命令总线训练模式 2 的基本时序图如图 33–37 所示。

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 DQ[6:0] 信号电平的值由 DMI[0] 上升沿采样。在时间 tVREFCA_long 之后, DRAM 临时新其 MR12 的VREFCA 设置。

注 5 tVREFCA_long 可能会减少到 tVREFCA_short。

注 6 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。如果交替FSP-OP 禁用了 ODT CA,那么终止将不会在 CA 总线训练模式下启用。

注 7 WCK ODT 状态设置为固定值, DQ ODT/NT-ODT 在 CBT 操作期间关闭。

注 8 只要频率在每个频率模式 (MR18 OP[3]) 的允许范围内,在 CBT 操作期间不关心 WCK 频率。 WCK 切换可以在 tDQ72DQ 期间和 tDHtrain 之后停止,但 WCK 对应在静态电平驱动,因为WCK_t = 低和 WCK_c = 高。在 DQ[7] 或 DMI[0] 再次改变之前, WCK 应该切换以满足 tWCK2DQ7H 和 tDStrain。

注 9 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。

注 10 CBT 阶段: MR16 OP[7] = 0B

图 33 — 进入命令总线训练模式和 CA 训练模式输入, VREF(CA) 值更新(WCK 频率变化)

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 DQ[6:0] 信号电平的值由 DMI[0] 上升沿采样。在时间 tVREFCA_long 之后, DRAM 临时更新其 MR12 的VREFCA 设置。

注 5 tVREFCA_long 可能会减少到 tVREFCA_short。

注 6 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。如果交替FSP-OP 禁用了 ODT CA,那么终止将不会在 CA 总线训练模式下启用。

注 7 WCK ODT 状态设置为固定值, DQ ODT/NT-ODT 在 CBT 操作期间关闭。

注 8 无论 CK:WCK 比率如何,在CBT 操作期间设置固定的 WCK 频率。只要频率在每个频率模式 (MR18 OP[3]) 的允许范围内, WCK 频率在 CBT 操作期间无关紧要。 WCK 切换可以在 tDQ72DQ 期间和 tDHtrain 之后停止,但 WCK 对应在静态电平驱动,因为 WCK_t = 低和 WCK_c= 高。在 DQ[7] 或 DMI[0] 再次改变之前, WCK 应该切换以满足 tWCK2DQ7H 和 tDStrain。

注 9 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。

注 10 CBT 阶段: MR16 OP[7] = 0B

图 34 — 进入命令总线训练模式和带有 VREF(CA) 值更新的 CA 训练模式输入(固定 WCK 频率)

注 1 DQ[6:0] 信号电平的值由 DMI[0] 上升沿采样。在时间 tVREFCA_long 之后, DRAM 临时更新其 MR12 的VREFCA 设置。

注 2 要将 DQ 引脚的读取模式更改为写入模式,必须将 DMI[0] 驱动为低电平。

注 3tVREFCA_long 可能会减少到 tVREFCA_short。

图 35 — CA 模式输入/输出到 Vref 设置输入

图 36 — 连续 CA 训练模式输入/输出

注 1 CK 需要在 DQ[7] 被驱动为低电平之前满足 tDQ7LCK。

注2 要求DQ[7]、 DMI[0]和WCK信号为有效电平,直到满足MRW命令退出该模式引起的tMRD。

注 3 在 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 切换采样 DQ[7] 的低电平之后, SDRAM ODT_CA 将恢复到命令总线训练模式进入之前由 FSP-OP 定义的状态/值,即。 , 原始频率设定点 (FSP-OP)。示例: 如果 SDRAM 使用 FSP-OP[x]、 FSP-OP[y] 或 FSP-OP[z] 进行训练,那么它将在 DQ[7] 被驱动为低电平后切换到 FSP-OP[x],并且通过 WCK 切换采样低电平。

注 4 训练值不由 SDRAM 保留,必须在返回以训练频率运行之前写入 FSP-OP 寄存器组。示例: VREFCA 将返回到原始设定点中编程的值。

注 5 WCK 在 CBT 模式下不需要与时钟信号同步。

图 37 — 退出命令总线训练模式

4.2.2.5 命令总线训练模式 2(启用 DVFSQ 的 FSP)

CBT 用于启用 DVFSQ 的操作,请按照以下步骤操作。本节适用于支持 DVFSQ 功能的 SDRAM。红色文本是 DVFSQ 禁用模式,蓝色文本是 DVFSQ 启用模式

1) 设置 MR16 OP[1:0] 以启用写入频率设置点“Y”(FSP-WR[y])。

2) 为所有通道写入 FSP-WR[y] 寄存器以设置启用 DVFSQ 的操作参数。

3) 禁用 SoC ODT 并设置 MRW MR17 OP[2:0]=000 B.

4) 在背景 ZQ 校准模式的情况下,发出 MRW MR28 以设置 ZQ_STOP(MR28 OP[1]=1B)并等待 tZQSTOP。

5) 设置为 VRCG VREF 高电流模式: MR16 OP[6]=1B 并等待 tVRCG 启用

6) 通过 MRW-1 和 MRW-2 命令设置 MR16 OP[5:4] 以选择 CBT 模式 (CBT[y]):进入 CBT

模式。

7) 将 DQ[7] 驱动为高电平,然后将 VDDQ 斜坡下降至标称值 0.3V。 (请勿在此处训

练!)对于 VDDQ 转换率 VDQSR1,请参阅“DVFSQ 模式”规范。

8) VREFCA 更新时序, VDDQ 上升完成后需要 tVREF_CA_long。

9) 执行命令总线训练(VREF(CA)、 CS 和 CA)。

10) 在 CBT 退出之前,将 VDDQ 斜升至 0.5V 标称值。对于 VDDQ 转换率 VDQSR1,请参阅“DVFSQ 模式”规范。在将 DQ[7] 驱动为低电平之前,将 CK 频率更改为 FSP[x] 频率工

作点

11) 通过将 DQ[7] 驱动为低电平退出训练,当 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK采样 DQ[7] 的低电平时, SDRAM 将自动切换回之前使用的 FSP-OP 寄存器训练(即训练值

不被 SDRAM 保留)。

12) 等待 tXCBT

13) 发出 MRW-1 和 MRW-2 命令以退出命令总线训练模式,并根据需要设置 VRCG VREF 高电流模式禁用。发布 ZQ_Stop(设置 MR28 OP[1]=0B)以启动背景 ZQ 校准。

14) 等待 tZQCALx 并发出 ZQCal Latch 命令。

15) 通过向 SDRAM 发出 MRW-1 和 MRW-2 命令并设置所有适用的模式寄存器参数,将训练值写入 FSP-WR[y]。

16) 发出MRW-1和MRW-2命令切换到FSP-OP[y]开启终端,改变CK频率和VDDQ电平到FSP-OP[y]工作点。此时Command Bus已经训练完成,可以执行其他训练或正常操作。

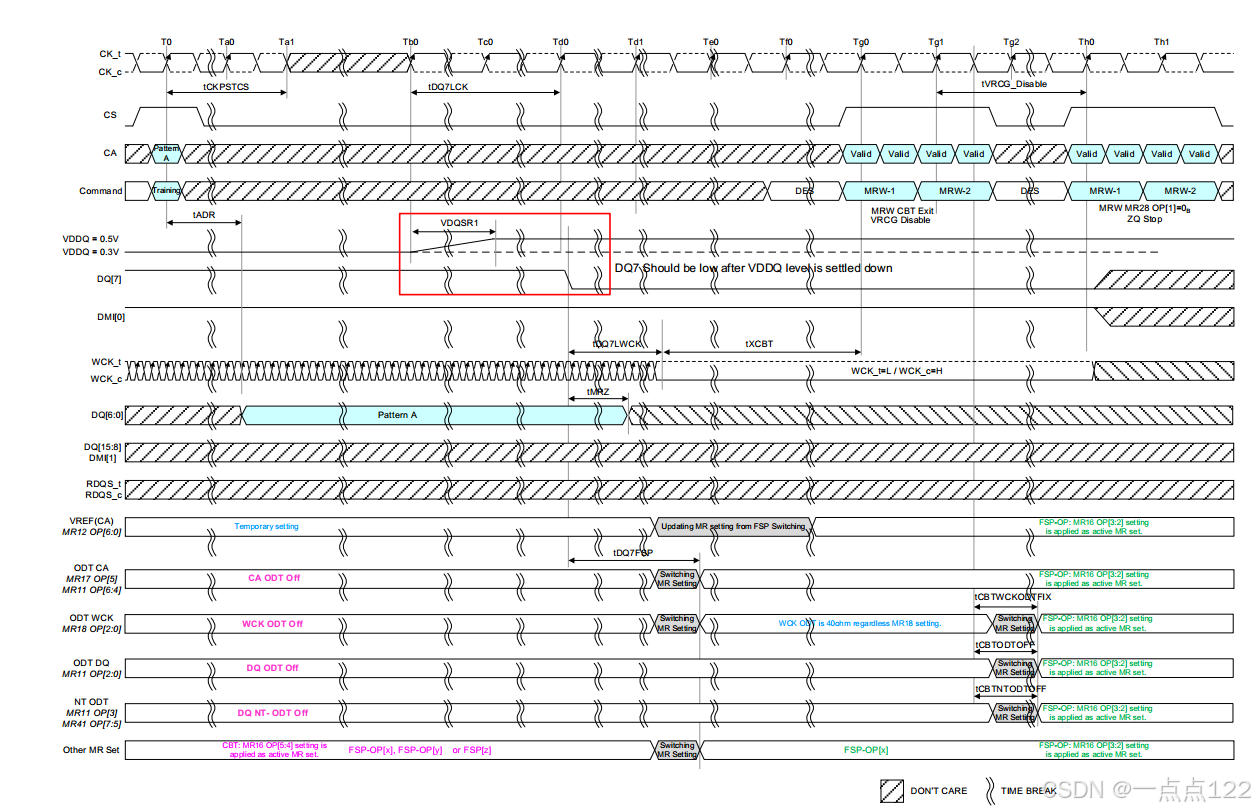

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 DQ[6:0] 信号电平的值由 DMI[0] 上升沿采样。在时间 tVREFCA_long 之后, DRAM 临时更新其 MR12 的VREFCA 设置。

注 5 tVREFCA_long 可能会减少到 tVREFCA_short。

注 6 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后,SDRAM 将切换其 FSP-OP 寄存器以使用备用(即,非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到FSP-OP[1]。所有经营在进入命令总线训练之前,应将参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。

注 7 CA ODT、 WCK ODT 和 DQ ODT/NT-ODT 在 CBT 和 DVFSQ 操作期间关闭。

注 8 在 tDQ72DQ 期间,WCK 可以在 FSP 更改后停止并更改频率。

注 9 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。

注 10 CBT 阶段: MR16 OP[7] = 0B

图 38 — 进入命令总线训练模式和带有 VREF(CA) 值更新的 CA 训练模式输入(后台 ZQ 校准)

注 1 在 tDQ7HCK 之后,时钟 (CK) 可以随时停止或改变频率。

注 2 输入时钟条件应满足tCKPRECS。

注 3 继续驱动 CK 并保持 CS 引脚为低电平,直到 DQ[7] 变为高电平后的 tDQ7HCK。

注 4 DQ[6:0] 信号电平的值由 DMI[0] 上升沿采样。在时间 tVREFCA_long 之后, DRAM 临时更新其 MR12 的VREFCA 设置。

注 5 tVREFCA_long 可能会减少到 tVREFCA_short。

注 6 在 DQ[7] 被驱动为高电平并且 SDRAM 在命令总线训练模式下通过 WCK 切换采样 DQ[7] 的高电平后, SDRAM将切换其 FSP-OP 寄存器以使用备用(即非活动) 放。示例:如果 SDRAM 当前正在使用 FSP-OP[0],则当 DQ[7] 被驱动为高电平并且通过 WCK 切换采样为高电平时,它将切换到 FSP-OP[1]。在进入命令总线训练之前,应将所有操作参数写入备用模式寄存器,以确保 ODT 设置、 RL/WL/nWR 设置等设置为正确的值。

注 7 CA ODT、 WCK ODT 和 DQ ODT/NT-ODT 在 CBT 和 DVFSQ 操作期间关闭。

注 8 在 tDQ72DQ 期间,WCK 可以在 FSP 更改后停止并更改频率。

注 9 在命令总线训练进入之前和之后可以使用相同的 FSP 和时钟频率。注 10 CBT 阶段: MR16 OP[7] = 0B

图 39 — 使用 VREF(CA) 值更新进入命令总线训练模式和 CA 训练模式输入(基于命令的 ZQ 校准)

注 1 CK 需要在 DQ[7] 被驱动为低电平之前满足 tDQ7LCK。

注 2 要求DQ[7]、 DMI[0]和WCK信号为有效电平,直到满足MRW命令退出该模式引起的tMRD。

注 3 在 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 切换采样 DQ[7] 的低电平之后, SDRAM ODT_CA 将恢复到命令总线训练模式进入之前由 FSP-OP 定义的状态/值,即。 , 原始频率设定点 (FSP-OP)。示例: 如果 SDRAM 使用 FSP-OP[x]、 FSP-OP[y] 或 FSP-OP[z] 进行训练,那么它将在 DQ[7] 被驱动为低电平后切换到 FSP-OP[x],并且通过 WCK 切换采样低电平。

注 4 训练值不由 SDRAM 保留,必须在返回以训练频率运行之前写入 FSP-OP 寄存器组。示例: VREFCA 将返回到原始设定点中编程的值。

注 5 WCK 在 CBT 模式下不需要与时钟信号同步。

图 40 — 退出命令总线训练模式(后台 ZQ 校准)

注 1 CK 需要在 DQ[7] 被驱动为低电平之前满足 tDQ7LCK。

注 2 要求DQ[7]、 DMI[0]和WCK信号为有效电平,直到满足MRW命令退出该模式引起的tMRD。

注 3 在 DQ[7] 被驱动为低电平并且 SDRAM 通过 WCK 切换采样 DQ[7] 的低电平之后, SDRAM ODT_CA 将恢复到命令总线训练模式进入之前由 FSP-OP 定义的状态/值,即。 , 原始频率设定点 (FSP-OP)。示例: 如果 SDRAM 使用 FSP-OP[x]、 FSP-OP[y] 或 FSP-OP[z] 进行训练,那么它将在 DQ[7] 被驱动为低电平后切换到 FSP-OP[x],并且通过 WCK 切换采样低电平。

注 4 训练值不由 SDRAM 保留,必须在返回以训练频率运行之前写入 FSP-OP 寄存器组。示例: VREFCA 将返回到原始设定点中编程的值。

注 5 WCK 在 CBT 模式下不需要与时钟信号同步。

图 41 — 退出命令总线训练模式(基于命令的 ZQ 校准)

4.2.3 CA VREF Training

TBD

-

Vref CA Training 在Command Bus Training完成

-

MR14 OP[6] : VREF(DQ) Range

4.2.4 DQ VREF Training

TBD

-

Vref DQ Training 在DQ Training完成

-

MR14 OP[5:0] : VREF(DQ) Setting

4.2.5 WCK2CK Leveling

4.2.5.1 WCK2CK Leveling Mode(LPDDR4中调用的write-leveling)

调整CK-to-WCK关系,保证WCK2CK-Sync。操作时, LPDDR5 SDRAM 提供 WCK2CK 调平功能,以补偿影响 WCK2CKSync 的 CK 到 WCK 时序偏差。手术。 SDRAM比较WCK上升沿和CK上升沿的相位,然后将WCK2CK相位检测结果异步反馈给内存控制器。在完成 WCK2CK Leveling 之后,确定tWCK2CK,即 CK-to-WCK 关系,并进行 WCK2CK-Sync。将以优化的保证金执行操作。

内存控制器参考 WCK2CK-Sync 反馈来调整每个 WCK_t/WCK_c 信号对的 CK-to-WCK 关系。所有数据位(WCK_t[0]/WCK_c[0] 的 DQ[7:0] 和 WCK_t[1]/WCK_c[1] 的 DQ[15:8])将训练反馈传

送到控制器。

在进入 WCK2CK 调平之前,需要将 CKR 模式设置为 2:1。

当模式寄存器 MR18-OP[6] 设置为高电平时, LPDDR5 SDRAM 进入 WCK2CK 调平模式。进入WCK2CK 调平模式时, DQ 引脚的状态未定义。在 WCK2CK Leveling 模式下,只允许使用DESELECT 命令,或 MRW 命令退出 WCK2CK Leveling 操作。 WCK2CK 调平完成后,当 MR18-OP[6] 复位为低电平时, SDRAM 退出 WCK2CK 调平模式。

WCK2CK Leveling 应该在写训练之前执行。

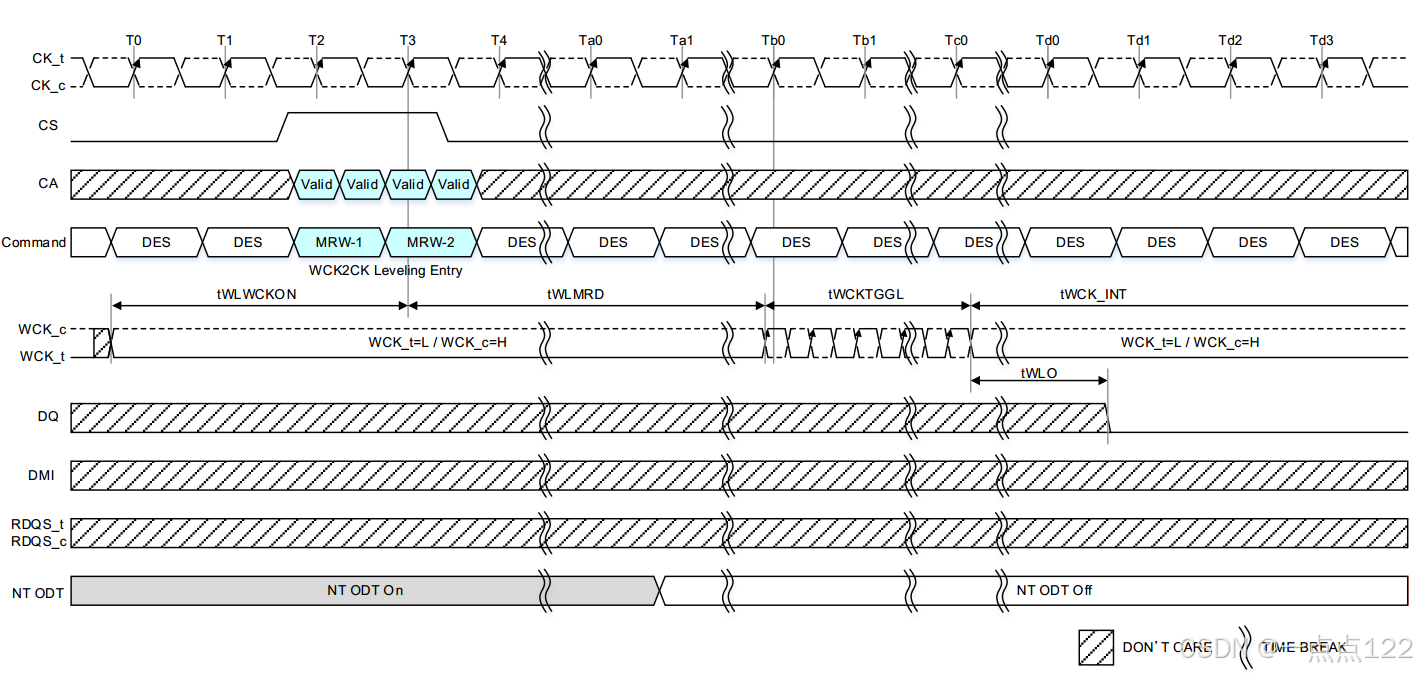

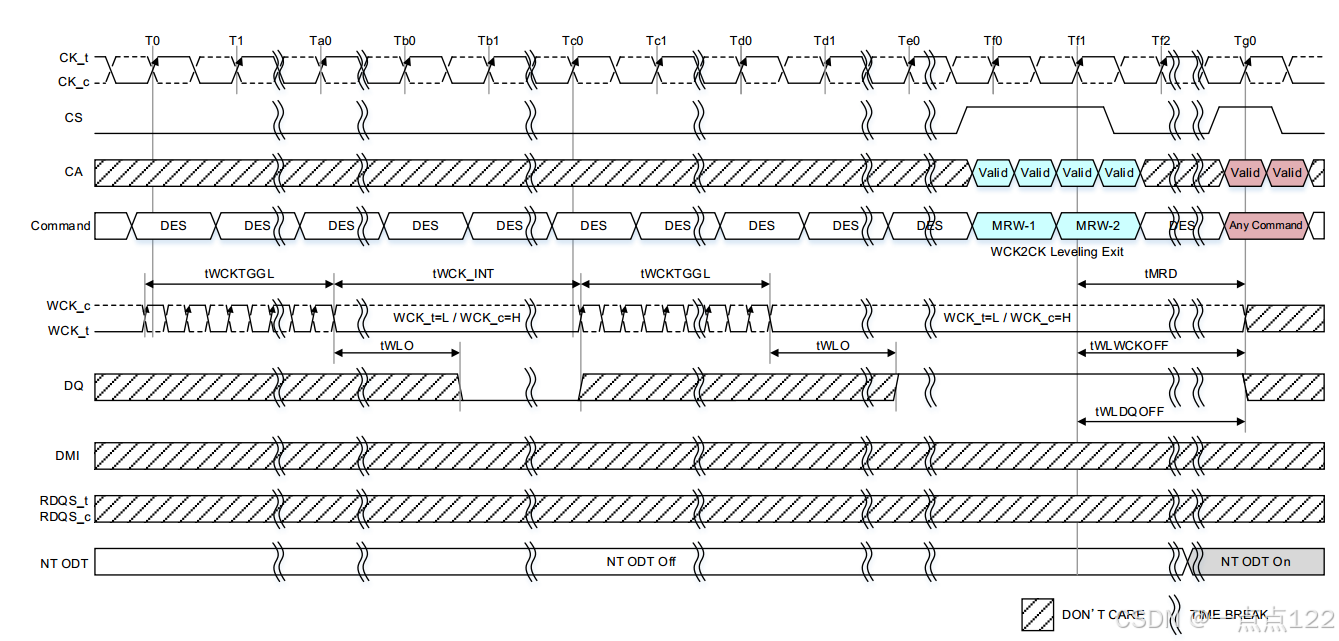

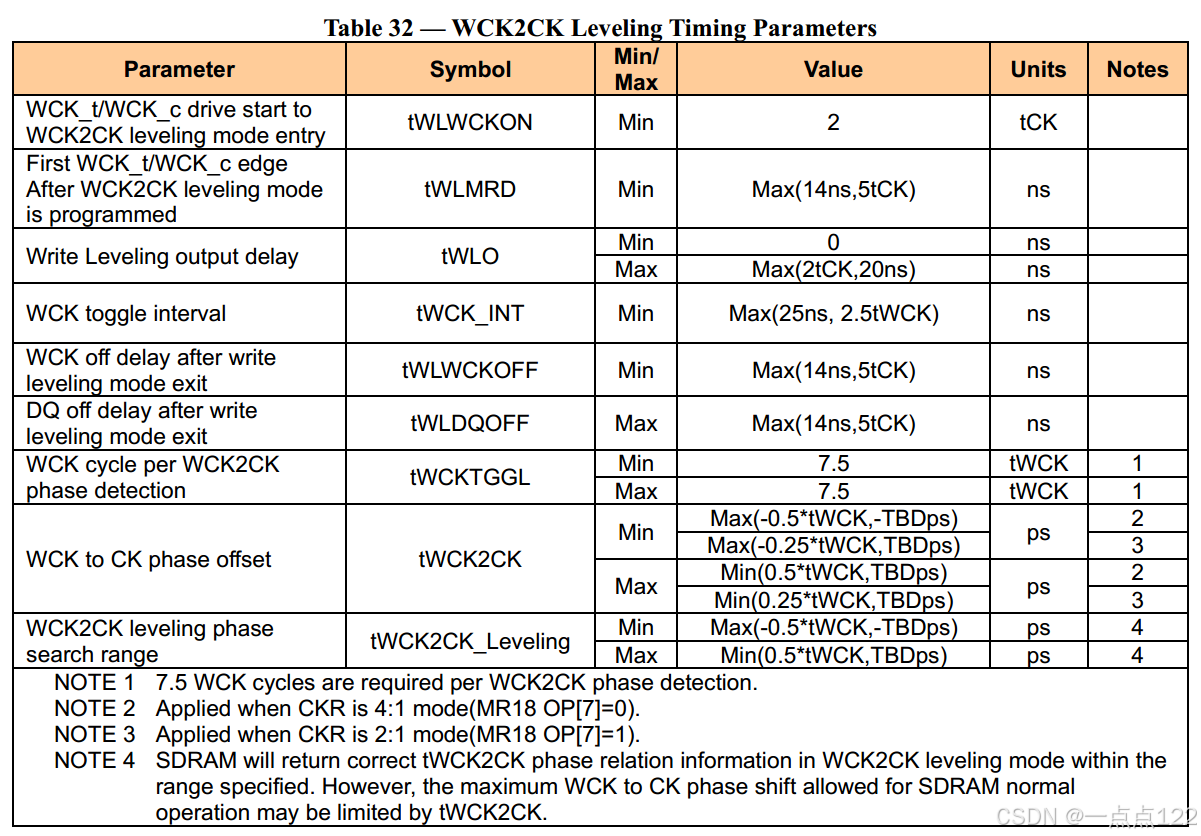

WCK2CK 调平示例显示在图 42和图 43,下文将对附图进行具体说明。

4.2.5.2 WCK2CK 调平程序及相关交流参数

注 1 WCK 必须在 WCK2CK 调平进入之前驱动 tWLWCKON。

注 2 WCK 必须恰好切换7.5 个周期 (tWCKTGGL= 7.5tWCK)。

注 3 DQ 总线上的 WCK2CK 相位检测结果为低,因为 WCK 相位早于 CK 相位。注 4 在此示例中,启用了 NT ODT。

图 42 — WCK2CK 调平输入和调平结果输出

注 1 当 WCK 阶段开始晚于 CK 阶段时, DQ 输出从低电平变为高电平。

注 2 只有当控制器驱动WCK_t=L/WCK_c=H 时,才允许控制器改变 WCK 相位。

注 3 WCK 必须恰好切换 7.5 个周期(tWCKTGGL=7.5tWCK)。

注 4 在此示例中,启用了 NT ODT。

图 43 — 连续的 WCK2CK 调平和 WCK2CK 调平退出

具体说明为图 42和图 43。

1. 开始将 WCK_t 驱动为低电平并将 WCK_c 驱动为高电平。

2. 通过设置 MR18-OP[6]=1B 进入 WCK2CK 调平模式。在WCK2CK调平模式下, WCK与CK的频率比必须为2:1,因为无论WCK2CK模式(4:1或2:1), WCK前导码的频率都是CK的2倍。即使通过 MR11 OP[3] 和 MR41 OP[7:5]: NT DQ ODT 启用 NT-ODT, NT-ODT 也将被禁用。

3. 在提供第一个 WCK 信号切换输入之前等待时间 tWLMRD。延迟时间 tWLMRD(MAX) 取决于控制器。

4. 将 WCK 信号切换 7.5 个周期以进行 WCK2CK 相位检测。由于第一个上升沿不稳定, SDRAM可能捕获也可能不捕获 WCK_t 的第一个上升沿。因此,在 WCK2CK 训练模式期间,每个 WCK输入信号都需要提供恰好 7.5 个周期的 WCK 信号输入。在时间 tWLO 之后的所有 DQ 位上, SDRAM 在 WCK 切换期间提供最后捕获的 WCK2CK 相位信息的异步反馈。如果 WCK 相位早于CK 相位, DQ 输出为低电平;如果 WCK 相位晚于 CK 相位,则 DQ 输出为高电平。控制器必须在满足 tWLO 后对 DQ 上的相位关系结果进行采样。

5. 控制器参考 SDRAM 提供的反馈来递增或递减 WCK_t 和 WCK_c 延迟设置。只有当控制器将WCK_t 驱动为低电平并将 WCK_c 驱动为高电平时,控制器才能调整 WCK 延迟设置,以防止WCK 信号中出现任何毛刺。来自控制器的 WCK 搜索范围定义为 tWCK2CK_leveling ac 参数。参考中的 tWCK2CK_leveling 值表 32。

6. 重复步骤 4 到步骤 5,直到建立正确的 WCK_t/WCK_c 延迟。

7. 通过设置 MR18-OP[6]=0B 退出 WCK2CK 调平模式。如果 NT-ODT 由 MR11 OP[3] 和 MR41 OP[7:5]: NT DQ ODT 启用, NT-ODT 将恢复启用。

4.2.6 占空比调节器 (DCA)

LPDDR5 SDRAM 支持模式寄存器可调的 WCK DCA,允许内存控制器调整 DRAM 内部 WCK 时钟树占空比,以补偿系统占空比误差。为每个字节提供单独的 DCA(DCAL 用于低字节调整, DCAU 用于高字节调整。)。 WCK DCA 仅在 WCK 高频模式下允许(MR18 OP[3]=1B)。 WCK DCA 在 WCK低频模式 (MR18 OP[3]=0B) 下不保证, DCA 代码 MR30 OP[7:0] 在 WCK 低频模式下应设置为0000 0000B。

WCK DCA 位于 WCK 分频器之前或等效位置。 WCK DCA 将在以下操作期间影响 WCK 占空比:

- 读

- 读32

- 写

- 写32

- 屏蔽写入

- 模式寄存器读取

- 读先进先出

- 写先进先出

- 读取 DQ 校准

- 占空比监视器

控制器可以通过 DCAL 的 MR30 OP[3:0] 和 DCAU 设置的 MR30 OP[7:4] 调整占空比,并可以通过多种不同方式确定 DCA 的最佳模式寄存器设置。此函数调整 SDRAM 内部 WCK 占空比(静态)。

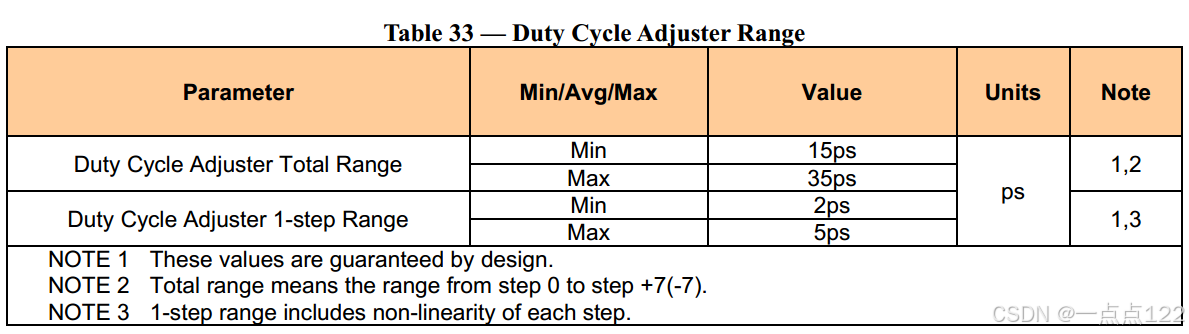

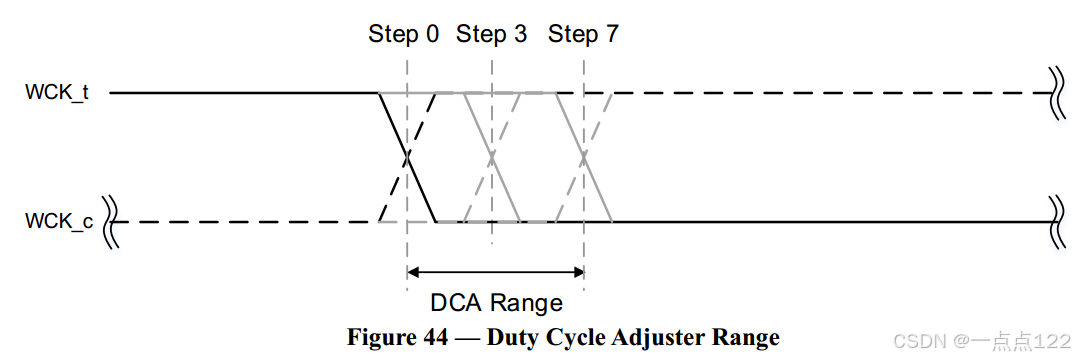

4.2.6.1 占空比调节范围

步骤 0 到步骤 7(-7) 之间的步骤范围如下。第 N 步和第 N+1 步之间的实际值差异被定义为在规格范围内,因为改变 DCA 代码导致的占空比变化不是线性的。

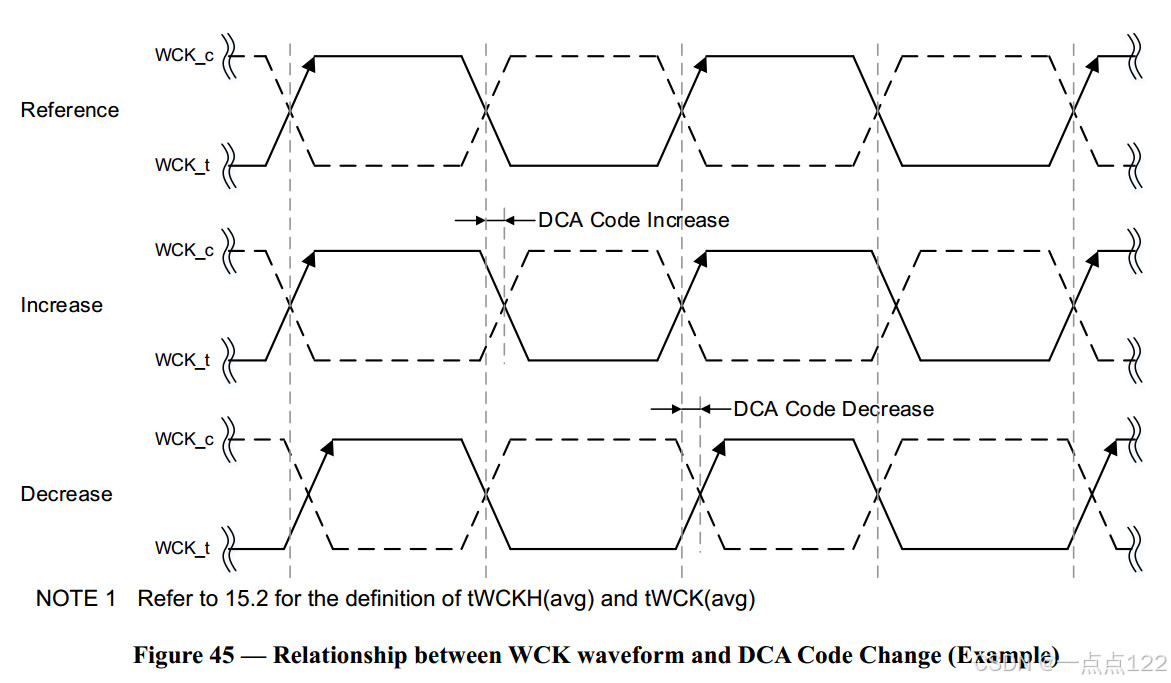

4.2.6.2 WCK波形与DCA代码变化的关系

DAC代码变化的基本操作如下。

DCA代码更改后,建议重新执行WCK2CK调平。

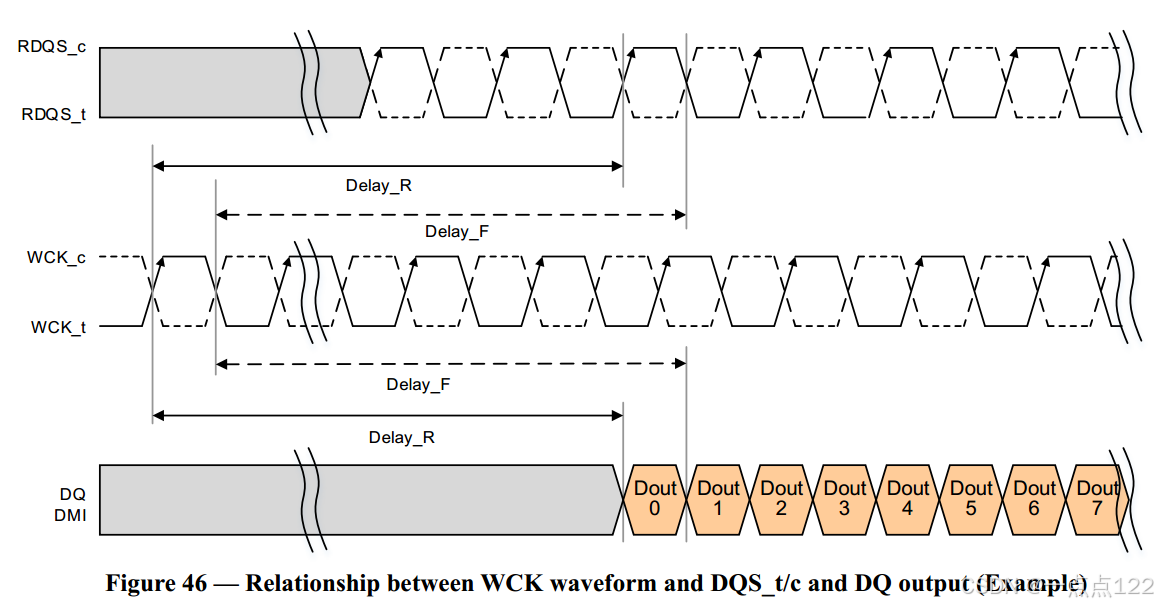

4.2.6.3 DCA Code Change与DQ输出/RDQS时序的关系

WCK DCA代码变化对DQ Output和RDQS的影响如下。 WCK_t 的上升沿影响RDQS_t 的上升沿和偶数据输出。 WCK_t 的下降沿影响RDQS_t 的下降沿和奇数据输出。互补信号(WCK_c 和 RDQS_c)与真实信号相同。

DCA代码变化与延迟时间变化(Delay_R/F)之间的关系只能定性定义。

4.2.7 读取 DCA(占空比调节器)

LPDDR5X SDRAM 具有读取 DCA 功能作为可选功能。读取 DCA 也是模式寄存器可调的,以允许内存控制器调整 DRAM 读取数据占空比以补偿专用于读取 DQ 的占空比失真。为每个字节提供单独的读取 DCA(RDCAL 用于低字节读取调整, RDCAU 用于高字节读取调整。)。

读取 DCA 位于调整后的 WCK 时钟树上,以提供专门的读取占空比调整。读取 DCA 将影响后续操作期间的读取数据。

read

read32

mode register read

read FIFO

read DQ calibration

控制器可以通过用于 RDCAL 设置的 MR69 OP[3:0] 和用于 RDCAU 设置的 MR69 OP[7:4] 调整读取占空比,并可以通过多种不同方式确定 DCA 的最佳模式寄存器设置。由于Read DCA受到WCKDCA的影响, read DCA训练应该在WCK DCA训练之后进行。

要获得适当的占空比失真调整,应以适当的方式执行 LPDDR5 SDRAM WCK 调整和同步。

MR24 OP[3]表示是否支持读取DCA:

MR24 OP[3]: 0B = 不支持读取 DCA MR24

OP[3]: 1B = 支持读取 DCA。

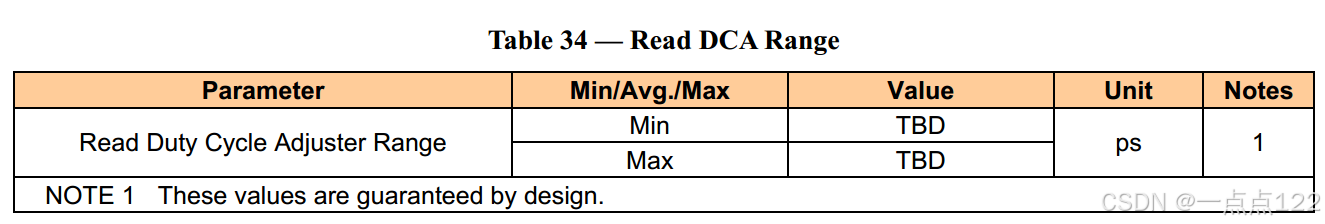

4.2.7.1 读取占空比调节器范围

步骤 0 到 7 (-7) 之间的步长范围如下。无法定义第 N 步和第 N+1 步之间的实际值差异,因为通过更改读取 DCA 代码改变占空比的变化不是线性的。

详细读取DCA代码及时序关系,请参考4.2.6.1.

4.2.7.2 Read DCA Code Change与DQ输出/RDQS时序的关系

Read DCA代码变化对DQ Output和RDQS的影响如下。 WCK_t 的上升沿影响RDQS_t 的上升沿和偶数据输出。 WCK_t 的下降沿影响RDQS_t 的下降沿和奇数据输出。互补信号(WCK_c 和 RDQS_c)与真实信号相同。

Read DCA代码变化与延迟时间变化(Delay_R/F)之间的关系只能定性定义。

参考信息请参考图 46.

4.2.8 占空比监视器 (DCM)

4.2.8.1 DCM功能说明

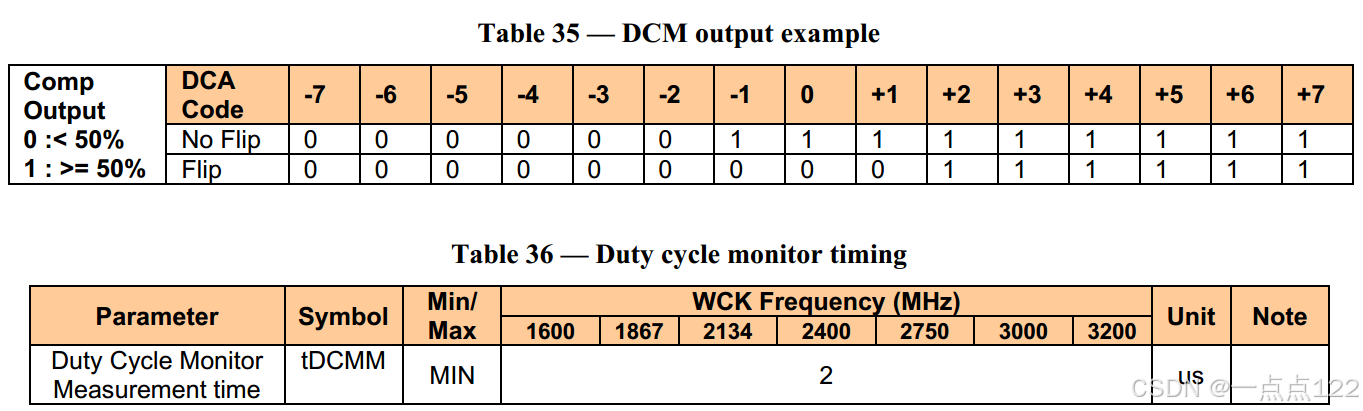

LPDDR5 SDRAM 设备具有占空比监视器 (DCM),允许内存控制器监视 SDRAM 内部 WCK 时钟树中的 WCK 占空比失真。当启用 DCM 时,低字节和高字节同时执行 DCM 功能。为每个字节提供两个单独的占空比结果: DCML0 和 DCML1 用于低字节, DCMU0 和 DCMU1 用于高字节。

DCM 操作通过写入 MR26 OP[0] = 1B 来启动。设置 MR26 OP[0] = 0B 终止 DCM 操作。在启动DCM 操作之前,应根据 7.2.1.2 执行 WCK2CK SYNC - 快速同步操作。启用 DCM 操作时需要连续切换 WCK 输入,直到通过写入 MR26 OP[0] = 0B 停止 DCM 操作后的 TBD。

如果存在 DCM 电路滞后, DCM 结果可能不准确。为了提高此功能的准确性, DCM 支持通过将 MR26 OP[1] 设置为相反状态然后重复测量来翻转输入。

MRW[DCM Flip] 和 MRW[DCM Stop] 将捕获 DCM 结果。 DCM 结果由 DCM 翻转位 (MR26 OP[1])的状态决定。

- DCM Flip = 0:将使用 DCML0 和 DCMU0

- DCM Flip = 1:将使用 DCML1 和 DCMU1

DCM 电路监控读/写 WCK 时钟路径。 DCM 需要高于 1600MHz 的 WCK。

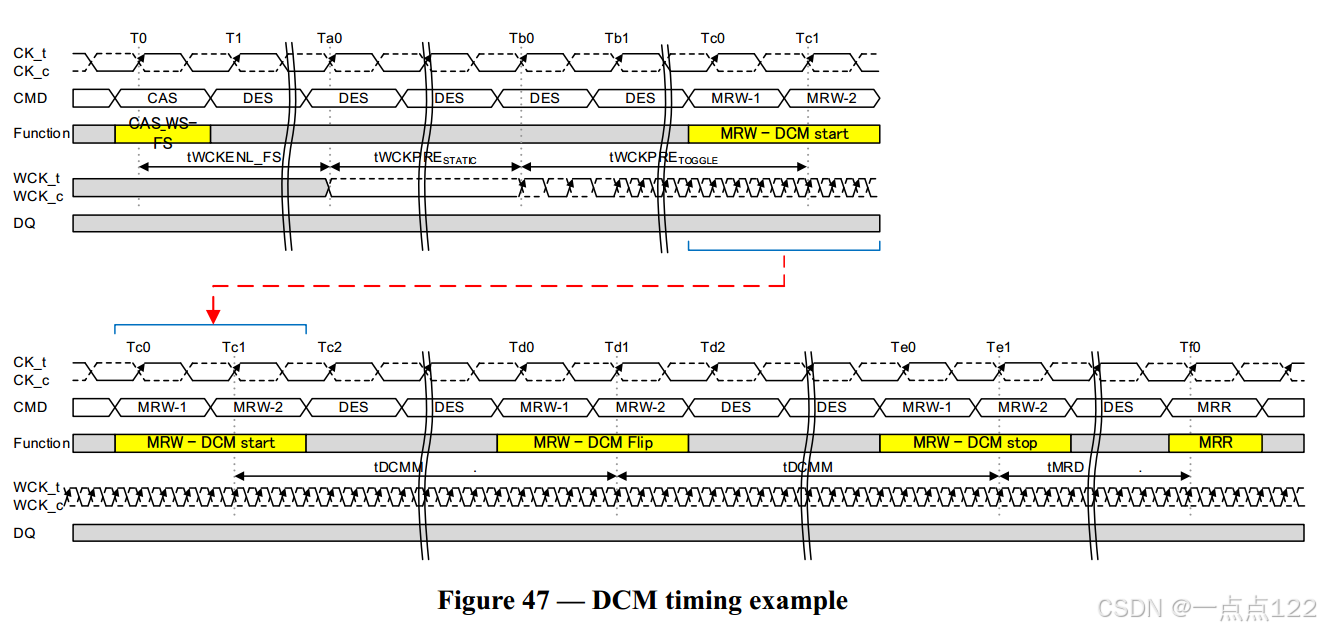

4.2.8.2 DCM序列

DCM 培训预计在 CBT 和 WCK2CK Leveling 之后进行,以确保 MRW 和 MRR 操作能够可靠地执行。下面是检查 WCK 路径占空比的 DCM 序列:

1. 更新 FSP 设置。

2. 发出 WS_FS=1 的 CAS 命令以在 DCM 启动之前以全速率切换 WCK。

3. 发出 MRW-1 和 MRW-2 以启动 DCM。

4. 等待 tDCMM,让 DCM 完成占空比测量。

5. 发出 MRW-1 和 MRW-2 来切换 MR26 OP[1] 以翻转 DCM 的输入。

5.1.将翻转位从逻辑低电平转换为逻辑高电平将自动:

5.1.1.捕获当前DCM 结果

5.1.2. 将DCM结果存入MR26 OP[2]/MR26 OP[4]

5.1.3.复位并重启DCM

5.2.将翻转位从逻辑高电平转换为逻辑低电平将自动:

5.2.1.捕获当前DCM 结果

5.2.2. 将DCM结果存入MR26 OP[3]/MR26 OP[5]

5.2.3.复位并重启DCM

6. 等待 tDCMM,让 DCM 完成翻转输入的占空比测量

7. 通过向 LPDDR5 SDRAM 设备发出 MRW-1 和 MRW-2 来退出 DCM。

7.1. 当 MR26 OP[1] 为逻辑低电平时,这会自动捕获当前 DCM 结果并将其存储在MR26 OP[2]/MR26 OP[4] 中。

7.2. 当 MR26 OP[1] 为逻辑高电平时,这会自动捕获当前 DCM 结果并将其存储在MR26 OP[3]/MR26 OP[5] 中。

8. MR26 OP[5:2] 可以通过使用正常 MRR 时序在 Tf0 之后发出 MRR 来读出。

此外,在通过 MRW 命令设置 MR26 OP[0]=0B 后的 MR26 OP[0]=1B和 tMRD 期间, Read、 RDC、MRR 和 RFF 命令被禁止。

表 35解释了 MR26 OP[1] 和 DQ 的关系。 MR26 OP[1] 不影响 MR26 OP[5:2] 输出极性。

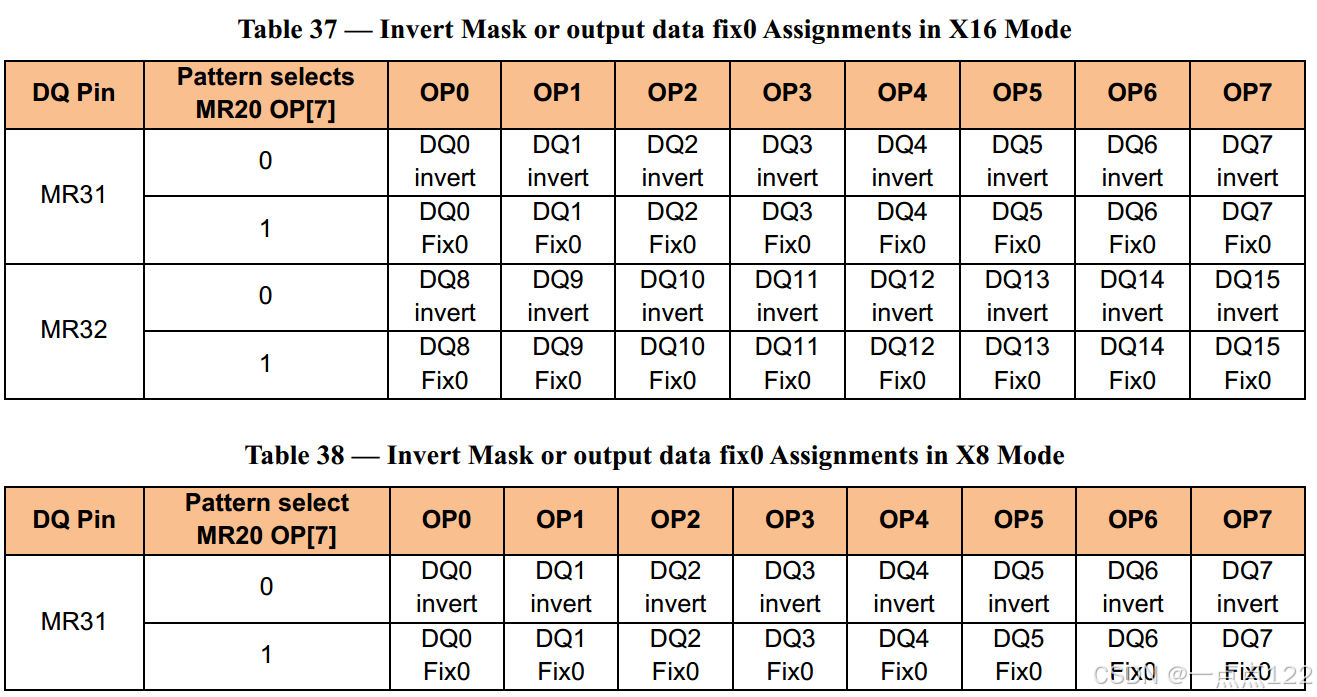

4.2.9 读取 DQ 校准

LPDDR5 SDRAM 器件具有 READ DQ 校准训练功能,可在 DQ 引脚上输出 16 位用户定义的模式。READ DQ 校准通过发出 READ DQ CALIBRATION (RDC) 命令启动,这会导致 LPDDR5 SDRAM 在DQ[15:0] 和 DMI[1:0] 上分别驱动 MR33 的内容和 MR34 的内容。根据用户定义的反转掩码或写入 MR31 和 MR32 的输出数据 fix0,模式可以在选定的 DQ 引脚上反转或固定为低电平。倒置或低位固定的选择是根据 MR20 决定的。

4.2.9.1 阅读 DQ 校准培训程序

执行 READ DQ 校准的过程是:

• 发出 MRW 命令以写入 MR33(前八位)、 MR34(后八位)、 MR20(选择反转或输出fix0)、 MR31/32(字节 0/1 的八位反转掩码或输出数据 fix0)。

- 可以选择跳过此步骤以使用默认模式。

- MR31 默认 = 55H

- MR32 默认 = 55H

- MR33 默认 = 5AH

- MR34 默认 = 3CH

• RD DQ 校准通过在处于 WCK2CK SYNC 状态时发出读取 DQ 校准 (RDC) 命令来启动。

- 每次 LPDDR5 SDRAM 收到 RDC 命令时,一个 16 位数据突发将在当前设置的 RL之后驱动 MR33 中编程的八位,然后是所有 I/O 引脚上 MR34 中编程的八位。只要保持 WCK2CK 同步状 态,就不需要 CAS 命令(WS_RD = 1)。

- 当 MR20 OP[7] = 0B 时, I/O 引脚的数据模式将被反转,并在相应的反转屏蔽模式寄存器位中编程为“1”。

- 当 MR20 OP[7] = 1B 时, IO 引脚的数据模式将固定为低电平,并在相应的输出数据固定 0 模式寄存器位中编程为“1”(参见表 37和表 38).当 MR20 OP[6]= 1B 时, DMI 模式将固定为低电 平。

- 请注意,模式是在 DMI 引脚上驱动的,但没有启用数据总线反转功能,即使在 SDRAM 模式寄存器中启用了读取 DBI 也是如此。

- RDC 命令可以每隔 2nCK @ CKR=1:4/ 4nCK @ CKR=1:2 无缝地发出,并且 Array Read 命令和 RDC 命令之间需要 tRTRRD 延迟,以及 RDC 命令和阵列读取之间需要的延迟.

- 使用 CAS 命令接收的操作数必须驱动为低电平, WS_RD 除外。

- 先前 CAS 操作数设置的功能将被忽略。 (忽略 DC0~3 和 B3。)

• DQ 读取训练可以在任何 bank 处于活动状态或没有 bank 处于活动状态、刷新期间或 SREF 期间执行,无需掉电。

• 在字节模式下, MR31 只对低字节选择的设备有效, MR32 只对高字节选择的设备有效。

4.2.9.1 阅读 DQ 校准培训程序(续)

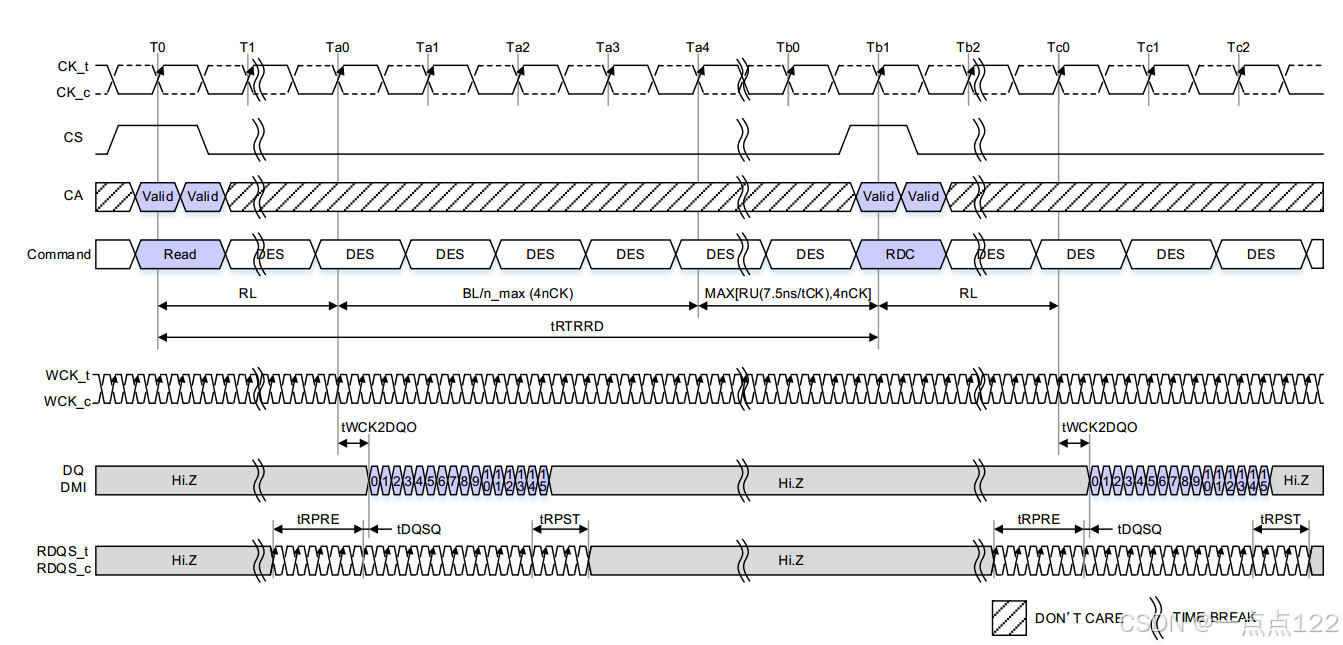

注 1 tWCK2CK 在此实例中为 0ps。

注 2 WCK 始终开启模式。

注 3 读取到读取 DQ 校准操作显示为命令到命令时序的示例。从读取到读取 DQ 校准的时间为 tRTRRD。

注 4 读取 DQ 校准使用与读取命令相同的命令到数据时序关系。

注 5 如果 WCK2CK 同步关闭状态,则需要在发出读取 DQ 校准命令之前发出 CAS(WS_RD) 或 CAS(WS_FS) 命令。这意味着必须在发出读取 DQ 校准命令之前执行 WCK2CK 同步操作。读取DQ 校准使用与 WCK2CK 同步操作相同的时序关系作为读取命令。

注 6 DES 命令的显示是为了便于说明;此时其他命令可能有效。

图 48 — 读取到读取 DQ 校准时序: BG 模式, CKR=4:1, BL=16, tRPST=2.5nWCK

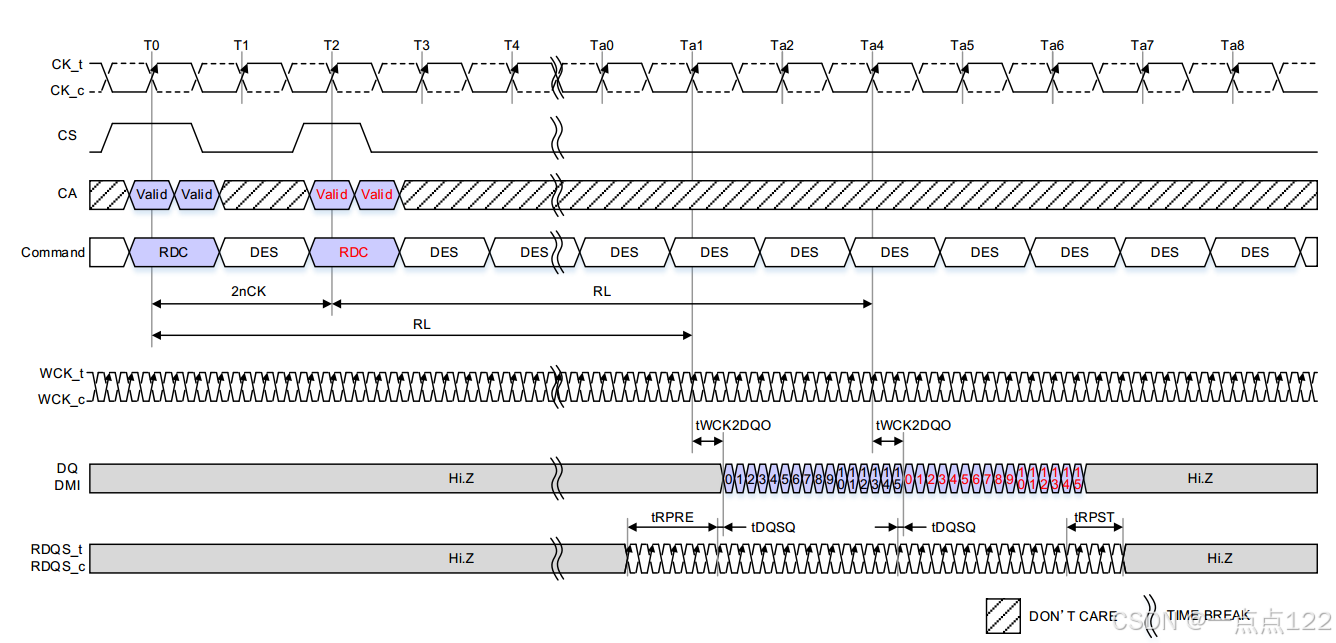

注 1 tWCK2CK 在此实例中为 0ps。

注 2 WCK 始终开启模式。

注 3 读取 DQ 校准到读取 DQ 校准操作显示为命令到命令时序的示例。无缝读取 DQ 校准命令可以通过在定义的训练相关时序约束表的每个周期重复该命令来执行。

注 4 读取 DQ 校准使用与读取命令相同的命令到数据时序关系。

注 5 如果 WCK2CK 同步关闭状态,则需要在发出读取 DQ 校准命令之前发出 CAS(WS_RD) 或 CAS(WS_FS) 命令。这意味着必须在发出读取 DQ 校准命令之前执行 WCK2CK 同步操作。读取DQ 校准使用与 WCK2CK 同步操作相同的时序关系作为读取命令。

注 6 DES 命令的显示是为了便于说明;此时其他命令可能有效。

图 49 — 读取 DQ 校准以读取 DQ 校准时序: BG 模式, CKR=4:1, BL=16, tRPST=2.5nWCK

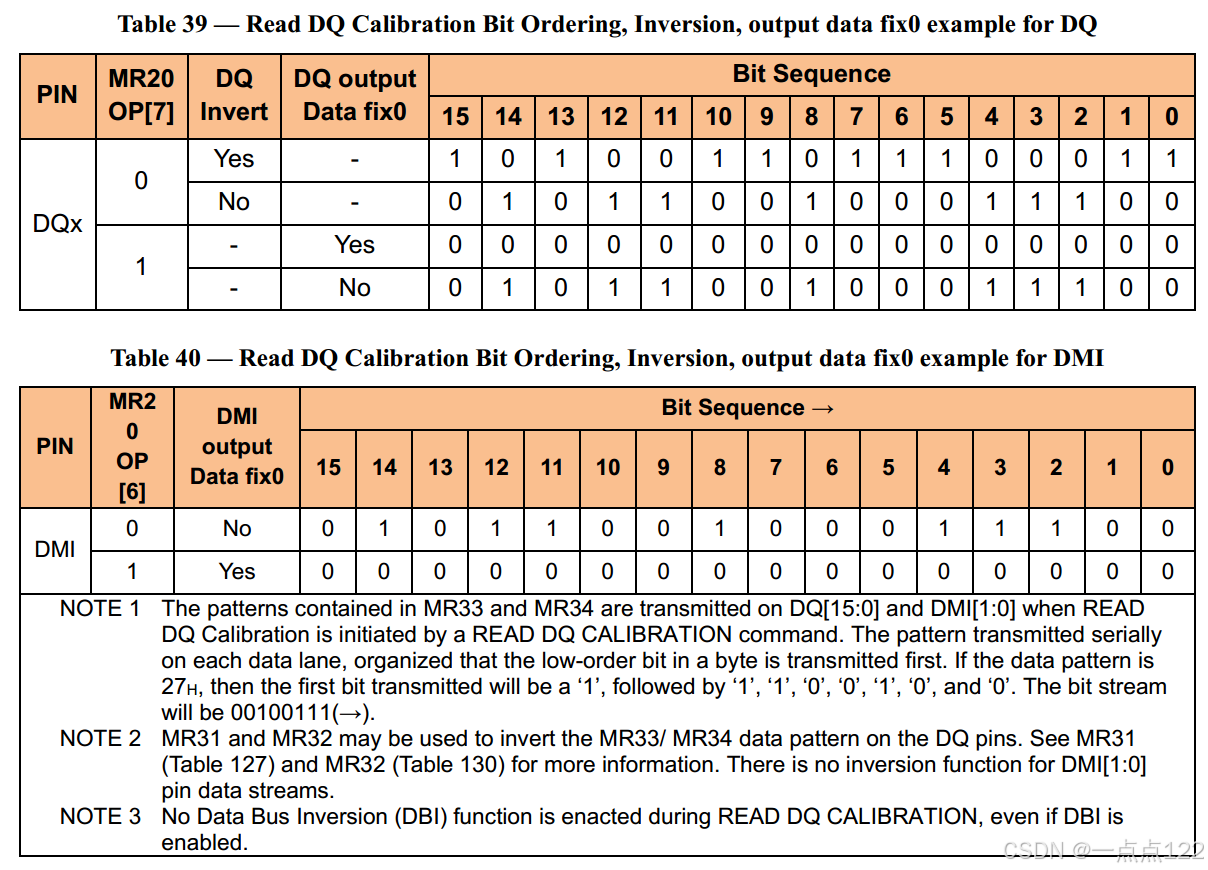

4.2.9.2 阅读 DQ 校准示例

READ DQ 校准训练输出的示例显示在表 39和表 40。 这显示了在执行一个 READ DQ CALIBRATION命令时将在每个 DQ 上驱动的 16 位数据模式。此输出假定使用以下模式寄存器值。

- MR31 默认 = 55H

- MR32 默认 = 55H

- MR33 默认 = 1CH

- MR34 默认 = 59H

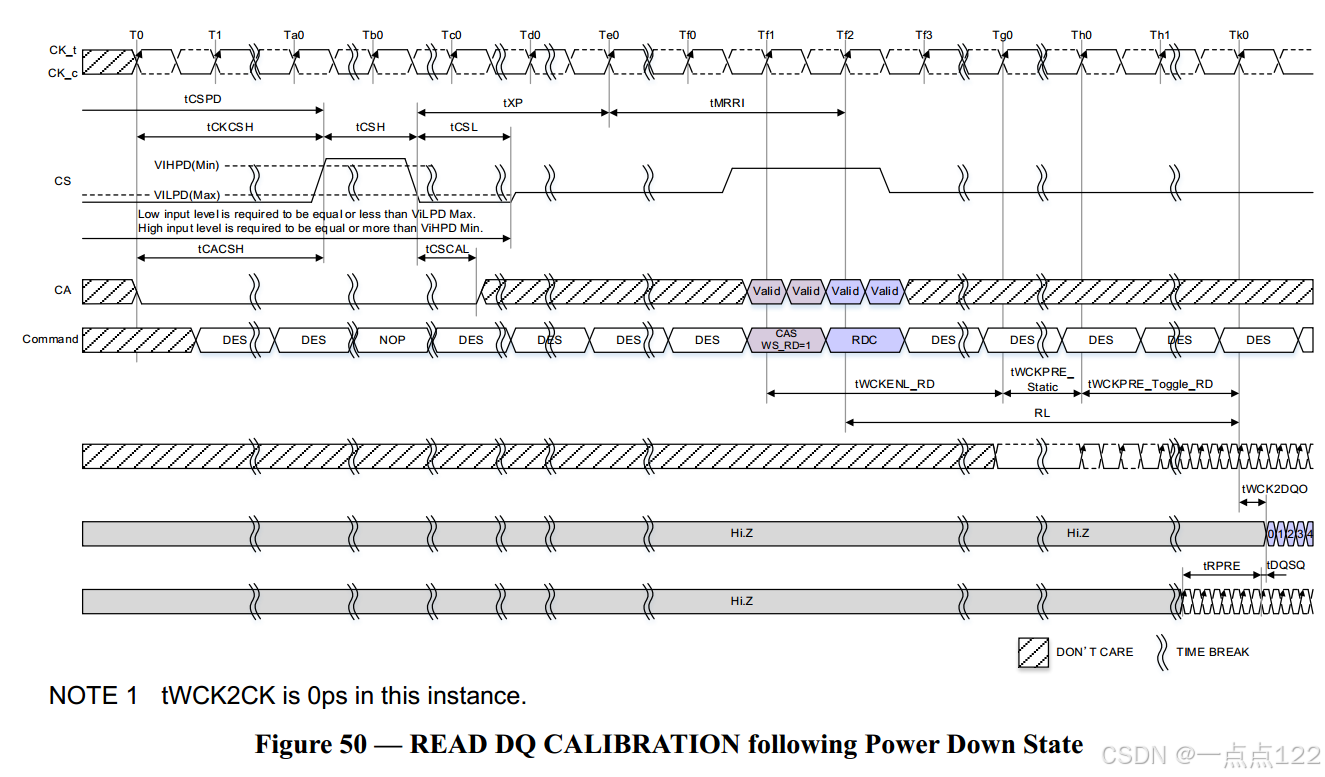

4.2.9.3 READ DQ Calibration after Power Down 退出

在掉电状态之后,在发出 READ DQ CALIBRATION 命令之前需要额外的时间 tMRRI。需要这个额外的时间是为了能够在退出待机、掉电模式后允许更多的上电时间用于 MR33 和 MR34 数据路径中的读取 DQ 数据,从而最大限度地节省掉电电流。

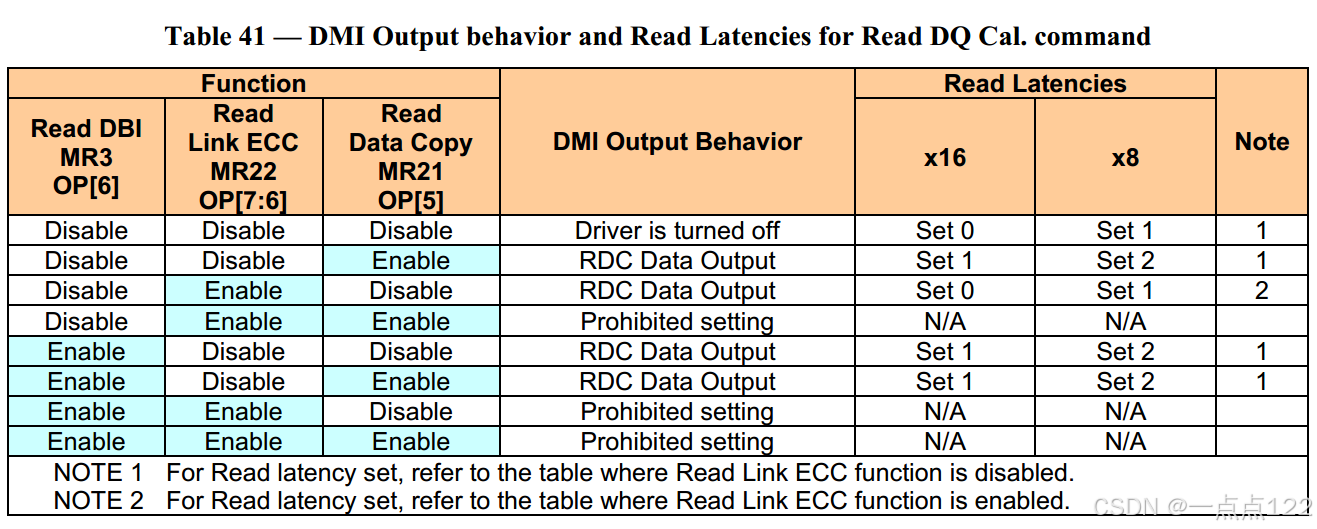

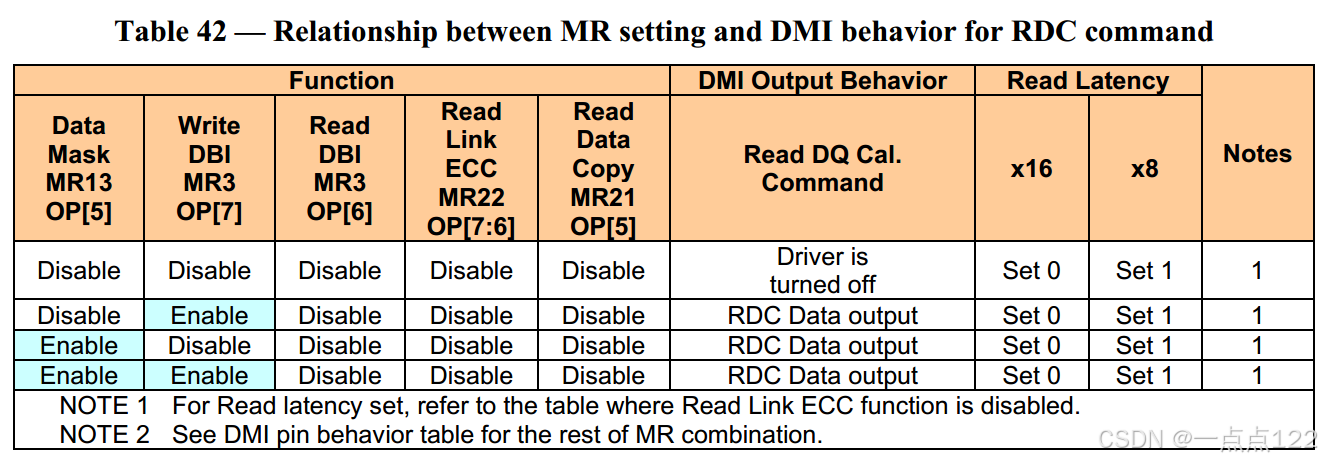

4.2.9.4 RDC 的 DMI 行为控制

LPDDR5 SDRAM 支持读取 DQ 校准命令时的 DMI 输出行为控制作为可选功能。 MR0 OP[4]表示是否支持DMI输出行为控制。如果MR0 OP[4]=1B, DMI输入/输出行为控制模式可以选择MR13 OP[4]。

- MR0 OP[4]=0B仅支持模式 1。

- MR0 OP[4]=1B可选择模式 1 和模式 2。

模式 1 和模式 2 的概述。

- 模式 1: MR13 OP[4]=0B DMI 输出行为遵循 MR 设置读取 DBI、读取链路 ECC 和读取数据复制。

- 模式 2: MR13 OP[4]=1B 如果在启用数据掩码和/或写入 DBI 时发出读取 FIFO 命令和读取 DQ 校准命令,即使禁用读取 DBI、读取链路 ECC 和读取数据复制, DMI 也会输出有效数据。

4.2.9.4.1.1 DMI 输出行为模式 1

4.2.9.4.1.2 DMI Output Behavior Mode 2

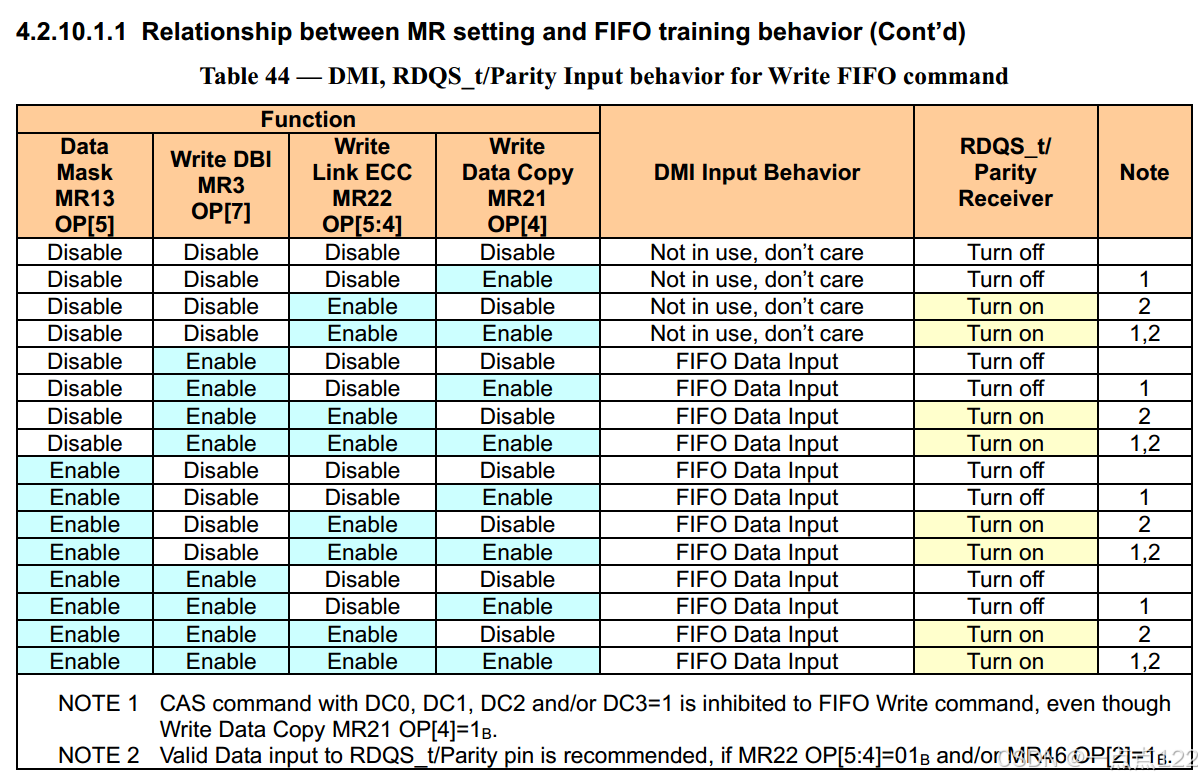

4.2.10 WCK-DQ training

LPDDR5 SDRAM 使用无与伦比的 WCK-DQ 路径来实现高速性能并节省 SDRAM 中的功率。因此,需要训练 WCK 以到达与数据眼中心对齐的 DQ 锁存器。 SDRAM DQ 接收器位于 DQ 焊盘处,并且在 SDRAM 中具有比 WCK 信号更短的内部延迟。当 WCK 到达锁存器时, SDRAM DQ 接收器将锁存DQ 总线上存在的数据,并且通过相对于 WCK 延迟 DQ 信号来完成训练,以便数据眼图到达以WCK 转换为中心的接收器锁存器。

LPDDR5 SDRAM 使用用户特定模式提供基于命令的 FIFO 写/读训练操作。基本上, DMI 将被视为与 DQ 相同。这意味着写入数据通过 WFF 命令发送到 DMI 的 FIFO,这些数据可以通过 RFF 命令从 DMI 的 FIFO 中读出。另一方面,在某些情况下, DMI 行为与 DQ 不同。请参阅本节后面将描述的有关特殊 DMI 行为的详细信息。

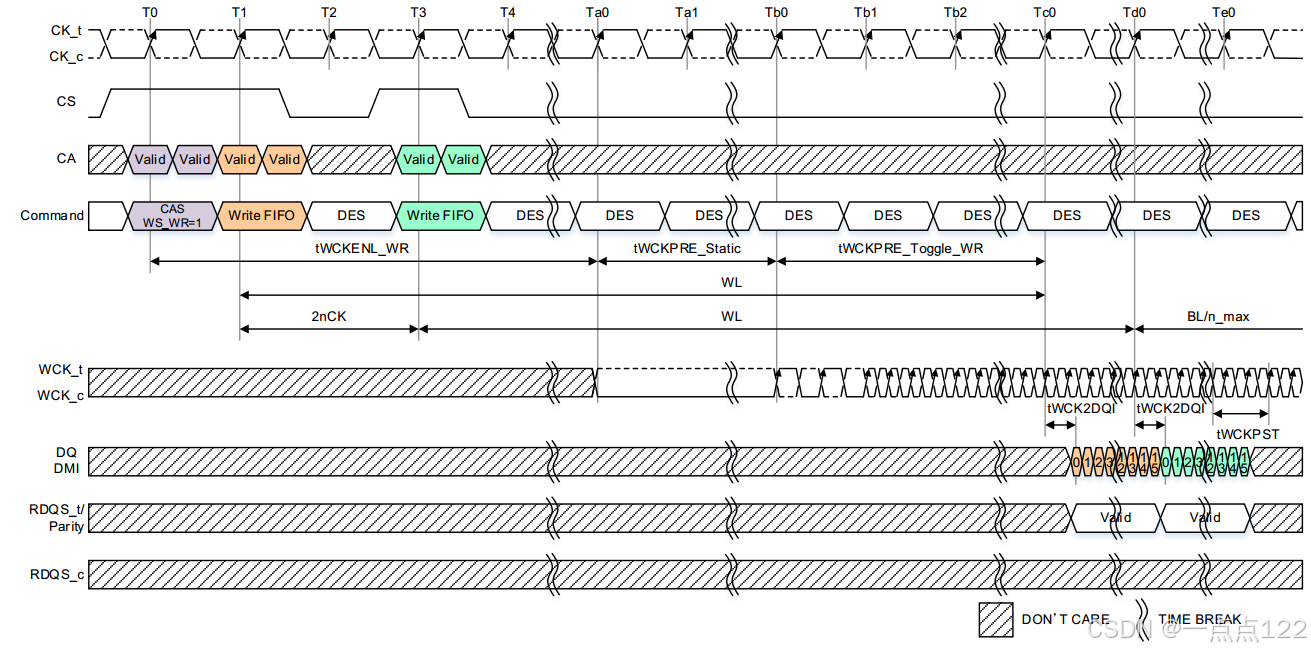

4.2.10.1 训练程序

要执行写入训练,需要向控制器发出 WS_WR=1 的 CAS 命令,然后立即发出写入 FIFO 命令以将数据写入 FIFO。 CAS 和 Write FIFO 命令的时序与 CAS 和 Write 命令相同。最多可向 SDRAM

发出 8 个具有用户定义模式的连续写入 FIFO 命令,以在每个引脚上存储最多 128 个值 (BL16 x 8),这些值可通过读取 FIFO 命令回读。

Write FIFO 和 Read FIFO 命令的突发长度限制为 BL16,而不管 Bank 架构: BG、 16B 和8B 模式。

写入/读取 FIFO 指针操作将在本节后面介绍。

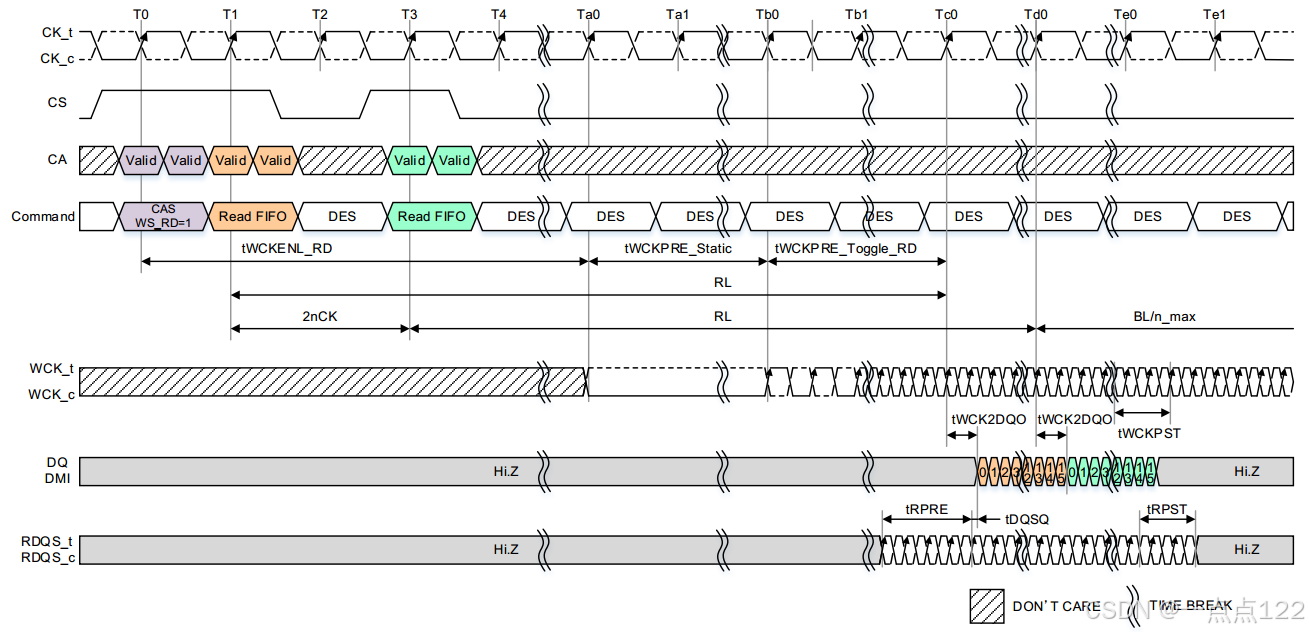

使用 Write FIFO 命令将数据写入 SDRAM 后,可以使用 Read FIFO 命令读回数据,并将结果与“预期”数据进行比较,以查看是否需要进一步训练。要回读数据, 控制器需要发出 WS_RD=1 的CAS 命令,然后立即发出读取 FIFO 命令以从 FIFO 回读数据。 CAS 和读取 FIFO 命令的时序与CAS 和读取命令相同。Read FIFO 操作不会破坏 FIFO 中捕获的数据,因此可以连续读取数据,直到它被 Write FIFO命令覆盖。例如:如果依次执行 8 个 Write FIFO 命令,那么一系列 Read FIFO 命令将从FIFO[0]、 FIFO[1]….FIFO[7] 中读取有效数据,然后返回到 FIFO[0]在下一个读取 FIFO 上。如果执行的 Write FIFO 命令少于 8 个,则未写入的寄存器在回读时将具有未定义(但有效)的数据。例如,如果顺序执行的 Write FIFO 命令少于 8 个(示例 = 3),那么一系列 ReadFIFO 命令将为 FIFO[0]、 FIFO[1] 和 FIFO[2] 返回有效数据,但是下一个(8-3) 读取 FIFO 命令将通过 FIFO[7] 返回 FIFO[3] 的未定义数据,然后返回到 FIFO[0] 中的有效数据。

在 WCK-DQ 训练期间,只允许使用以下命令以防止写入和读取 FIFO 被覆盖并简化此训练过程。

CAS_WR, CAS_RD, CAS_FS and CAS_OFF

Read FIFO

Write FIFO

DES

NOP

Refresh (All bank and Per bank)

Mode Register Write for FSP-WR: MR16 OP[1:0], FSP-OP: MR16 OP[3:2], VRCG: MR16 OP[6], VREF(DQ[7:0]): MR14 OP[6:0] and VREF(DQ[15:8]): MR15 OP[6:0]

WCK-DQ 训练可以在空闲、 Bank 活动、 SDRAM 刷新或自刷新期间启动。当 FIFO 指针在 Write 和Read FIFO 之间的值相同时,可以结束 WCK-DQ 训练。

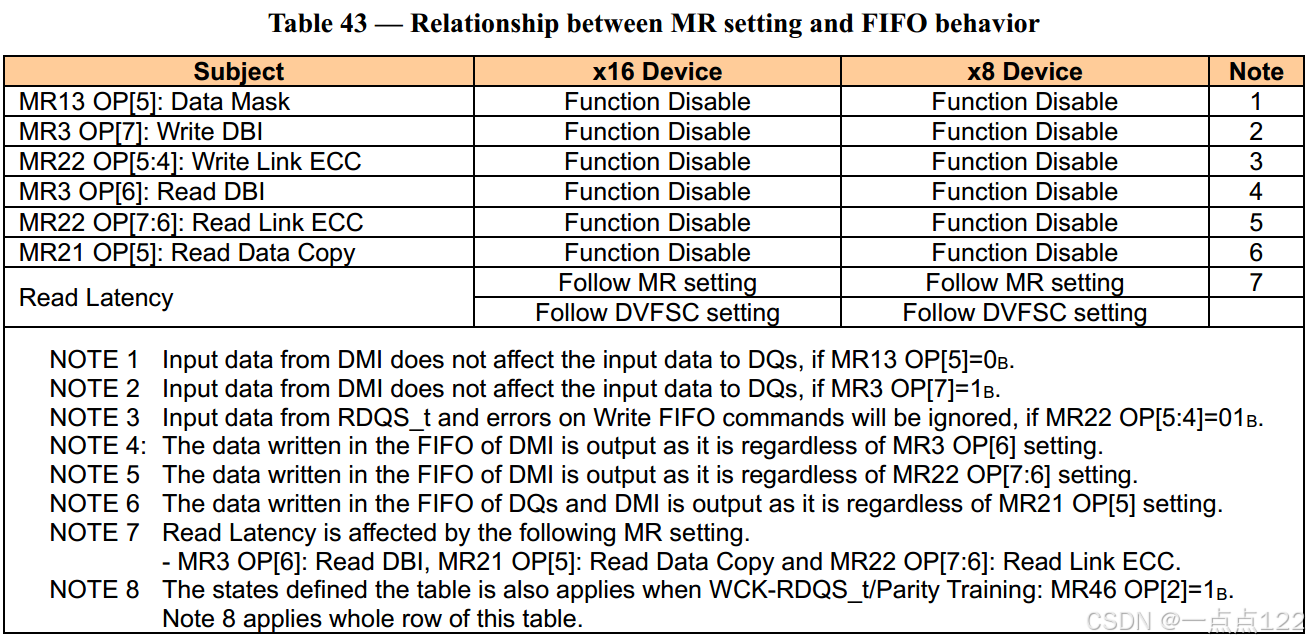

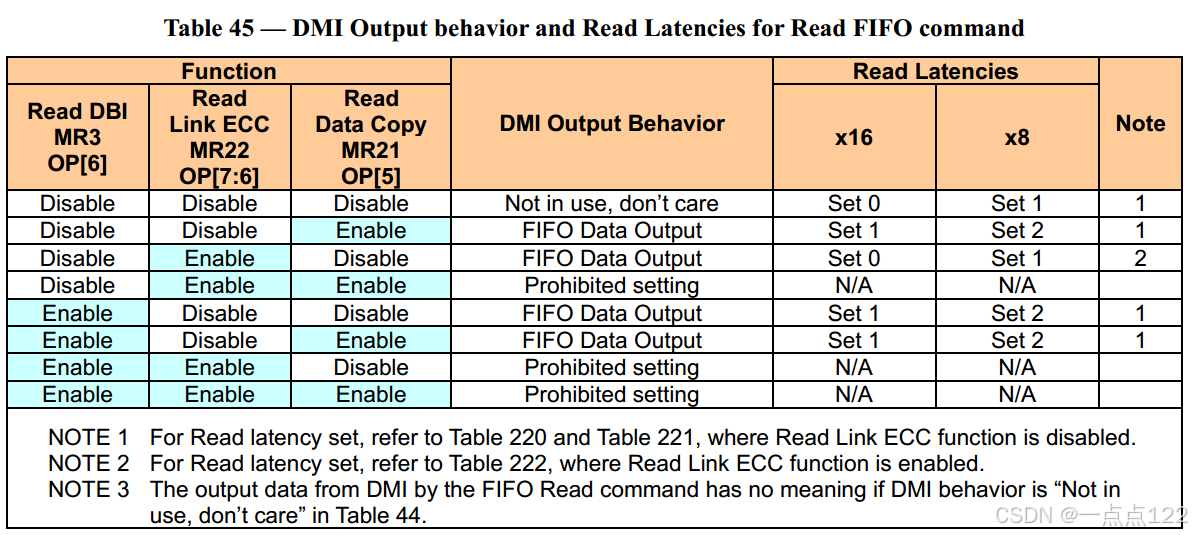

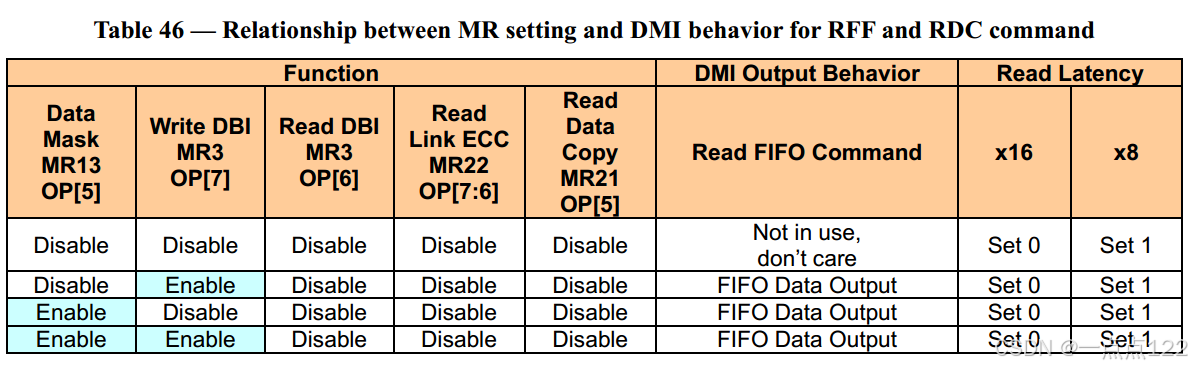

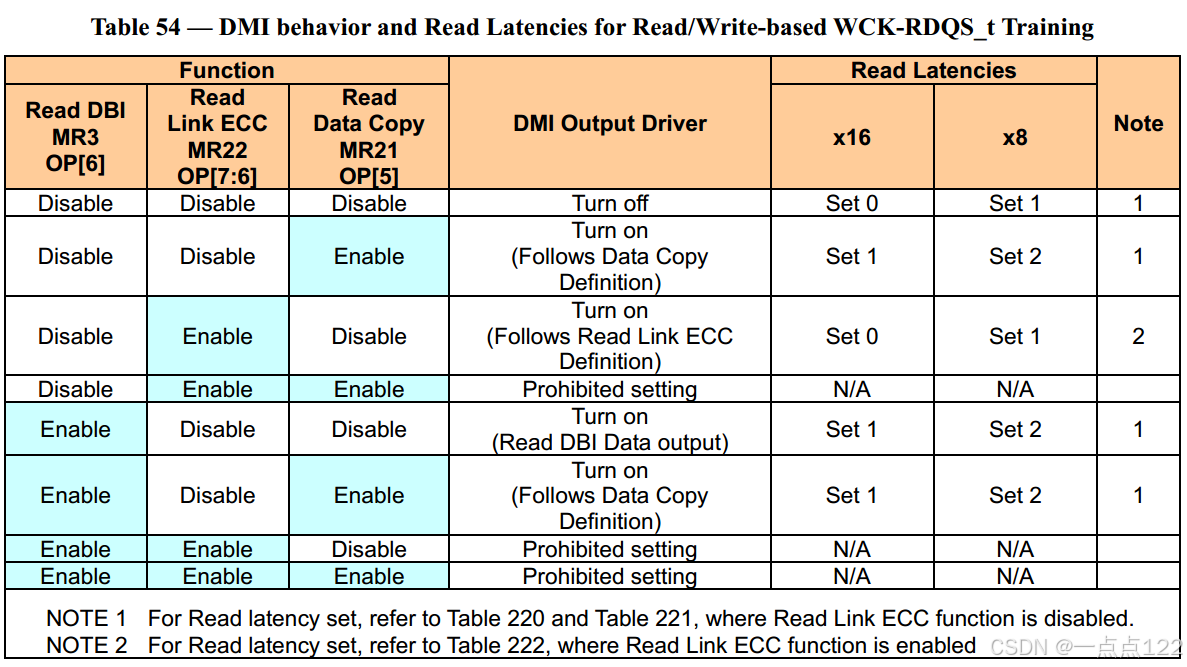

4.2.10.1.1 MR设置与FIFO训练行为的关系

无论以下 MR 设置如何,都可以发出写入 FIFO 和读取 FIFO 命令。

MR13 OP[5]:

数据掩码

MR3 OP[7]:写入 DBI

MR22 OP[5:4]:写入链路 ECC

MR3 OP[6]:读取 DBI

MR22 OP[7:6]:读取链路 ECC

MR21 OP[5]:读取数据拷贝

但是,上述 MR 设置会影响读取延迟和/或 DMI 引脚行为。参考桌子43 详细信息。

LPDDR5 SDRAM 支持读取 FIFO 命令和读取 DQ 校准命令的 DMI 输出行为控制作为可选功能。MR0 OP[4]表示是否支持DMI输出行为控制。如果MR0 OP[4]=1B, DMI输入/输出行为控制模式可以选择MR13 OP[4]。

MR0 OP[4]=0B 仅支持模式 1。

MR0 OP[4]=1B 可选择模式 1 和模式 2。

Mode 1和Mode 2的概要 Mode1:

mode1:MR13 OP[4]=0B DMI 输出行为遵循 MR 设置读取 DBI、读取链路 ECC 和读取数据复制。

mode2:MR13 OP[4]=1B 如果在启用数据掩码和/或写入 DBI 时发出读取 FIFO 命令和读取 DQ 校准命令,即使禁用读取 DBI、读取链路 ECC 和读取数据复制, DMI 也会输出有效数据。

4.2.10.1.1.1 DMI 输出行为模式 1

4.2.10.1.1.2 DMI 输出行为模式 2

4.2.10.2 WCK-RDQS_t/对偶训练

启用 Link ECC 后, RDQS_t 引脚将具有两种不同的功能。

因此,在定义的正常 WCK-DQ 训练过程中, RDQS_t 引脚不能用作数据输出引脚4.2.10.1.

为了训练 RDQS_t 引脚,读取和写入 FIFO 命令与 MR46 OP[2] 设置为“1”一起使用。设置此位后, Write FIFO 命令将允许通过 RDQS_t 引脚写入数据。通过 RDQS_t 引脚写入的数据随后可以通过 DMI 通过读取 FIFO 命令读回。在将 1B 设置为 MR46 OP[2] 之前,需要进行以下 MR设置: WCK-RDQS_t/Parity Training Enabled。

- 在读取操作期间, RDQS_t 将用作 RDQS_t。

- 在写操作期间, RDQS_t 将用作奇偶校验。

- 写入链路 ECC: MR22 OP[5:4]=01B

- 读取链路 ECC: MR22 OP[7:6]=01B

- CAS_WR、 CAS_RD、 CAS_FS 和 CAS_OFF

- Read FIFO

- Write FIFO

- DES

- Nop

- Refresh(all bank and pre bank)

- FSP-WR 的模式寄存器写入: MR16 OP[1:0]、 FSP-OP: MR16 OP[3:2]、 VRCG: MR16 OP[6]和 MR46 OP[2]。

一旦 MR46 OP[2] 设置为 1B,允许的命令如下。

而WCK-RDQS_t/Parity Training: MR46 OP[2]=1B只能在WCK频率1600MHz以外使用,以及Link ECC功能。

退出 WCK-RDQS_t/奇偶校验训练模式, MR46 OP[2] 必须设置为“0”。

4.2.10.3 FIFO 指针复位和同步

Read 和 Write FIFO 指针在以下条件下复位:

- 上电初始化

- RESET_n 置位

- 掉电

- 进入深度睡眠模式

- 自刷新掉电进入

Write FIFO 命令使 Write-FIFO 指针前进,而 Read FIFO 命令使 Read-FIFO 指针前进。为了保持指针对齐, SoC 内存控制器必须在 WCK-DQ 训练期结束时遵守以下限制:

- b=a+(nxc)

其中:

'a' 是写入 FIFO 命令的数量;

'b' 是读取 FIFO 命令的数量;

'c' 是 FIFO深度(对于 LPDDR5 = 8);

'n'为正整数, ≥0

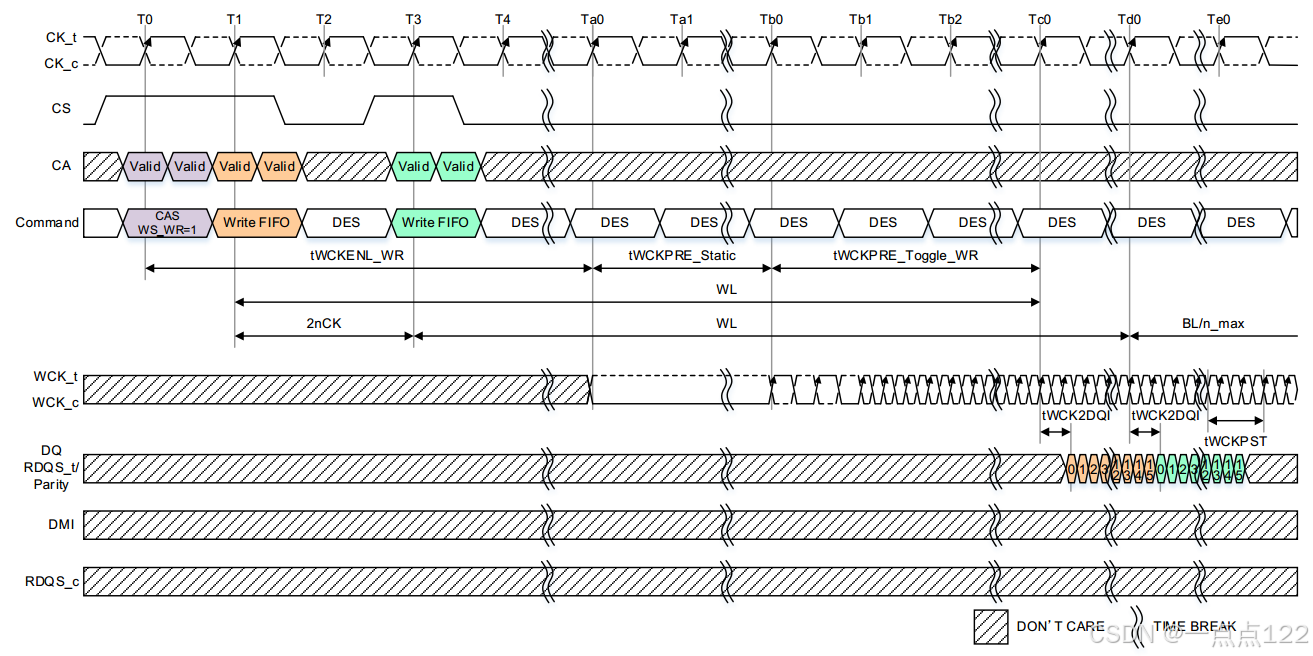

注 1 tWCK2CK 在此实例中为 0ps。

注 2 WL 的结束和 tWCKPRE_Toggle_WR 在此实例中的时序相同。

注 3 (8 +1) Write FIFO 命令将覆盖来自第一个命令的 FIFO 数据。如果执行的 Write FIFO 命令少于 8 个,则剩余的 FIFO 位置将包含未定义的数据。

注 4 当 WCK 同步到期时,在 Write FIFO 命令之前需要 CAS 命令。注 5 在 RDQS_t/Parity 和 DMI 的输入接收器由 MR 设置启用的情况下。

图 51 — BG 模式的连续写入 FIFO 操作时序: CKR(WCK 与 CK) = 4:1

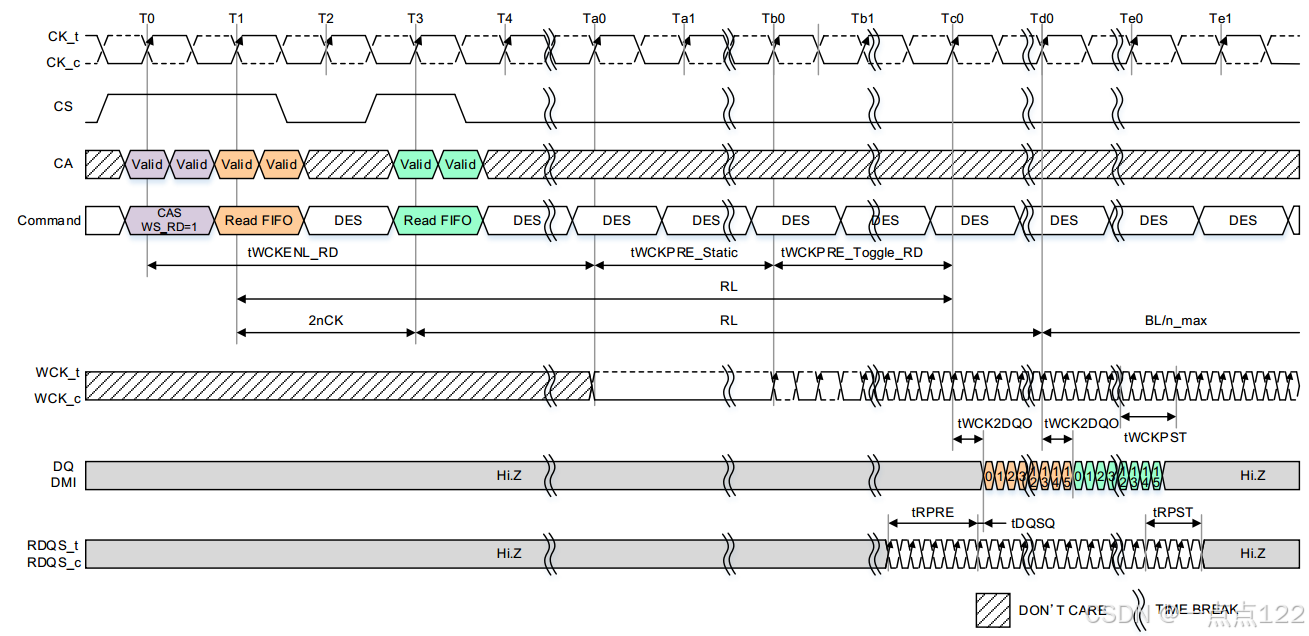

注 1 tWCK2CK 在此实例中为 0ps。

注 2 RL 的结束和 tWCKPRE_Toggle_RD 在此实例中的时序相同。

注 3 可以从 FIFO 连续读取数据而不会损坏任何数据。在 8 个读取 FIFO 命令后, FIFO 指针将返回到第一个 FIFO 并继续前进。

注 4 当 WCK 同步到期时,在读取 FIFO 命令之前需要 CAS 命令。注 5 如果通过 MR 设置启用 DMI 的输出驱动器。

图 52 — BG 模式的连续读取 FIFO 操作时序: CKR(WCK 与 CK) = 4:1

注 1 WCK-RDQS_t/奇偶校验训练已启用: MR46 OP[2] =1B 注 2 tWCK2CK在此实例中为 0ps。

注 3 WL 的结束和 tWCKPRE_Toggle_WR 在此实例中的时序相同。

注 4 (8 +1) Write FIFO 命令将覆盖来自第一个命令的 FIFO 数据。如果执行的 Write-FIFO 命令少于 8 个,则剩余的 FIFO 位置将包含未定义的数据。

注 5 当 WCK 同步到期时,在 Write FIFO 命令之前需要 CAS 命令。注 6 在 RDQS_t/Parity 和 DMI 的输入接收器通过 MR 设置启用的情况下。

图 53 — 连续写入 FIFO 操作时序: WCK-RDQS_t/Parity 为 BG 模式启用训练: CKR(WCK 与 CK) = 4:1

注 1 WCK-RDQS_t/奇偶校验训练启用: MR46 OP[2] =1B

注 2 DMI 引脚输出写入 FIFO 命令通过奇偶校验引脚写入 FIFO 的数据。注 3 tWCK2CK 在此实例中为 0ps。

注 4 在这种情况下, RL 和 tWCKPRE_Toggle_RD 的结束时间相同。

注 5 可以从 FIFO 连续读取数据而不会损坏任何数据。在 8 个读取 FIFO 命令后, FIFO 指针将返回到第一个 FIFO 并继续前进。

注 6 当 WCK 同步到期时,在读取 FIFO 命令之前需要 CAS 命令。注 7 如果通过 MR 设置启用 DMI 的输出驱动器。

图 54 — 连续读取 FIFO 操作时序: WCK-RDQS_t/Parity 为 BG 模式启用训练: CKR(WCK 与 CK) = 4:1

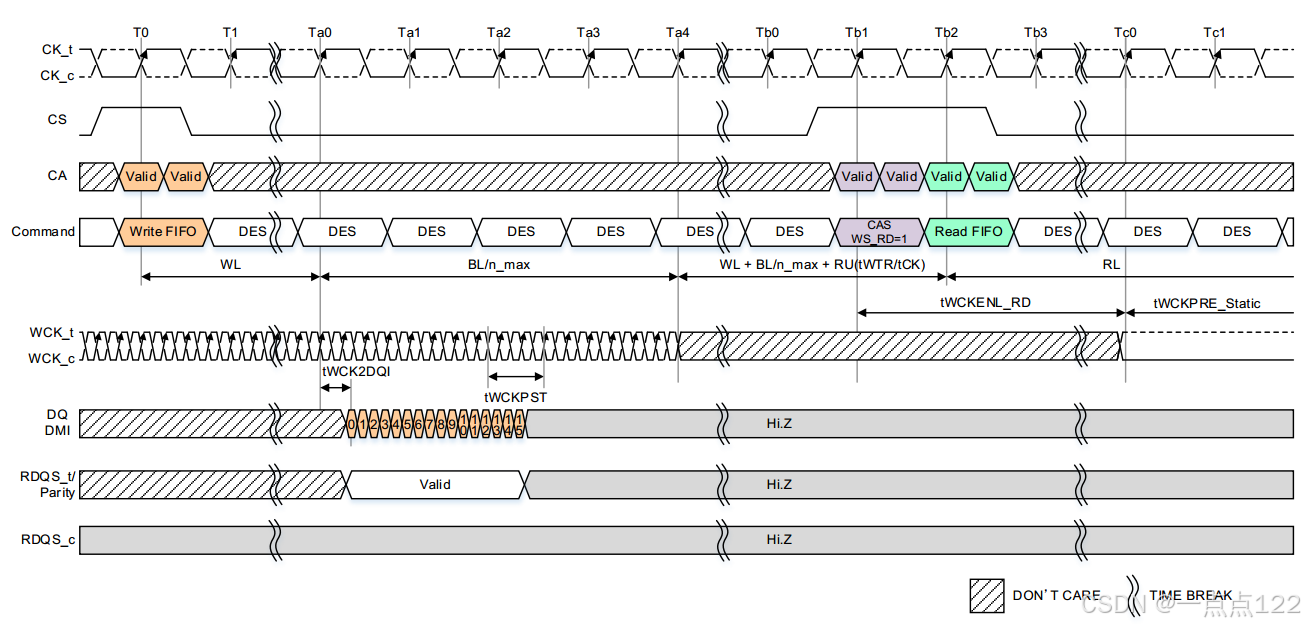

注 1 tWCK2CK 在此实例中为 0ps。

注 2 在 RDQS_t/Parity 和 DMI 的输入接收器通过 MR 设置启用的情况下。

图 55 — BG 模式的写入 FIFO 到读取 FIFO 时序: CKR(WCK 与 CK) = 4:1

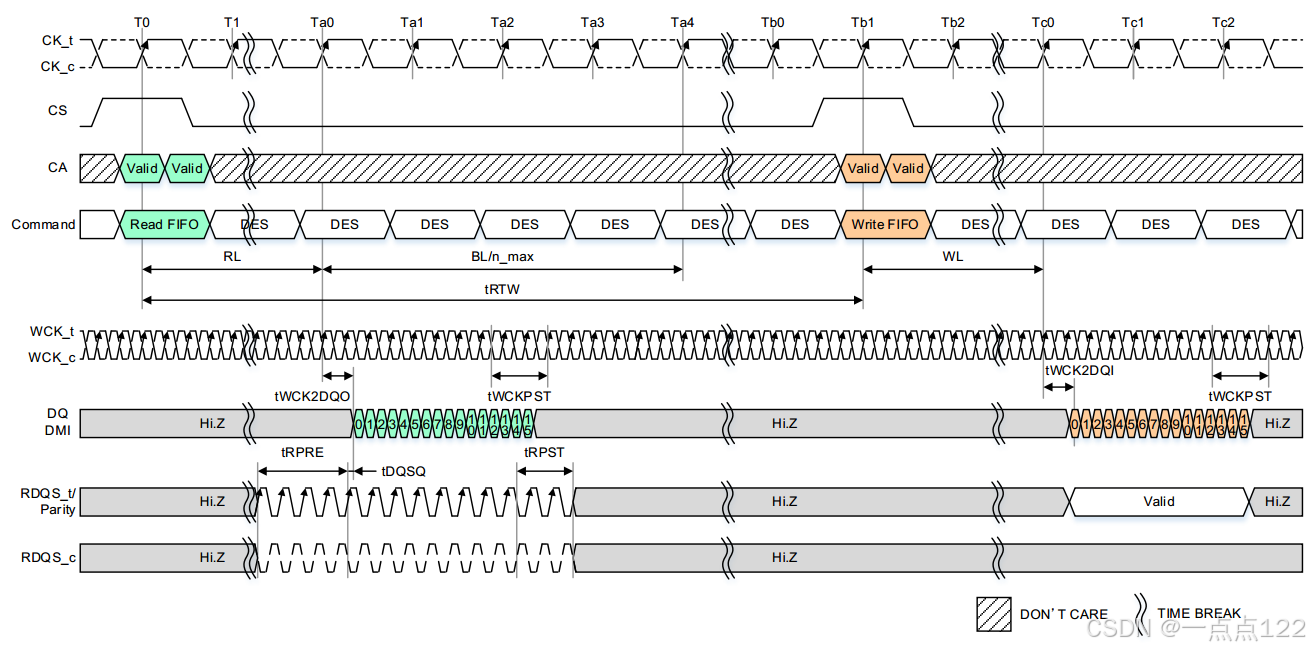

注 1 tWCK2CK 在此实例中为 0ps。

注 2 如果通过 MR 设置启用 DMI 的输出驱动器。

注 3 在 RDQS_t/Parity 和 DMI 的输入接收器通过 MR 设置启用的情况下。

图 56 — BG 模式的读 FIFO 到写 FIFO 时序: CKR(WCK 与 CK) = 4:1

4.2.11 RDQS 切换模式

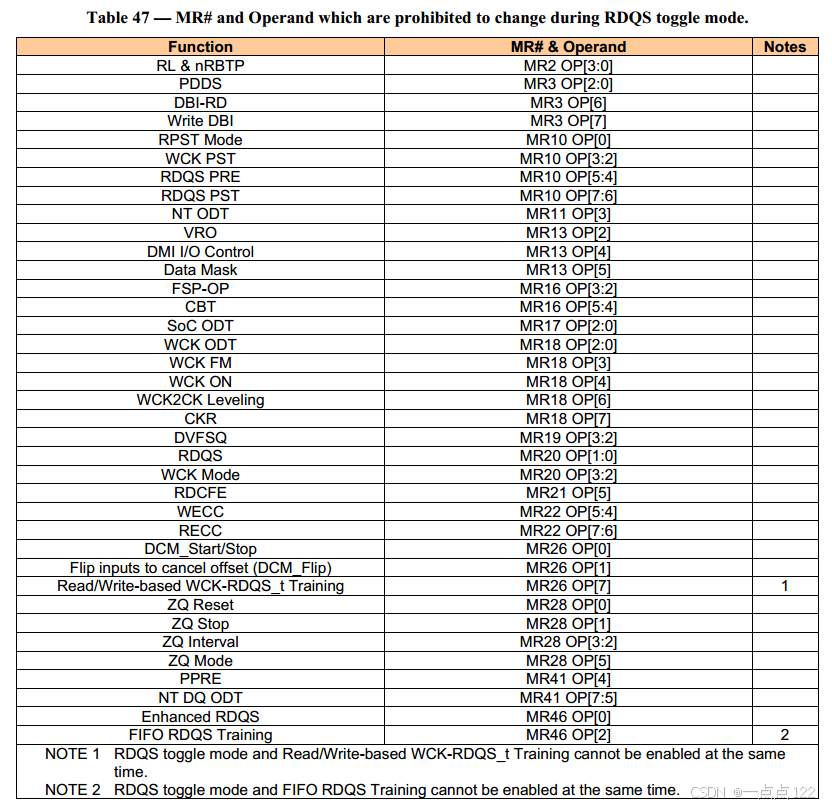

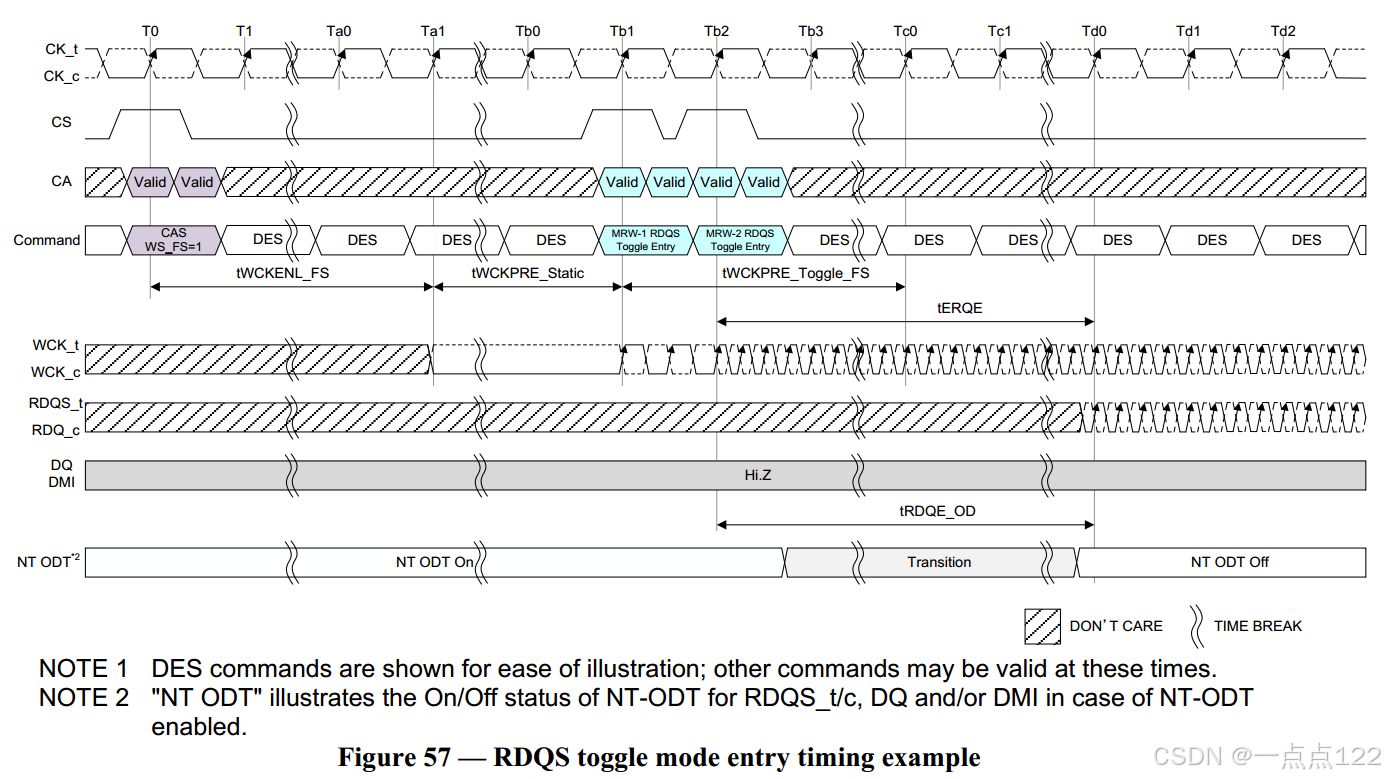

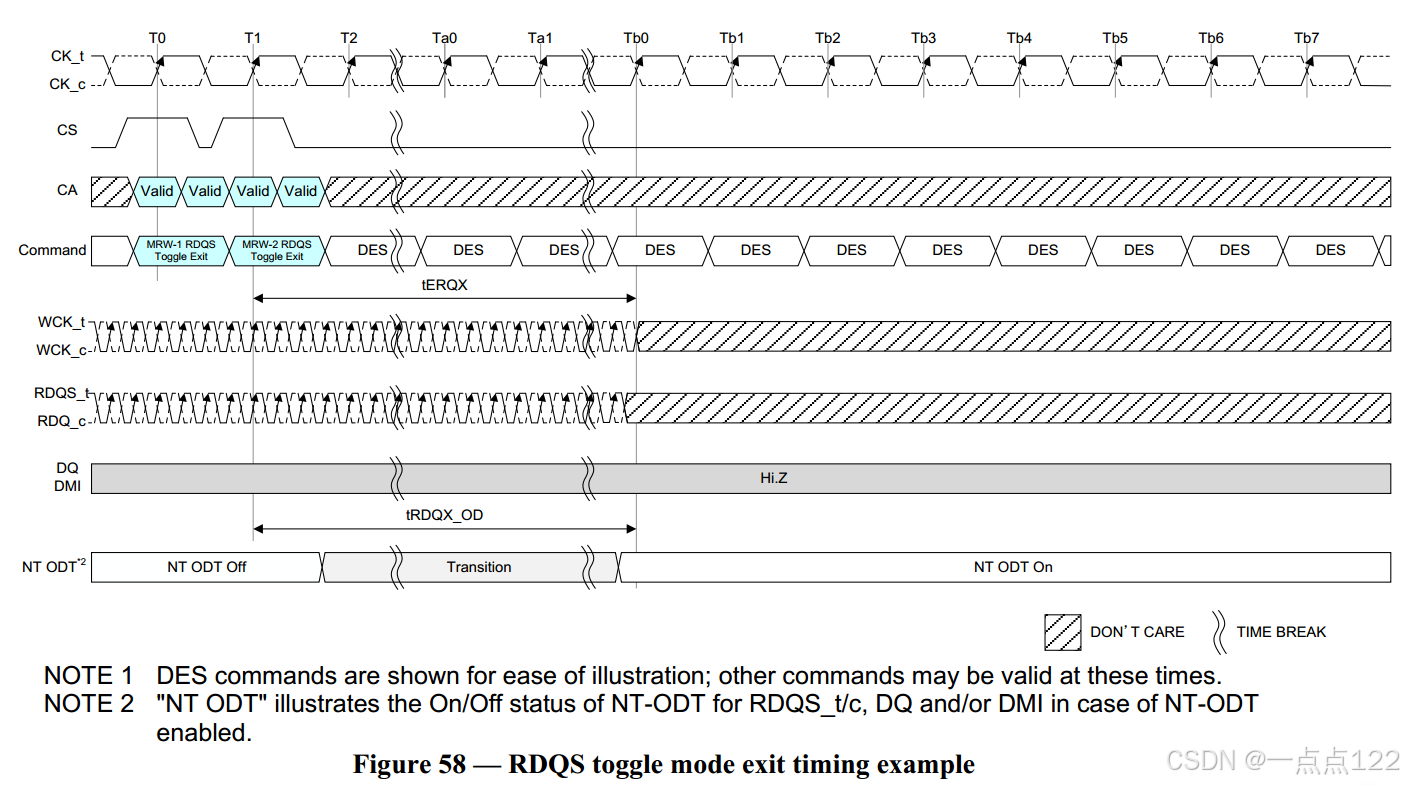

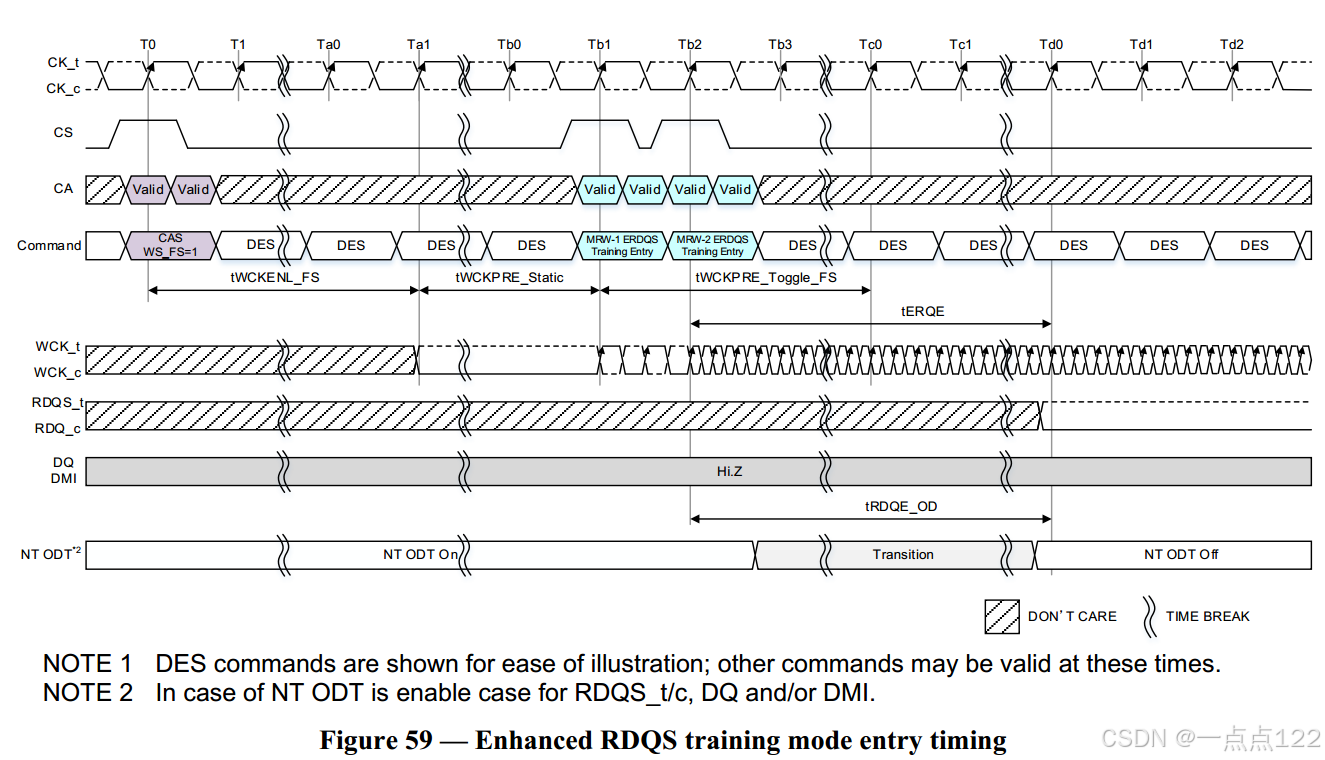

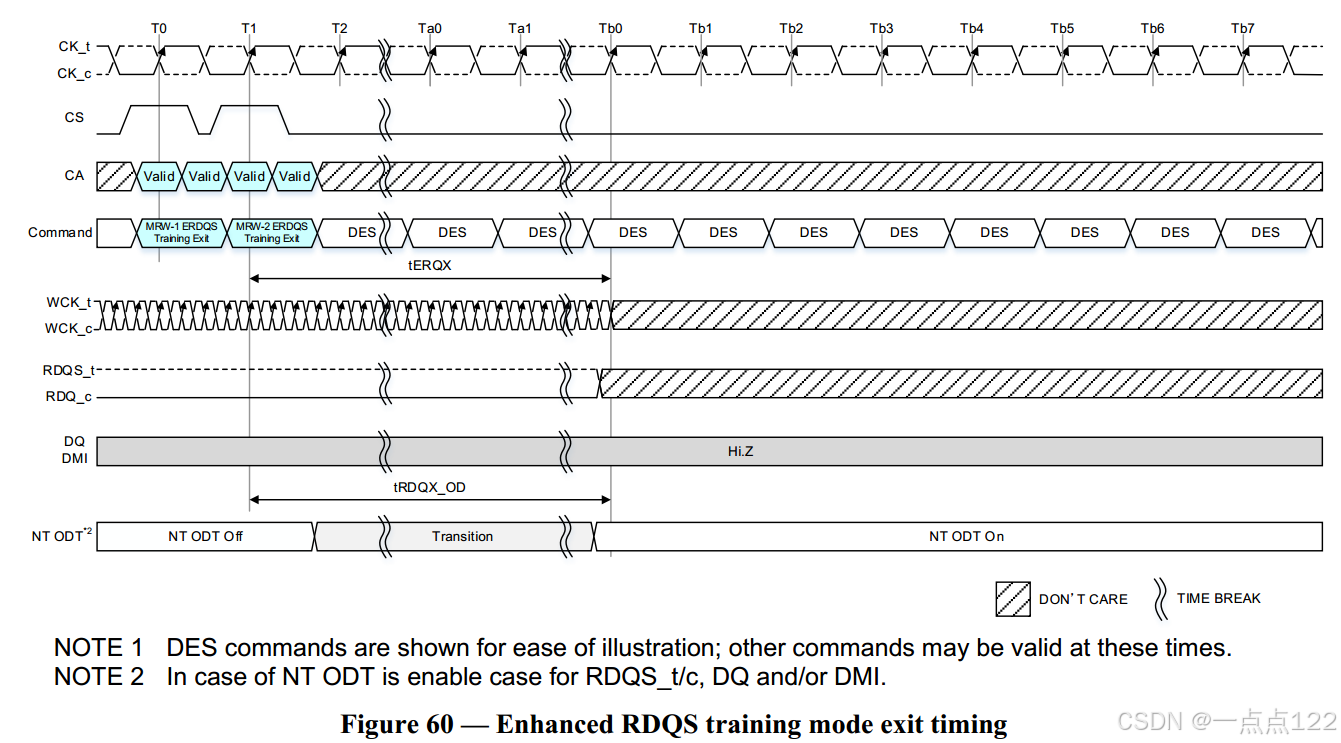

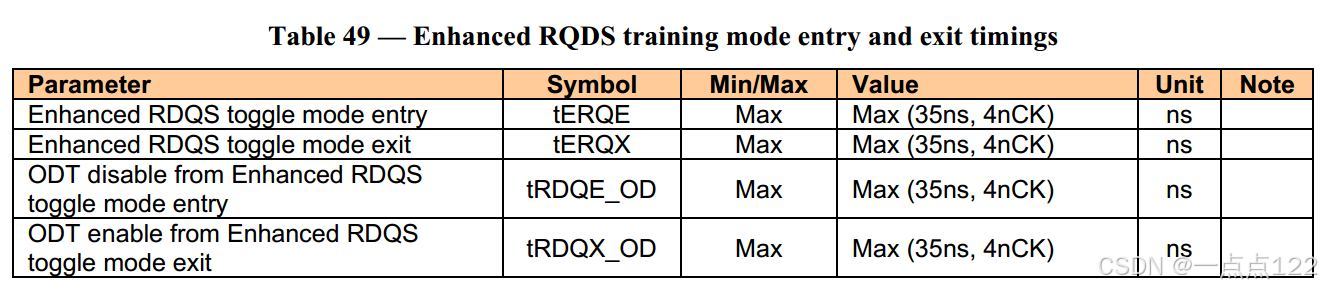

LPDDR5 SDRAM 具有 RDQS 切换模式,可在 RDQS 引脚上输出连续切换模式。在发出 MRW 命令之前,需要一个 CAS-WS_FS 命令。在“tWCKENL_FS + tWCKPRE_static”之后,必须发出 MRW [MR46OP[1]=1B] 以启用 RDQS 切换模式。在 MRW-2 [RDQS toggle mode Enabled] 后“tERQE”通过后,LPDDR5 SDRAM 将开始驱动 RDQS_t 和 RDQS_c。 LPDDR5 设备通过发出 MRW [MR46 OP[1]=0B RDQS 切换模式禁用] 退出 RDQS 切换模式。在“tERQX”从 MRW-2 [RDQS 切换模式禁用] 通过后,LPDDR5 SDRAM RDQS 将转换为高阻抗状态。在 tERQX 期间, WCK 必须继续切换。参考4.2.12 了解有关 tERQE、 tERQX 和 ODT 相关时序的 LPDDR5 增强型 RDQS 训练模式的信息。在 tERQE 和 tERQX 期间,只允许 DES 命令。

RDQS_t/c 输出行为遵循 RDQS:MR20 OP[1:0] 设置。因此,如果 MR20 OP[1:0] 为 00B:RDQS_t 和 RDQS_c 禁用,则启用 RDQS 切换模式没有意义。

在 RDQS 切换模式期间,不允许 Power Down、 SREF、 Deep sleep、 MRR、 Write、 Mask Write、Read、 Write FIFO、 Read FIFO 和 RDC,但是 NOP、 DES、 ACT-1、 ACT-2、 PREpb、可以发行PREab、 REFpb、 REFab、 MRW-1、 MRW-2 和 MPC。在 RDQS 切换模式期间,不允许通过 MR30 OP[3:0] 用于 DCAL 和 MR30 OP[7:4] 用于 DCAU 设置来调整 WCK 占空比。此外,从 RDQS 切换模式进入到退出,内部数据总线用作读取功能。因此,与输出控制、 ODT/NT-ODT 和 WCK 设置有关的 MR 不允许更改:请参阅表 47对于特定的先生。 RDQS 切换模式和增强型 RDQS 训练模式相互排斥,并且 MR46 OP[0] 和 MR46 OP[1] 不允许在同一个 MRW 命令中改变。

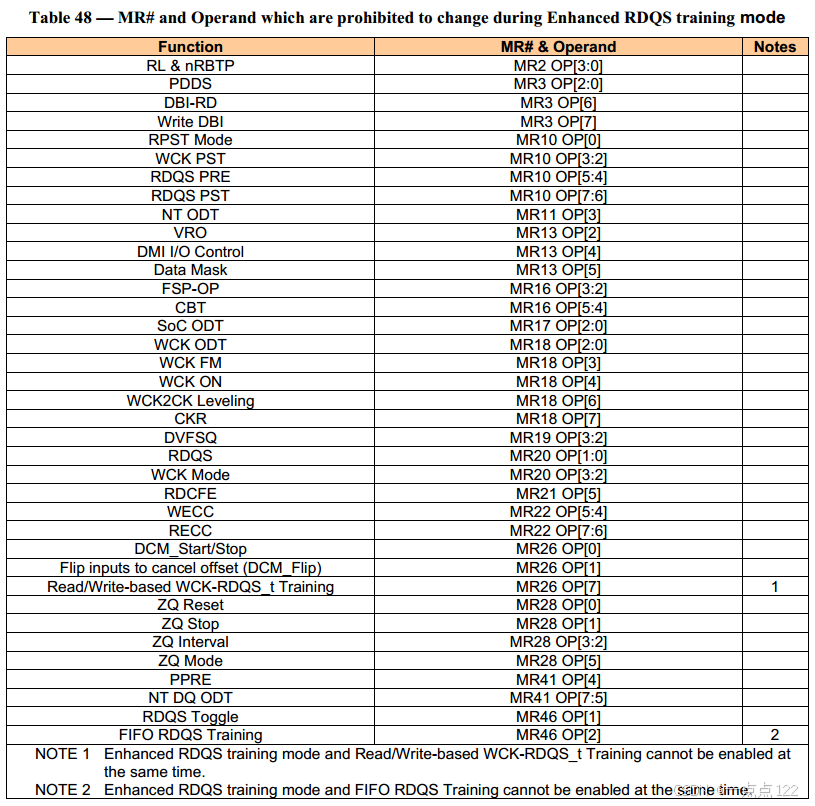

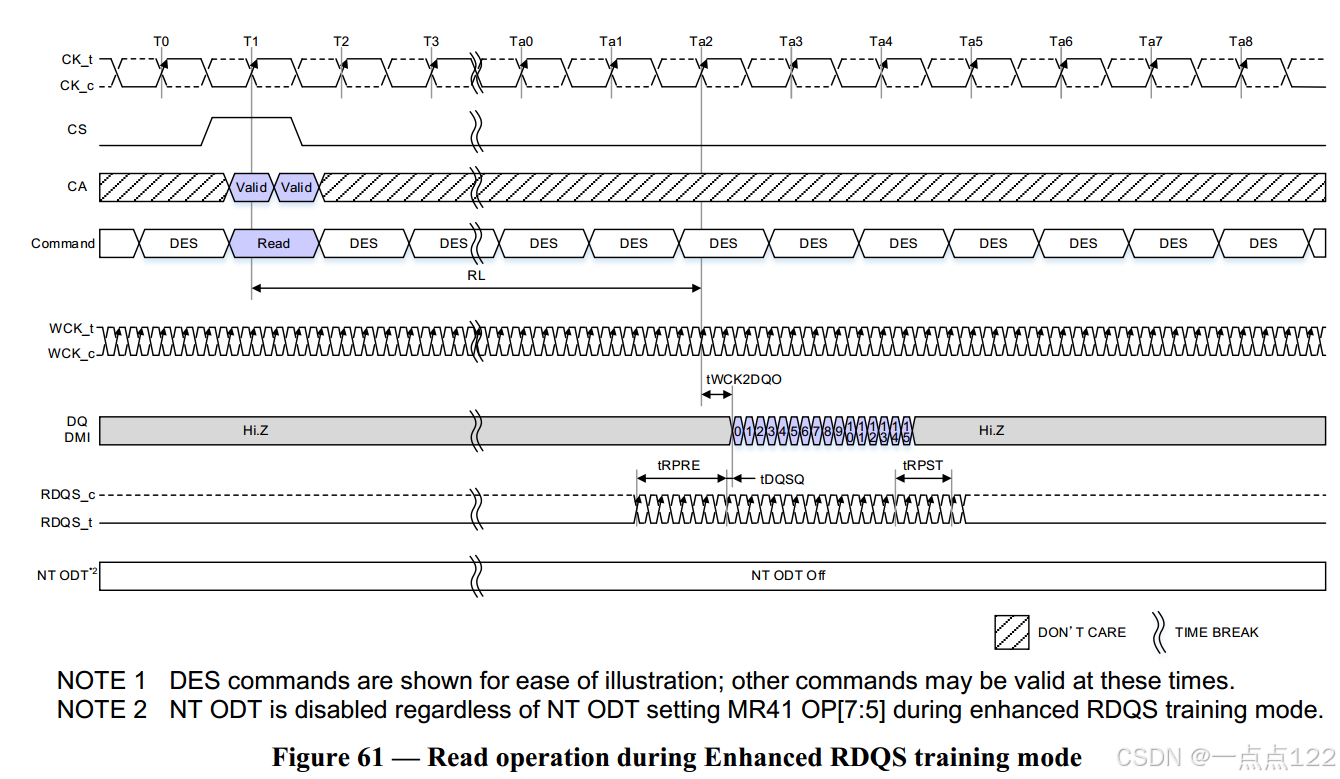

4.2.12 增强型RDQS training模式

LPDDR5 将通过设置 MR46 OP[0] Enhanced RDQS training mode enable 进入 Enhanced RDQS training mode。在发出 MRW 命令之前,需要 CAS WS_FS。在 WCKENL_FS+tWCKPRE 静态之后,必须发出 MRW 命令以启用增强型 RDQS 训练模式。 MRW 之后的 tERQE, LPDDR5 将开始驱动RDQS_t = low 和 RDQS_c = high。

为了保持 RDQS 低阻抗,在增强型 RDQS 训练模式期间, WCK 必须继续切换。

当 LPDDR5 接收到 Read Command 时, LPDDR5 将输出 RDQS 和数据。 RDQS 前导码和后导码跟随在 MR10 OP[7:4] 之后。在突发读取操作之后, LPDDR5 将在此模式下将 RDQS 保持为低阻态。

LPDDR5 通过设置 MR46 OP[0] 增强型 RDQS 训练模式禁用来退出增强型 RDQS 训练模式。tERQX 从 MRW 过去后, LPDDR5 RQDS 将转换为高阻抗状态。在 tERQX 期间, WCK 必须继续切换。

在 tERQE 和 tERQXperiod 中,仅允许 DES 命令以及在增强型 RDQS 模式、读取数据训练模式、ACT-1、 ACT-2、 PREpb、 PREab、 REFpb、 REFab、 RD、 RD32、 MRW-1、 MRW-2、可以下发MRR、 MPC、RDC,但不允许下发其他命令。

前提是如果 DMI 输出行为控制设置为模式 2 (MR13 OP[4]=1B),则禁止发出 RDC 命令。

此外,从增强型 RDQS 训练模式进入到退出,内部数据总线都作为读取功能工作。因此,与输出控制、 ODT/NT-ODT 和 WCK 设置相关的 MR 不允许更改;参考表 48对于特定的先生。 MR46 OP[0] 和 MR46 OP[1] 不允许在同一个 MRW 命令中改变。

RDQS_t 和 RDQS_c 驱动遵循 MR20 OP[1:0]。

在增强型 RDQS 启用 MRW 后 tRDQE_OD 过去后, RDQS ODT 被禁用。在增强型 RDQS 禁用 MRW之后经过 tRDQX_OD 后,启用 RDQS ODT。

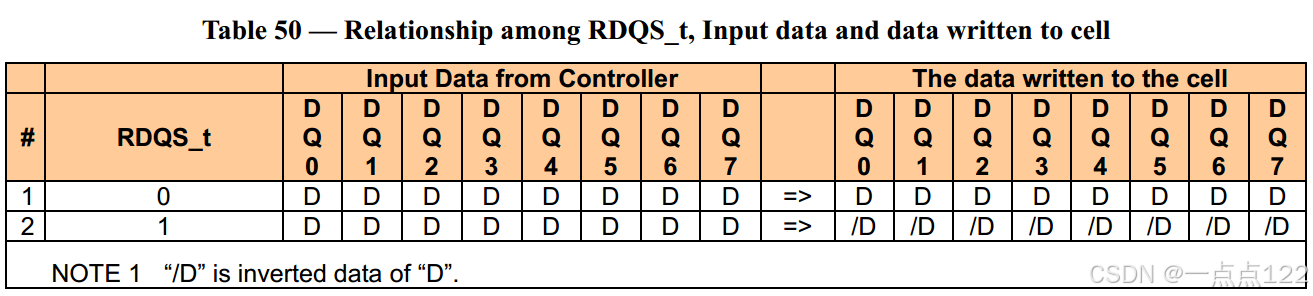

4.2.13 基于读/写的 WCK-RDQS_t 训练

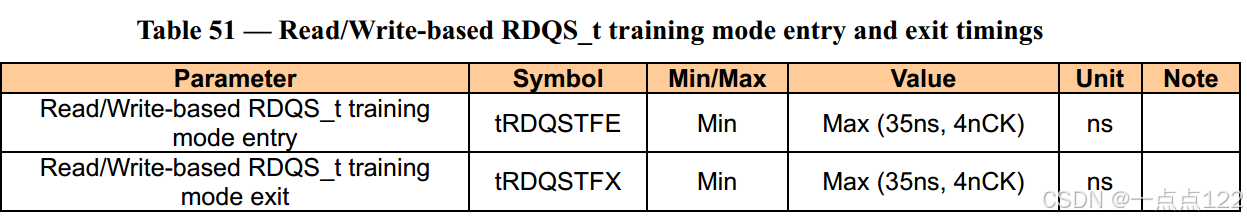

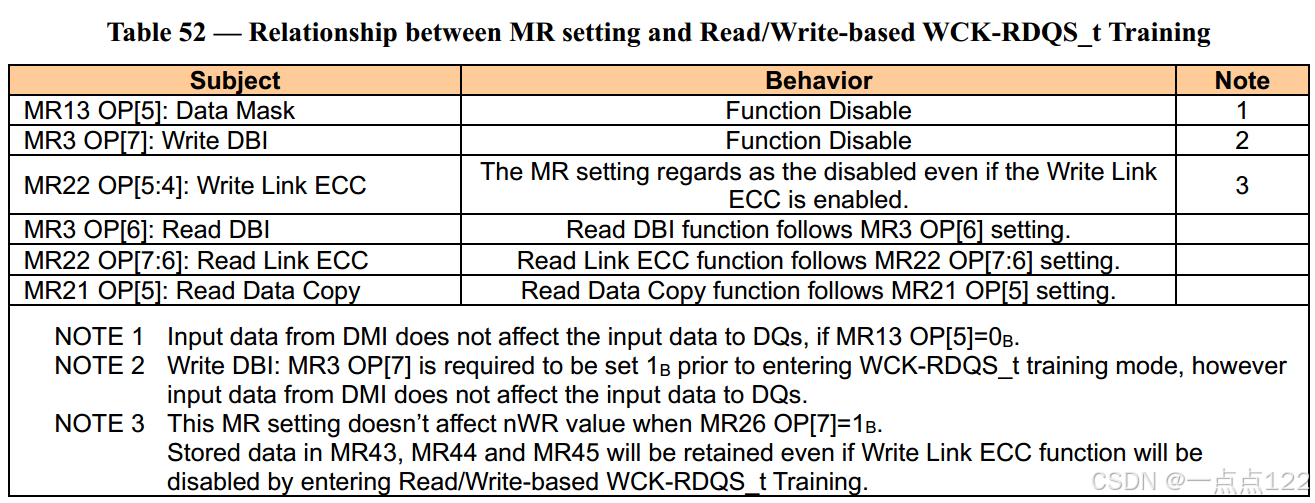

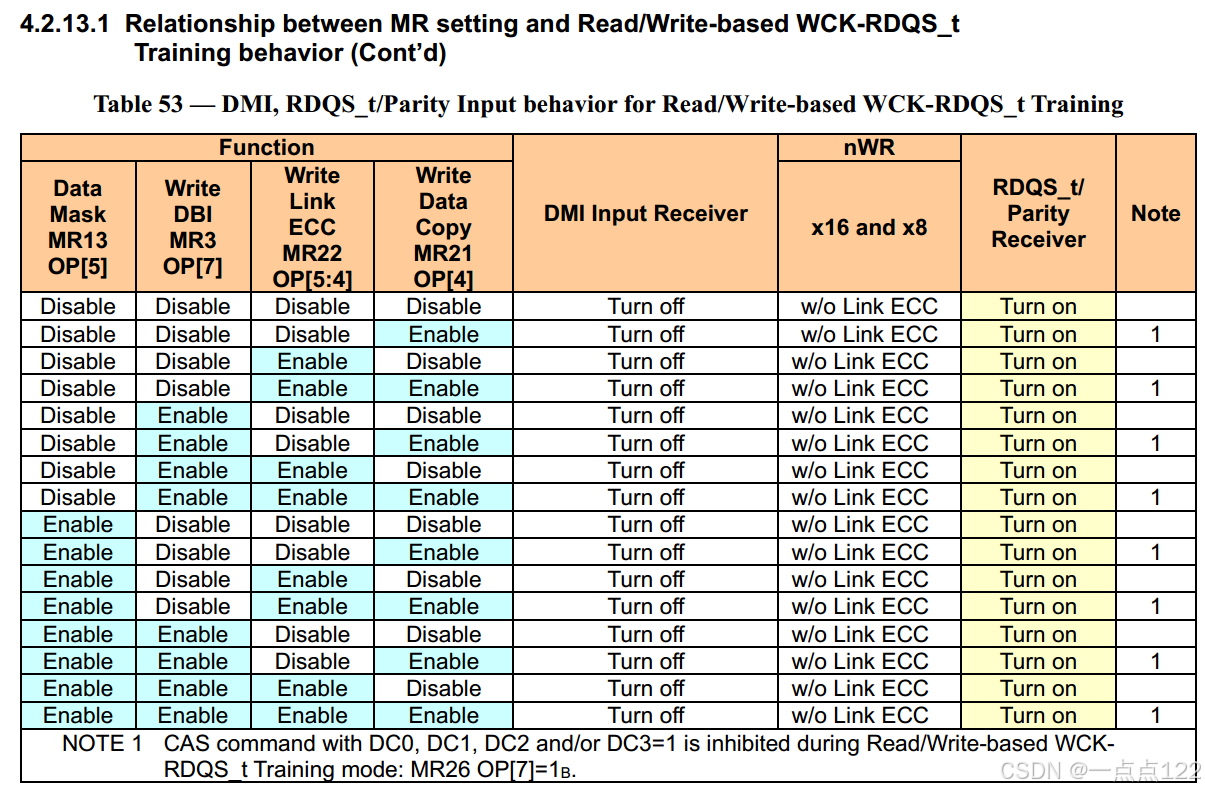

启用 Write Link ECC 时, RDQS_t 引脚在写操作期间用作奇偶校验。 RDQS_t、 DQ数据、 WCK需要经过训练才能满足写时序。除了 WCK-RDQS_t/Parity Training in4.2.10.2, 它利用 Read 和Write FIFO 命令进行 WCK-RDQS_t 训练, LPDDR5 SDRAM 可选地支持通过 Read 和 Write 命令进行 WCK-RDQS_t 训练。如果LPDDR5设备支持Read/Write-based WCK-RDQS_t训练功(MR26 OP[6]=1B),用户可以通过设置MR26 OP[7]=1B来开启训练功能。

Read/Write-based WCK-RDQS_t Training MR26 OP[7]=1B 只能用于1600MHz以上的WCK频率,以及Link ECC功能。

要进入基于读/写的 WCK-RDQS_t 训练模式,需要一个 MRW 命令来设置 MR26 OP[7]=1B。tRDQSTFE 从 MRW 命令传递后, LPDDR5 SDRAM 准备好进行基于读/写的 WCK-RDQS_t 训练,其中RDQS_t 的行为类似于 DMI 引脚,启用了写 DBI(基于读/写的 WCK-RDQS_t 训练可能使用写 DBI电路).因此,写入 DBI: MR3 OP[7] 需要在进入 WCK-RDQS_t 训练模式之前设置为 1B。此外,即使启用了写入 DBI, LPDDR5 SDRAM 在写入操作期间也会忽略 DMI 输入: MR3 OP[7] = 1B。在这种训练模式下,控制器需要遵循 LPDDR5 SDRAM 行和读/写操作来访问 SDRAM。在发出读或写命令之前需要一个银行激活命令。通过发出 WS_WR=1 的 CAS 命令,紧随其后的是写入命令,将训练数据写入 DRAM。在 RDQS_t 被采样为高电平的情况下,LPDDR5 SDRAM 反转在 DQ 输入上接收到的写入数据, 或者,如果 RDQS_t 被采样为低电平,则保持写入数据不反转。通过 Write 命令写入 SDRAM 的数据可以通过发出 WS_RD=1 的 CAS 命令然后立即执行 Read 命令来回读。控制器将读取的数据与“预期”数据进行比较,以查看是否需要进一步训练。连续读取或写入命令的数量,即训练模式的长度,不受限制。当然,可以在没有WCK Sync 的情况下发出 Write/Read 命令。WCK 同步状态期间的命令。训练完成后, LPDDR5 SDRAM 通过设置 MR26 OP[7]=0B 退出Read/Write-based WCK-RDQS_t 训练模式。tRDQSTFX 从 MRW 过去后, LPDDR5 恢复正常操作,其中 RDQS_t 在写入操作期间根据写入链路 ECC 设置运行。

在 tRDQSTFE 和 tRDQSTFX 期间,只允许 DES 命令。

在基于Read/Write 的WCK-RDQS_t 训练过程中,禁止使用以下命令以简化训练过程。

读 FIFO (RFF)

写 FIFO (WFF)

屏蔽写入 (MWR) CAS_Write

数据复制 (WDC) CAS_Write

X (WRX)

读取 DQ 校准 (RDC)

4.2.13.1 MR 设置与基于读/写的 WCK-RDQS_t 训练行为之间的关系

在基于读/写的 WCK-RDQS_t 训练模式(即 MR26 OP[7]=1B)期间,模式寄存器设置和 DMI、RDQS_t/奇偶校验引脚行为的处理如中所示表 52。

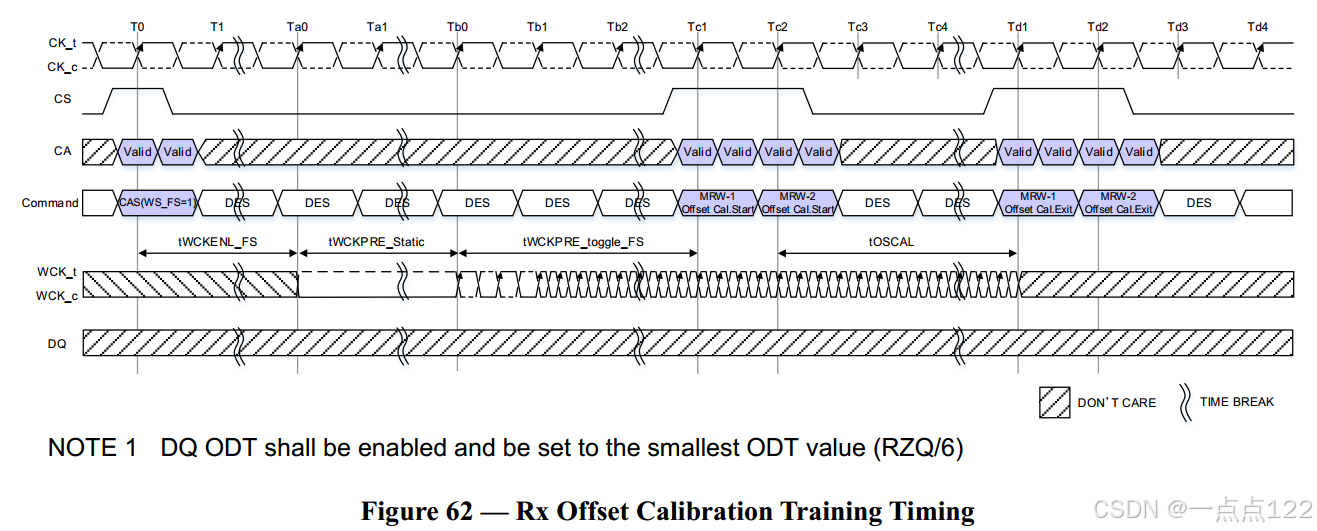

4.2.14 Rx 偏置校准训练

4.2.14.1 偏置校准培训说明

LPDDR5X SDRAM 提供用于调整 DQ Rx 偏移的偏移校准训练。建议在每次上电和初始化训练序列时进行训练,以应对 SDRAM 运行条件的变化。偏移校准由 MR15 OP[7] 启用。当 SDRAM 开始训练时, DQ 通道可以悬空。在发布 MRW-1 和 MRW-2 以启动偏移校准培训后,应自动启用 DQ ODT。在训练期间,要求 SDRAM 处于 WCK2CK 同步状态,并且 WCK 应以全速率切换。建议在训练前使用 CAS(WS_FS) 将 WCK 同步到 CK,或者您可以使用之前操作的 WCK2CKsync 状态。

4.2.14.2 偏置校准训练序列

下面是偏移校准训练序列。

1. 发出 CAS(WS_FS=1) 命令并操作 WCK2CK 同步参考 7.2.1.5 WCK2CK Sync operation with CAS(WS_FS=1)”并保持全速率切换 WCK。

2. 发出 MRW-1 和 MRW-2 以开始偏移校准培训

3. 等待 tOSCAL,直到 LPDDR5X SDRAM 完成偏移校准。

4. 发出 MRW-1 和 MRW-2 以退出偏移校准培训。

补充内容如下:

ZQ校准的目的

为了提高信号完整性,并增强输出信号的强度,DDR内存中引入了终端电阻和输出驱动器,而为了在温度和电压发生变化的场景下仍然能够保持信号完整性,就需要对这些终端电阻和输出驱动器进行校准;

未经校准的终端电阻会直接影响到信号质量,而调整不当的输出驱动器则会使得有效信号跃迁偏离参考电平,从而导致数据和选通信号之间出现偏差。

LPDDR5的training流程:

- 上电&复位

- ZQ校准

- CBT(command bus training)

- DQ training(1.RD DQ Training 2.DQS-DQ Training)

-

Read Training(1.Read DQS gate training 2.Read data eye training 3. Read Preamble training)

ZQ参考:

https://www.eet-china.com/mp/a270945.html

LPDDR4芯片学习(四)——DDR Training_学习_-特立独行的猪--腾讯云开发者社区

FSP参考:

DDR Study - LPDDR4 Clock Switch_lpddr4 fsp需要soc支持吗-CSDN博客

https://zhuanlan.zhihu.com/p/617195218

DDR Study -LPDDR5 DFE / Data Copy / Write X / Link ECC / FSP / Non-Target ODT-CSDN博客

DVFSC参考:

DDR Study -LPDDR5 vs LPDDR4_dvfsq-CSDN博客

DM参考:

https://www.eet-china.com/mp/a86723.html

DBI参考:

DDR4中的DBI引脚与DBI功能_ddr dbi-CSDN博客

LPDDR5结构图参考:

1391

1391

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?