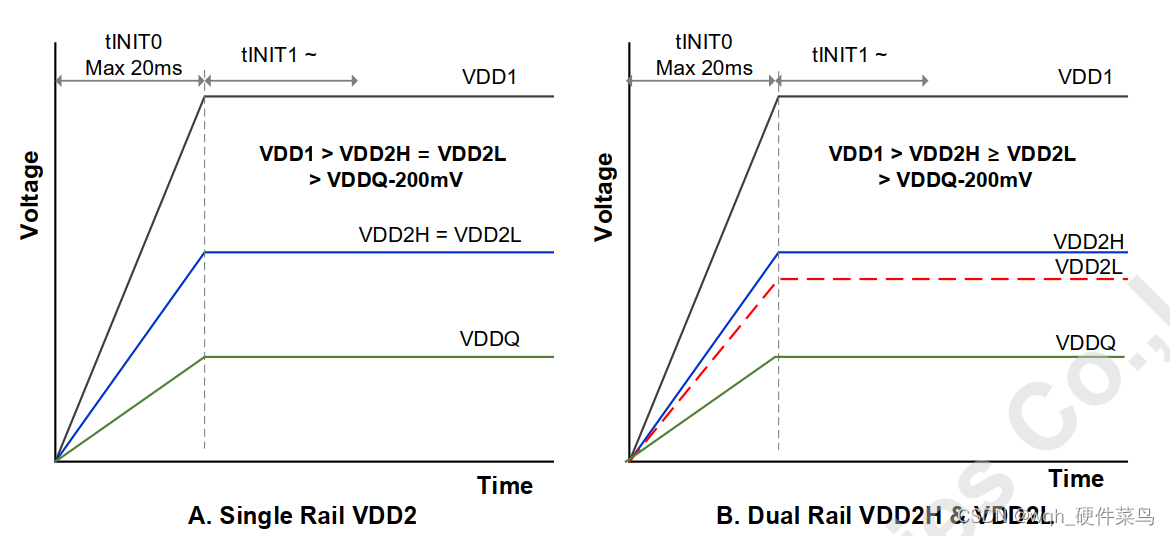

图1 上电控制需求

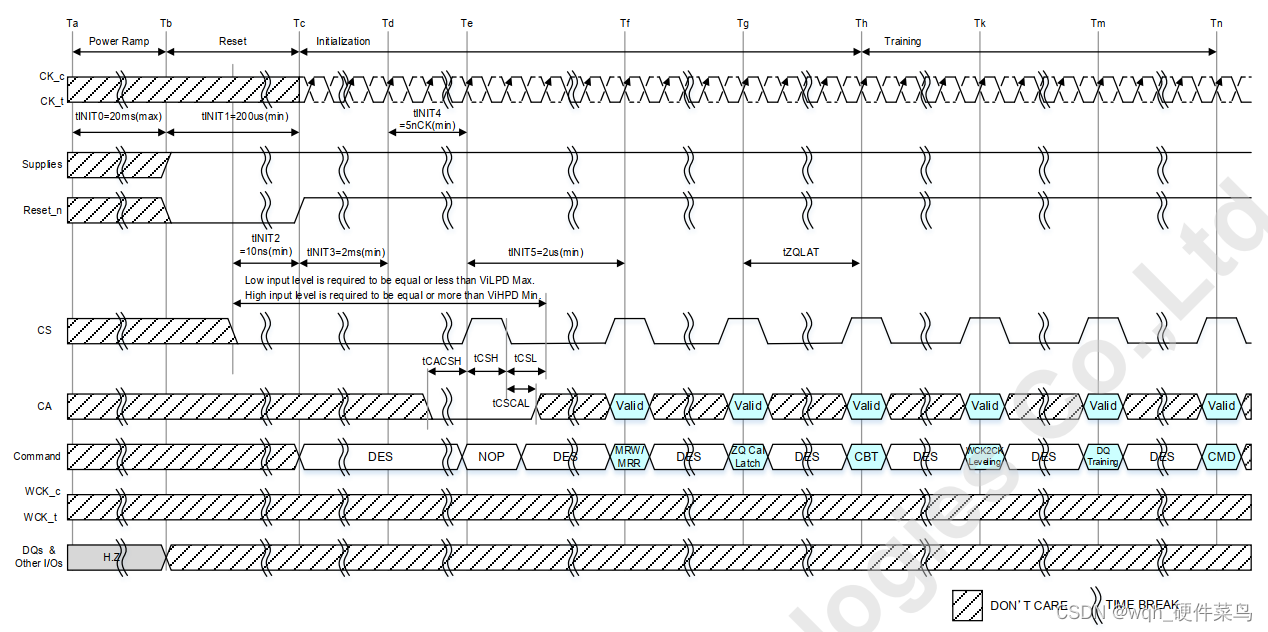

图2 初始化流程

图2上方有Ta~Tn的时间戳,下面介绍步骤时要引用,请自行对应。

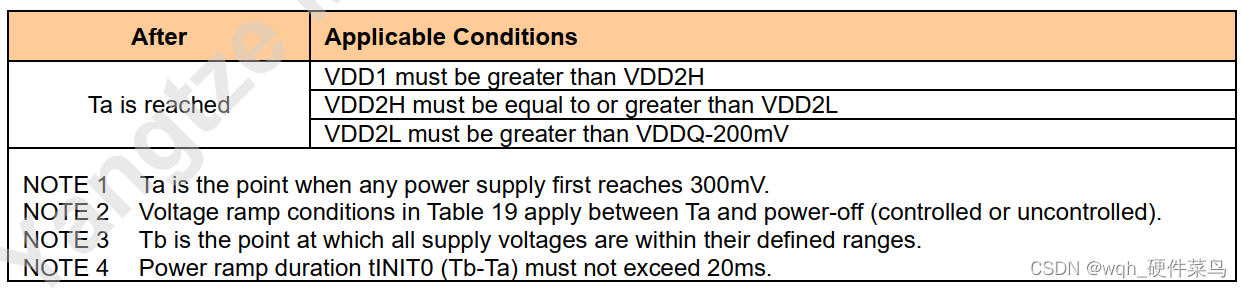

1) 通电时(Ta之后),建议RESET_n为LOW(≤0.2 x VDD2H),所有其他输入应在VILmin和VIHmax之间。SDRAM输出保持在High-Z,而RESET_n保持在LOW。表1提供了电源电压上电要求。VDD1必须在与VDD2H相同的时间或更早的时间上电。VDD2H必须在与VDD2L相同的时间或更早的时间上电。VDD2L必须在与VDDQ相同的时间或更早地上电。

表1 电源上电条件

2) 在完成电压上电(Tb)之后&#

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

411

411

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?