计算机系统原理实验——总线-运算器-存储器-数据通路日志

实验日期:2020.3.4

ps:工程文件在博客——计算机系统原理/模型机中

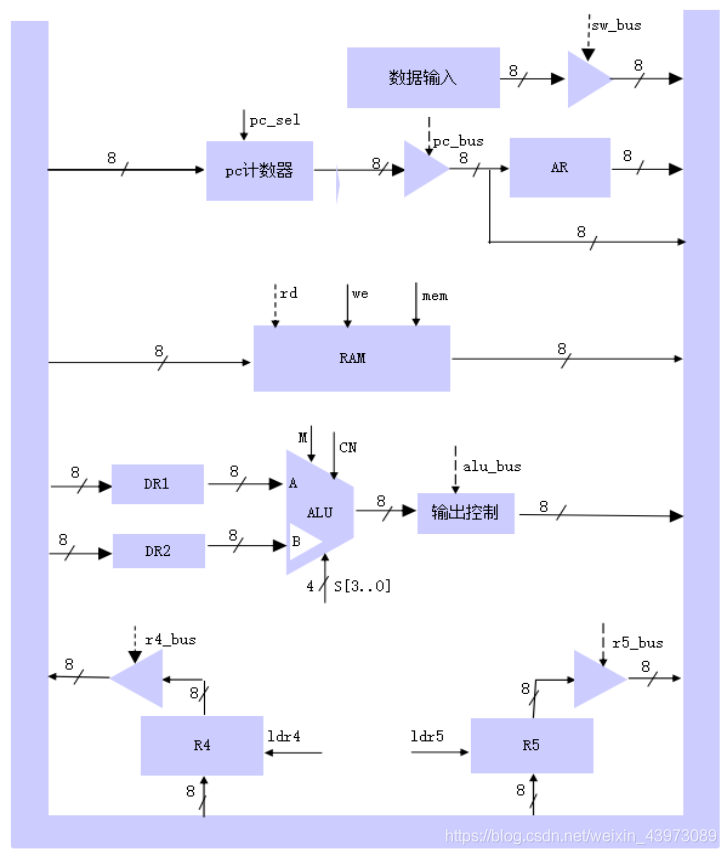

一、数据通路结构图

数据通路:将运算器通过数据总线连在一起

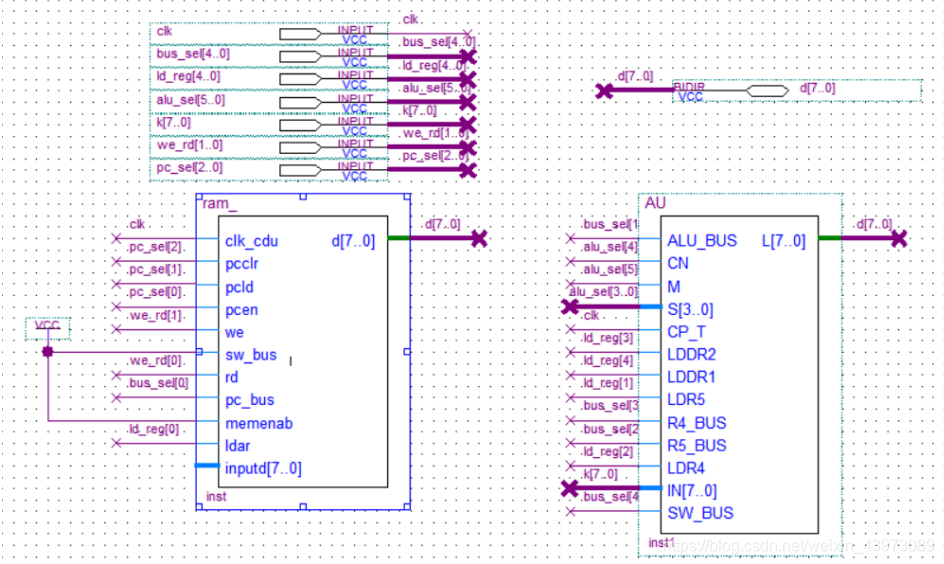

二、数据通路电路图

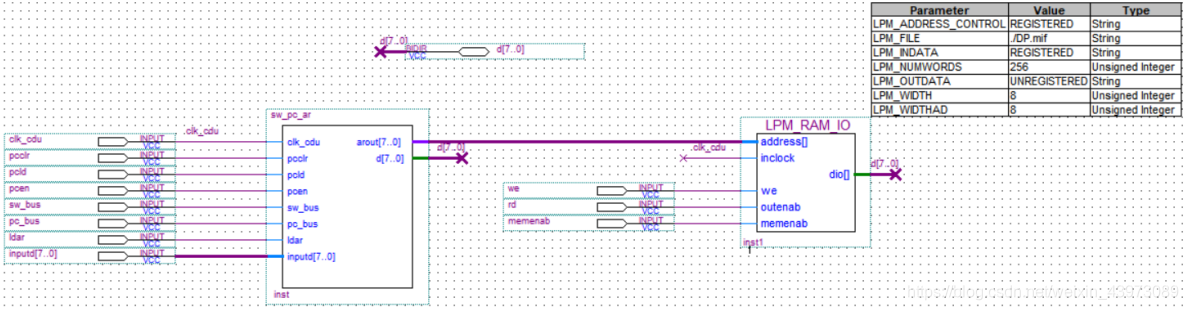

ram_元件电路图

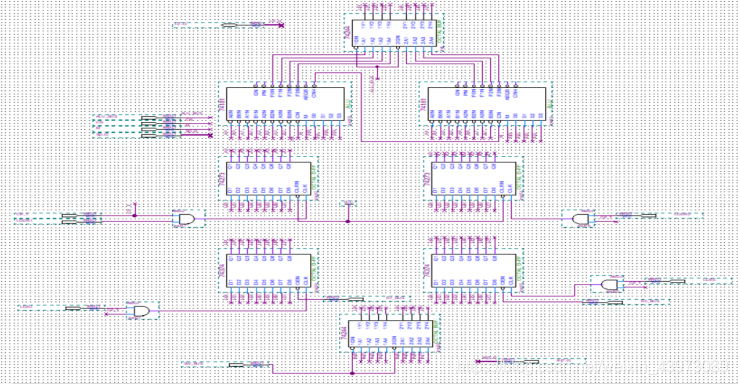

AU元件电路图

三、仿真验证

1、参数设置

芯片类型:

Family : Cyclone II

Device : EP2C5T144C8

2、信号功能描述

clk:时钟信号

bus_sel:控制数据进入总线

ld_reg:控制数据存入寄存器

pc_sel:控制pc计数器的状态

we_rd:控制ram的存取

k:输入信号

alu_sel:控制alu的各种运算

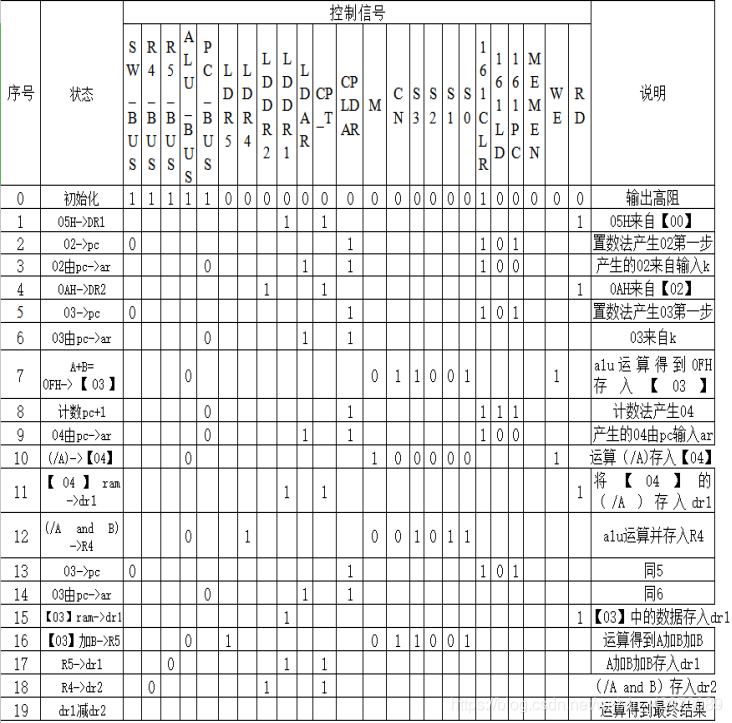

3、仿真内容

mif内存初始化实现数据A=05H→【00】, 数据 B=0AH→【02】

①计算 (A加B)减【(/ A)and B )】加B

② A 加B → 【03】 置数发产生【03】地址

③ / A →【04】 计数法产生【04】地址

④ (/ A)and B )→ R4

⑤ 【03】 加B → R5

⑥ R5减R4

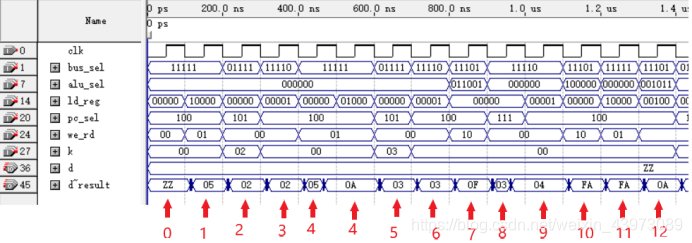

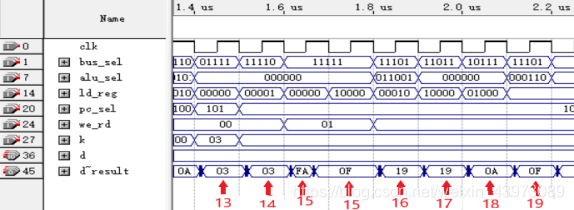

4、仿真波形

5、波形说明

说明:

(1)先找准初始状态,每次有效操作,只需改动相关的操作信号状态即可。如表中1状态,09H->DR1只需改SW为0,LDDR1为1,CP_T为1。

(2)CP_T,CPLDAR为正脉冲信号。

(3)序号0、1、2……可用于波形图中标示。

数据记录依据具体仿真内容完成

6、仿真结论

通过波形仿真可知,运算结果与运算步骤全部正确,波形逻辑仿真正确;证明电路图正确。

四、日志记录

1、结合以下思考题,试述如何构造总线电路?

电路中BIDIR端口的用途是什么?

举例说明画电路图中连接bus line 与node line的区别,总线与支线命名方式是什么?

Exp_bus.vhdl中如何实现双向总线的定义与缓冲?

答:

BIDIR端口为双向端口,既可以实现输入又可以输出信号;bus line(粗线)中含有多个支线,是多个node line(细线)的汇总,从bus line中可以引出node line,也可以使node line汇总为bus line,总线命名一般为X[n…a],支线为X[n]、X[n-1]、…、X[a],其中X为名称,n-a为总线中汇总信号的数目;exp_bus.vhdl中通过信号bus_reg来定义双向总线,通过输入信号SW-bus、R1-bus、R2-bus、R3-bus来缓冲总线的输入。

构造总线电路,首先要明确有几个寄存器,要为其分配对应的输入到总线的控制信号和从总线得到数据的加载信号,之后确定寄存器之中的信息位数,最后按需求连接总线,接着进行验证和修改,最后下载到板子上观察现象。

2、试述实验8位运算器如何实现复合运算?

答:

分步计算:首先将初始数据存入暂存器DR1、DR2,用ALU计算出可以计算出的中间结果,通过总线将其保存到寄存器中,之后继续分步计算得到进一步的结果,直到得到最后的正确结果。应注意计算过程中中间结果的保存不能将还有用的数据覆盖,应注意寄存器的选择。

3、分析仿真结果图4-3-14(P241)中200ns后执行读RAM【01】中数据时为何会先出现E1?

答:

因为175ns处的上升沿,arout输出的还是00,RAM读出数据时在时钟上升沿触发,在上沿有效之前显示为前一地址【00】H单元的数据E1

本文档记录了一次关于计算机系统原理的实验,涉及数据通路结构、电路图、8位运算器复合运算实现、总线构造方法,以及对实验波形的详细解读。通过仿真验证了运算过程的正确性和总线设计的合理性。

本文档记录了一次关于计算机系统原理的实验,涉及数据通路结构、电路图、8位运算器复合运算实现、总线构造方法,以及对实验波形的详细解读。通过仿真验证了运算过程的正确性和总线设计的合理性。

3446

3446

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?