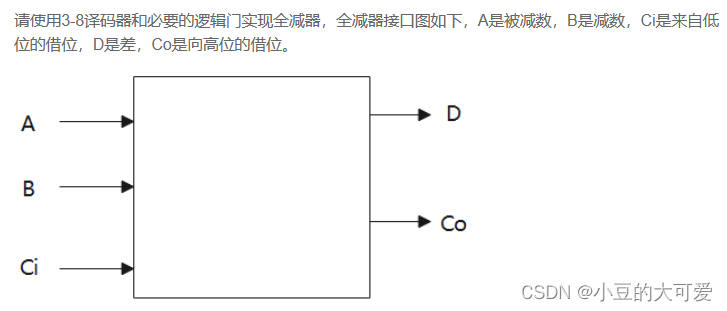

一、题目:

3-8译码器代码如下,可将参考代码添加并例化到本题答案中。

module decoder_38(

input E ,

input A0 ,

input A1 ,

input A2 ,

output reg Y0n ,

output reg Y1n ,

output reg Y2n ,

output reg Y3n ,

output reg Y4n ,

output reg Y5n ,

output reg Y6n ,

output reg Y7n

);

always @(*)begin

if(!E)begin

Y0n = 1'b1;

Y1n = 1'b1;

Y2n = 1'b1;

Y3n = 1'b1;

Y4n = 1'b1;

Y5n = 1'b1;

Y6n = 1'b1;

Y7n = 1'b1;

end

else begin

case({A2,A1,A0})

3'b000 : begin

Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b001 : begin

Y0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b010 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b011 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b100 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b101 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;

end

3'b110 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;

end

3'b111 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;

end

default: begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

endcase

end

end

endmodule

输入描述:

input A ,

input B ,

input Ci

输出描述:

output wire D ,

output wire Co

二、全减器的真值表

这篇文章写的很好,全减器真值表怎么理解?

有一些关键点如下:

1、Ci是低位向本位的借位,Co是本位向高位的借位;

2、二进制的借位规则是“借1当2”

根据这两个关键点即可得出全减器的真值表

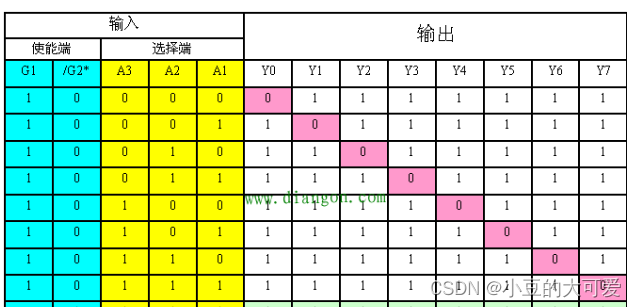

三、3-8译码器的真值表

四、3-8译码器实现全减器

由全减器的真值表可知,D和Co的最小项表达式为:

D = m1 | m2 | m4 | m7;

Co = m1 | m2 | m3 | m7;

又因为3-8译码器的真值表对应的是最小项取反,

所以若需要用3-8译码器表达全减器,需要根据反演定理对D和Co的表达式进行转换:

D = ~(m1’ & m2’ & m4’ & m7’);

Co = ~(m1’ & m2’ & m3’ & m7’);

注意m是全减器真值表的最小项,设M是3-8译码器的真值表

所以表达式为:

D = ~(M1 & M2’ & M4 & M7);

Co = ~(M1 & M2 & M3 & M7);

由此便可写出verilog代码:

`timescale 1ns/1ns

module decoder_38(

input E ,

input A0 ,

input A1 ,

input A2 ,

output reg Y0n ,

output reg Y1n ,

output reg Y2n ,

output reg Y3n ,

output reg Y4n ,

output reg Y5n ,

output reg Y6n ,

output reg Y7n

);

always @(*)begin

if(!E)begin

Y0n = 1'b1;

Y1n = 1'b1;

Y2n = 1'b1;

Y3n = 1'b1;

Y4n = 1'b1;

Y5n = 1'b1;

Y6n = 1'b1;

Y7n = 1'b1;

end

else begin

case({A2,A1,A0})

3'b000 : begin

Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b001 : begin

Y0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b010 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b011 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b100 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b101 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;

end

3'b110 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;

end

3'b111 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;

end

default: begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

endcase

end

end

endmodule

module decoder1(

input A ,

input B ,

input Ci ,

output wire D ,

output wire Co

);

wire M0,M1,M2,M3,M4,M5,M6,M7;

decoder_38 u_decoder_38(

.E (1'b1),

.A0 (Ci),

.A1 (B),

.A2 (A),

.Y0n(M0),

.Y1n(M1),

.Y2n(M2),

.Y3n(M3),

.Y4n(M4),

.Y5n(M5),

.Y6n(M6),

.Y7n(M7)

);

assign D = ~((M1)&(M2)&(M4)&(M7));

assign Co = ~((M1)&(M2)&(M3)&(M7));

endmodule

1613

1613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?