专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

分析

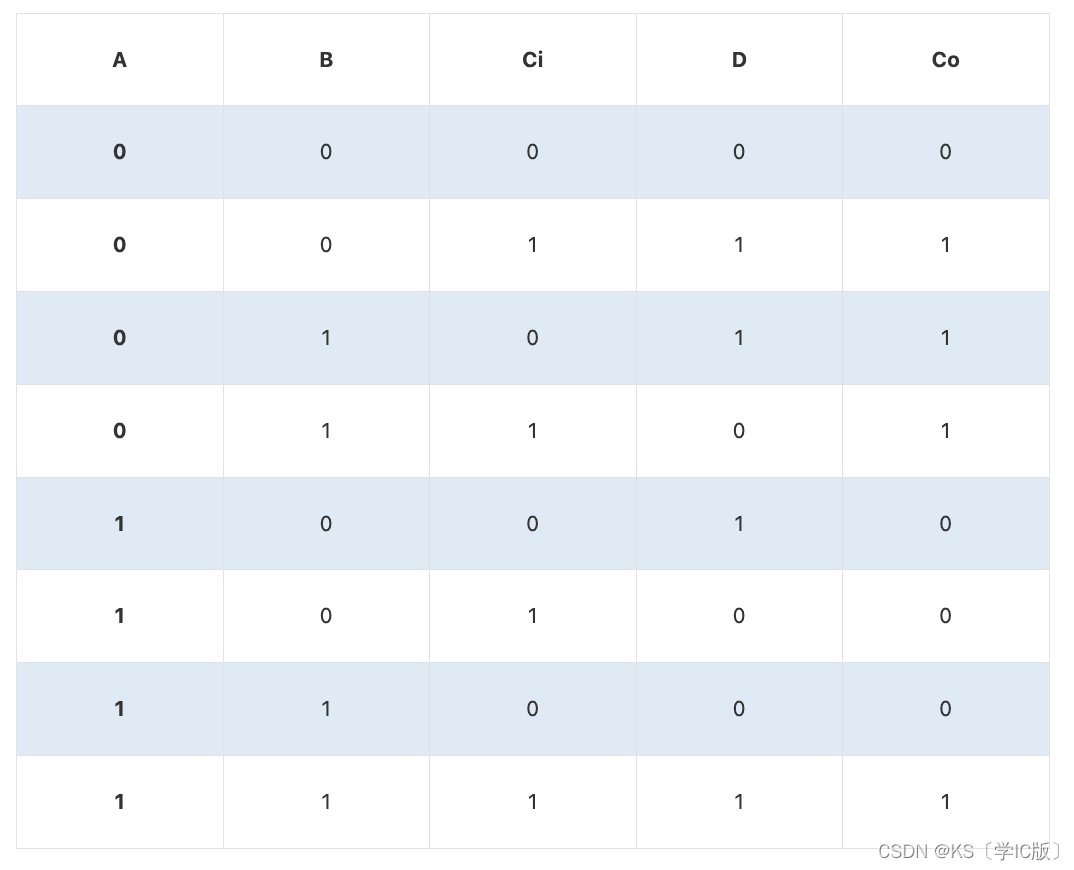

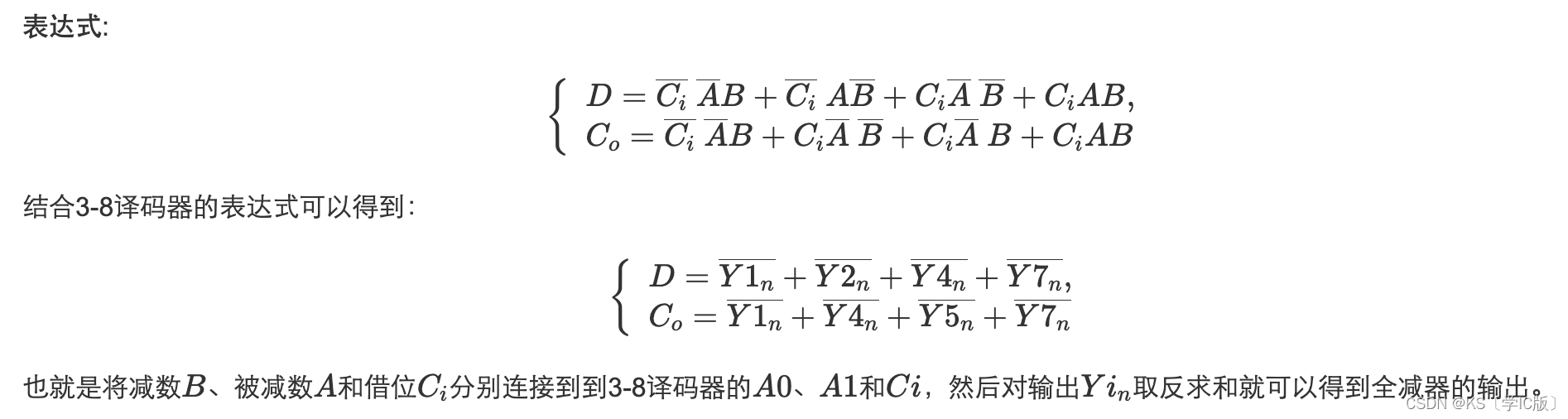

首先列出3-8译码器和全减器的真值表 全减器真值表如下

3-8译码器真值表如下

`timescale 1ns/1ns

module decoder_38(

input E ,

input A0 ,

input A1 ,

input A2 ,

output reg Y0n ,

output reg Y1n ,

output reg Y2n ,

output reg Y3n ,

output reg Y4n ,

output reg Y5n ,

output reg Y6n ,

output reg Y7n

);

always @(*)begin

if(!E)begin

Y0n = 1'b1;

Y1n = 1'b1;

Y2n = 1'b1;

Y3n = 1'b1;

Y4n = 1'b1;

Y5n = 1'b1;

Y6n = 1'b1;

Y7n = 1'b1;

end

else begin

case({A2,A1,A0})

3'b000 : begin

Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b001 : begin

Y0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b010 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b011 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b100 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

3'b101 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;

end

3'b110 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;

end

3'b111 : begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;

end

default: begin

Y0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1;

Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;

end

endcase

end

end

endmodule

module decoder1(

input A ,

input B ,

input Ci ,

output wire D ,

output wire Co

);

wire [7:0] Y ;

assign D = ~Y[1] + ~Y[2] + ~Y[4] + ~Y[7] ;

assign Co = ~Y[1] + ~Y[2] + ~Y[3] + ~Y[7] ;

decoder_38 d1(

.E (1 ),

.A0(Ci ),

.A1(B ),

.A2(A ),

.Y0n(Y[0]),

.Y1n(Y[1]),

.Y2n(Y[2]),

.Y3n(Y[3]),

.Y4n(Y[4]),

.Y5n(Y[5]),

.Y6n(Y[6]),

.Y7n(Y[7])

);

endmodule

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?