STM32时钟树

提示:本笔记是根据B站UP @keysking 讲解所整理得到

逻辑门带来的问题:

组合逻辑电路由于外部电平的改变和门电路处理速度(MOS管的充放电速度)相较于裸线传输速度的滞后,可能会影响寄存器中值的改变。比如裸线状态的直接改变,此时门电路的结果尚未输出,就会导致寄存器中暂时会出现一个错误的状态。于是有一个好的解决方法,在寄存器之前放置一个边沿触发器,这个器件的特点是,只有当控制端接收到一个上升沿信号的时候,输出端的信号才会变得和输入端保持一致,其他时间,无论输入端怎么变化,输出端都是不会发生任何变化。

当在控制端给了周期方波信号,在一个周期内,门电路执行运算产生的任何副作用都不会影响到寄存器的值,等一切稳定后,方波的上升沿到达,最终的运算结果才会进入寄存器。这里的方波信号,就是时钟信号。从这一角度阐述了时钟信号的必要性。

时钟信号:

时钟信号是由时钟源产生,通过时钟树传播到整个芯片之中。

- 几个概念:

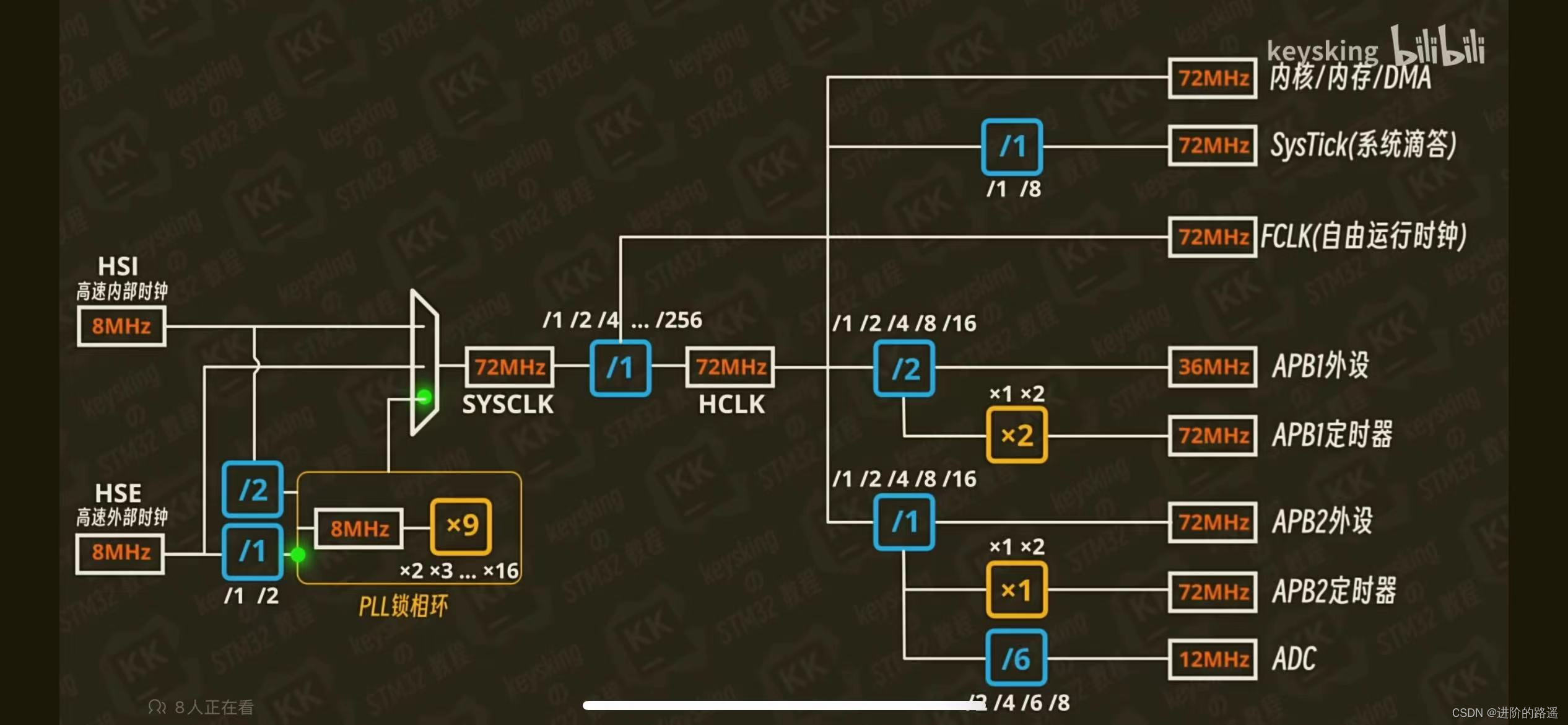

SYSCLK: 系统时钟,HSI或者HSE选择一个。

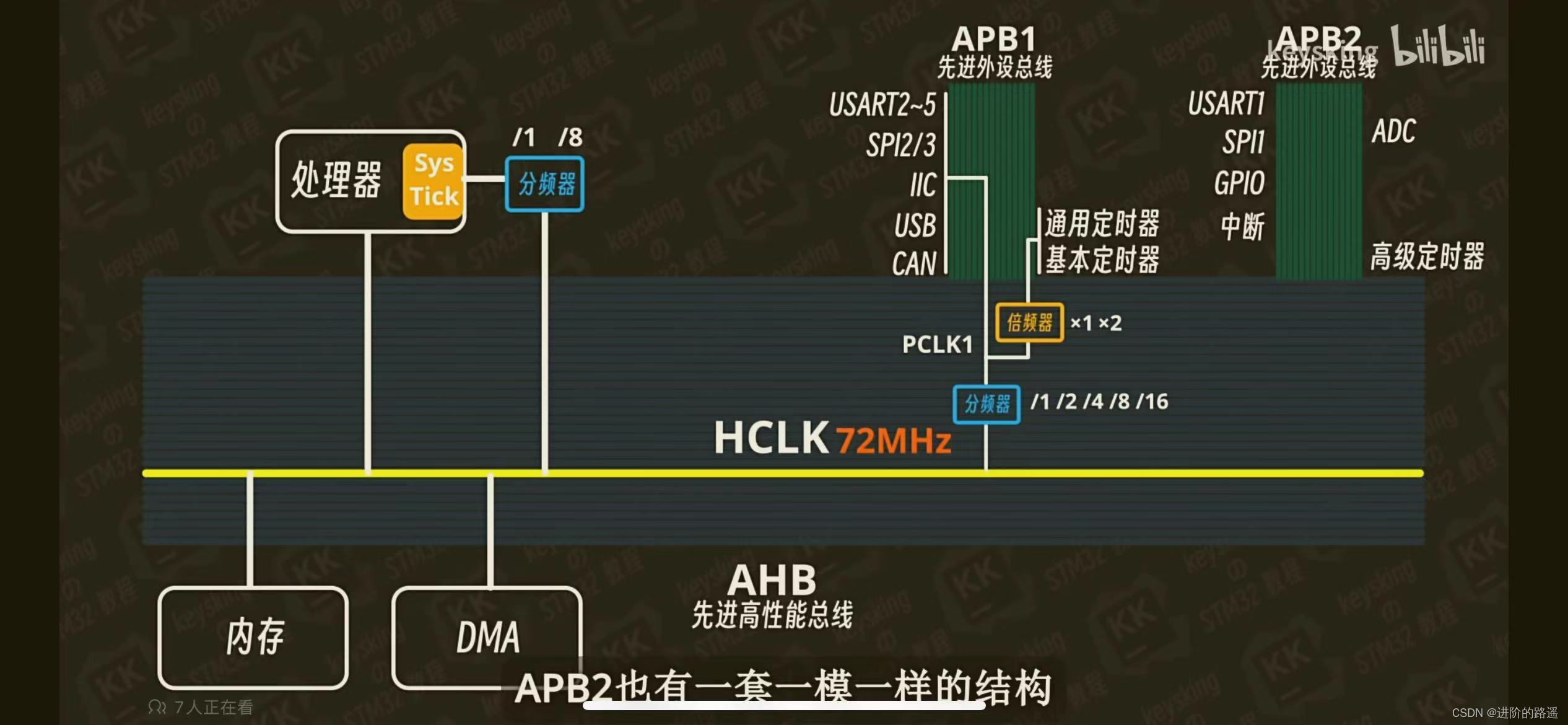

AHB(Advanced High Performance Bus):先进高性能总线,作为STM32总线的主干线。

HCLK:(源头来自于HSI、HSE)AHB总线中的时钟线。直接给处理器、内存、DMA提供时钟信号。

APB(Advanced Peripheral Bus): 先进外设总线,有两条,专门用来连接外设,通过桥接器连接到AHB总线上。

PCLK(1/2): APB1总线的时钟信号,由HCLK分频(/1 /2 /4 /8 /16)得到,供给除了定时器以外的其他外设。而定时器的时钟信号来自于PCLK1的倍频(x1 x2)。

HSI(高速内部时钟,8MHZ): STM32默认使用的时钟源,精度稍差。

HSE(高速外部时钟,8MHZ): 精度很高。

Systick:一个独立的24位定时器,其时钟频率来自于HCLK的分频(/1 /8),用于为程序提供一个时间基准。

CSS:时钟安全系统,它可以子啊HSE发生故障的时候立刻将时钟源切换回HSI。

MCO:时钟输出功能,默认引脚PA8。

FCLK:自由运行时钟,HCLK在STM32进入低功耗模式之后,会失去作用,这FCLK从分频器引出,不受HCLK的影响。

时钟树:

3312

3312

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?