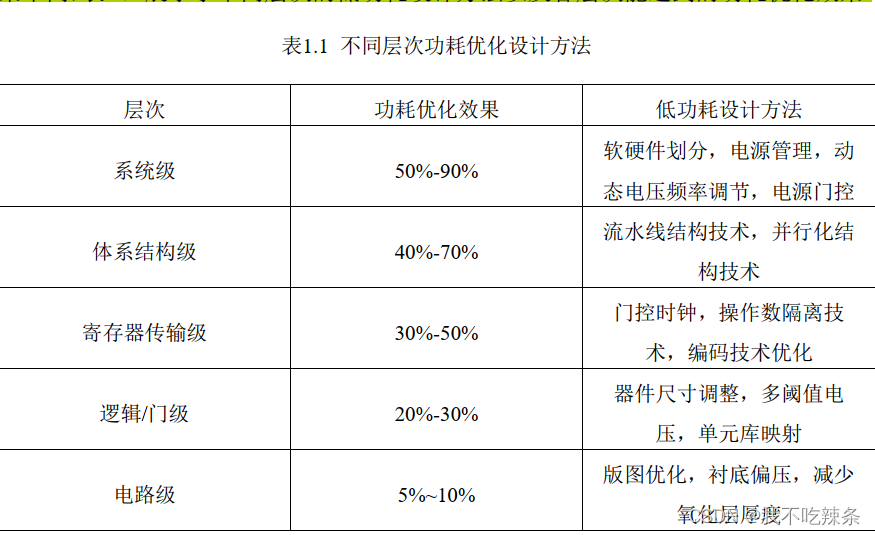

在低功耗电路设计方面,研究者从静态功耗和动态功耗的角度入手, 提出了许多成熟的方法,在不同层次对功耗进行优化。层次越低的优化手段,优化效果越低, 所以业内主要的工作是从高层次的进行低功耗设计。 低功耗设计方法有很多,低功耗设计贯穿集成电路设计的不同阶段。目前,低功耗研究划分为多个层次,包括系统级、体系结构级、 寄存器传输级、 逻辑/门级和电路级五个层次。每个层次对功耗的优化效果不同,表 1.1 展示了不同层次的低功耗设计方法以及各层次能达到的功耗优化效果。

影响芯片功耗的两个重要因素是芯片的工作时钟频率和工作电压,因此系统层级最有效的低功耗设计手段是电源管理,电源管理通过控制芯片的供电电源和时钟有效的降低系统工作功耗。在 CPU 的低功耗设计方面,目前业界主要使用的电源管理方案是功耗管理技术(PM)、 动态电压频率调整技术(DFVS) 和自适应电压调节技术(AVS)。

功耗来源:

- 动态功耗

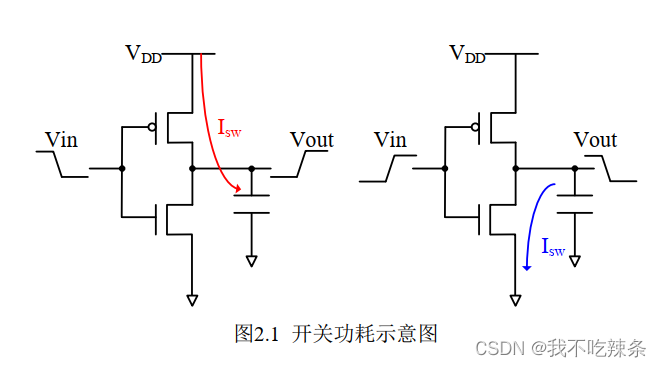

动态功耗包括两个部分: 由于信号变化对 MOS 管的寄生电容充电和放电产生的损耗, 由于电流流过输入信号引起的电源到地短路通路产生的电流损耗[26]。开关功耗的示意图如图 2.1 所示, 寄生电容充电过程中反相器输出端由 0 到 1(低电平到高电平)变化,寄生电容放电过程中反相器输出端由 1 到 0(高电平到低电平)变化。

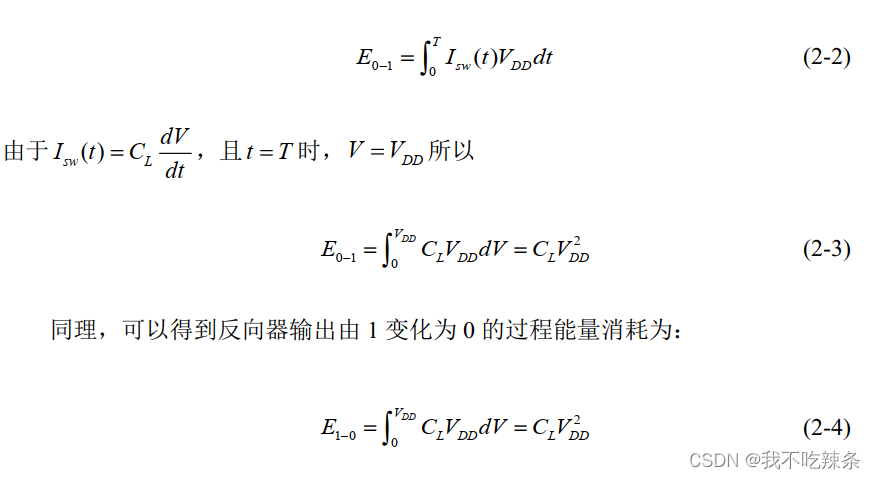

开关功耗是由图 1.1 中所示的开关电流Isw引起的。以反相器输出发生 0 到 1 变化过程为例,消耗的能量为:

开关功耗是由图 1.1 中所示的开关电流Isw引起的。以反相器输出发生 0 到 1 变化过程为例,消耗的能量为:

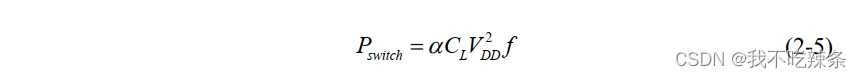

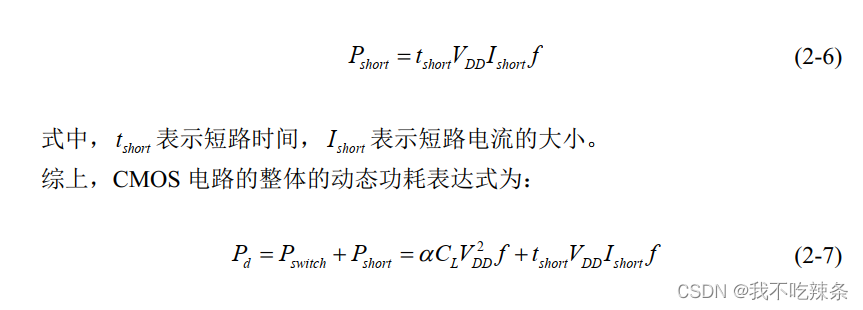

所以,对于电路的每一次开关变化,无论是由高电平变化为低电平还是由低电平变化位高电平,电路都会因为开关电流消耗固定为C V L DD 2 的能量。在芯片中,电路的开关活动并不是每时每刻都在进行,所以考虑到电路的开关活动性后,电路的开关功耗表示为式 2-5[27]:

式中, 阿尔法是电路开关活动因子,表示电路中一个信号发生跳变的概率, f 是电路工作的时钟频率[28]。

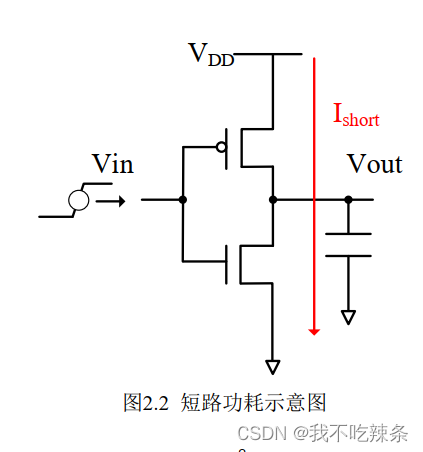

短路功耗是动态功耗的另一个组成部分[29]。CMOS 电路的晶体管是互补类型的,所以 PMOS 和 NMOS 处于相反的状态。在理想的信号切换过程中,信号转换时间为0,这种情况下 PMOS 和 NMOS 不会同时导通。但是在实际情况中,高低电平之间的转换过程需要一定的时间才能完成,在这个信号切换时间内由于输入信号电平变化到一个中间值, PMOS 管和 NMOS 管会出现同时导通的情况,产生一个瞬时的导通电流,这个电流被称为短路电流。 如图 2 所示短路电流为 Ishort ,这个电流产生了短路功耗,短路功耗的表达式如下:

2) 静态功耗

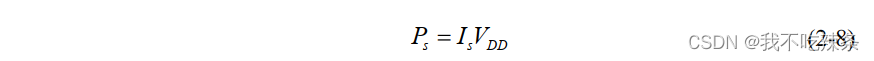

动态功耗是 CMOS 电路的开关活动产生的,相对地, CMOS 电路在状态不发生翻转的时候也存在着功耗, 被称为静态功耗。 由于器件结构以及制造工艺等因素的影响, CMOS 电路中在上电后就会产生漏电流,漏电流的存在导致了静态功耗的产生。漏电流的成因比较复杂, 一般和器件的工艺参数相关。静态功耗见表达式 2-8:

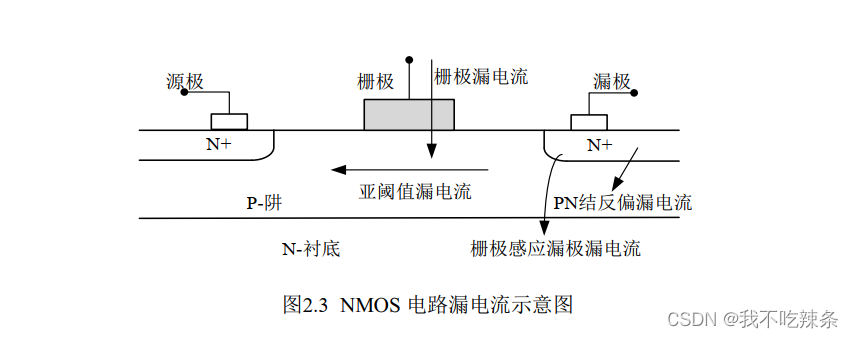

其中Is为漏电流, 漏电流是 CMOS 电路未工作时的电流, VDD 为供电电压[30]。CMOS 电路中的漏电流主要包括亚阈值漏电流,反偏 PN 结电流,多晶硅栅极漏电流,栅致漏极漏电流等[31]。 各种漏电流如图 2.3 所示(以 NMOS 管为例):

其中Is为漏电流, 漏电流是 CMOS 电路未工作时的电流, VDD 为供电电压[30]。CMOS 电路中的漏电流主要包括亚阈值漏电流,反偏 PN 结电流,多晶硅栅极漏电流,栅致漏极漏电流等[31]。 各种漏电流如图 2.3 所示(以 NMOS 管为例):

a) 亚阈值漏电流

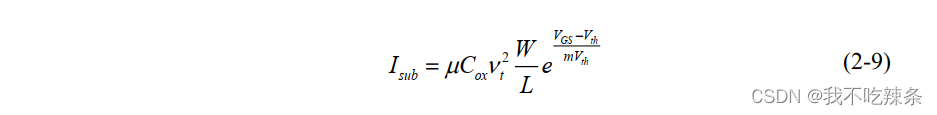

理想情况下, MOS 管是一个开关,对 MOS 管施加的栅压未达到器件阈值电压时被视为开关闭合,只要开关闭合就会完全关断电路,电路中就不会存在电流。但是比较遗憾的是,在实际情况中,由于亚阈值效应的存在,即使栅源电压未达到器件阈值电压,源漏也会形成通路。 因为亚阈值效应产生的微弱电流就是亚阈值漏电流,该电流的大小可以用下式计算[32]:

a) 栅漏电流

为了 MOS 器件小型化的需求以及增强 MOS 器件的栅控能力,器件栅氧化层会尽可能的减薄。较薄的栅氧化层使得氧化层中电场很大,高场强加上薄氧化层厚度会导致栅极发生隧穿效应产生栅漏电流,栅漏电流会从栅极流向沟道或者从沟道流向栅极[34]。 一般而言, 工艺节点越小,栅氧化层的厚度越薄, 产生的栅漏电流越大。在纳米工艺节点下, 人们普遍采用的抑制栅漏电流的方式是使用高K介质的栅氧化层[35]。

b) 栅致漏极漏电流

栅致漏极漏电流是场效应晶体管关闭状态下的电流。 当一个场效应管器件的栅极关闭但是漏极接高电压时,漏栅电压过大会导致漏极扩散层与栅极重叠的部分靠近界面处的能带发生弯曲,表面形成反型层, 此时由于耗尽层非常薄, 导带电子和价带空穴发生带带隧穿效应(Band-to-Band Tunneling, BTBT), 产生漏极流向衬底的电流[36]。

c) 反偏结漏电流

MOS 管的源漏和衬底之间会形成反向偏置的 PN 结,由于载流子的扩散效应或者隧道效应,反偏 PN 结会产生漏电流[37]。

功耗优化措施:

- 动态功耗优化

从动态功耗的表达式(2-7)可以很直观的看到,开关活动性、 负载电容、 电源供电电压以及时钟工作频率是动态功耗的决定要素。因此,优化动态功耗需要从这些方面入手。最为有效的措施是减小电路负载电容、 降低工作电源电压和工作时钟频率、减小电路翻转频率[38]。

在设计中,通过对总线编码技术调整、 使用门控时钟和操作数隔离等手段可以降低一些信号的开关活动性。电路的等效电容和晶体管尺寸关系密切,在工艺上,可以采用尺寸较小的晶体管来降低负载电容的大小。在物理设计中减小互连线的长度也可以减小电路的负载电容。

由动态功耗表达式(2-7)可以看出,功耗与时钟频率呈正比关系,与电源供电电压的二次方呈正比关系。因此,在对电路不进行任何改变的情况下,降低电源电压和时钟工作频率,能够大幅度的降低动态功耗。 由于供电电压的降低会导致电路的时序变差, 影响电路的性能,所以电源电压的调整需要综合考虑电路的功耗和性能,在合理范围内降低电源电压。电压的减小也不是无限制的减小,一般来说,供电电压不能小于阈值电压的二倍。 - 静态功耗优化

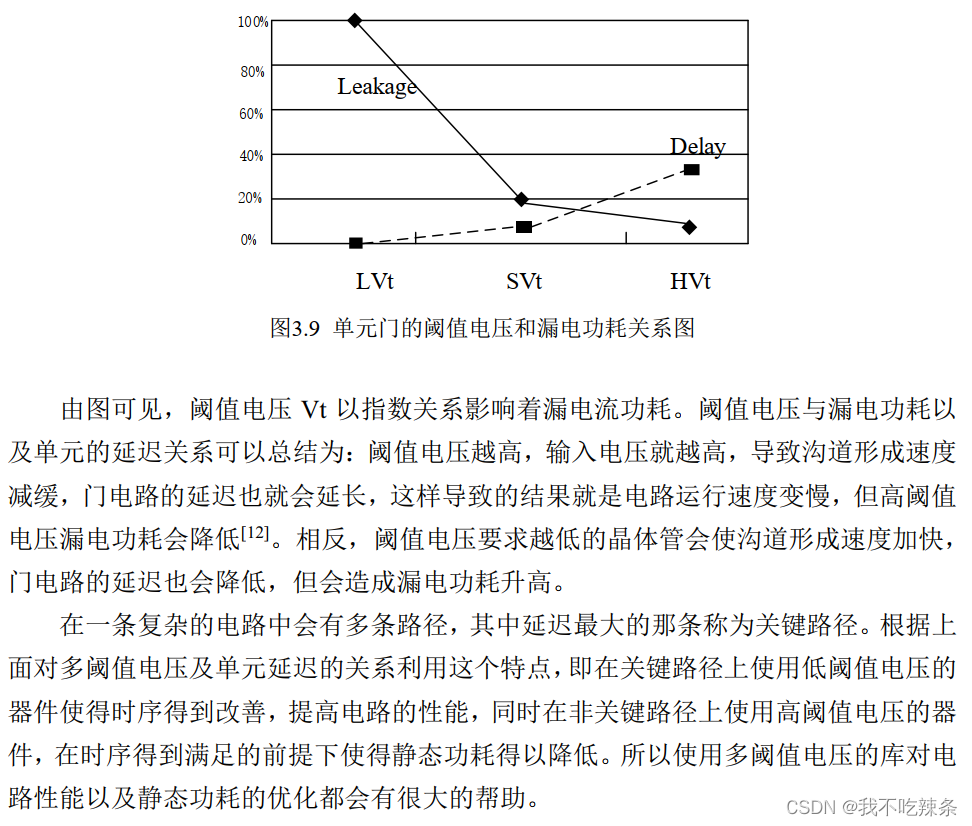

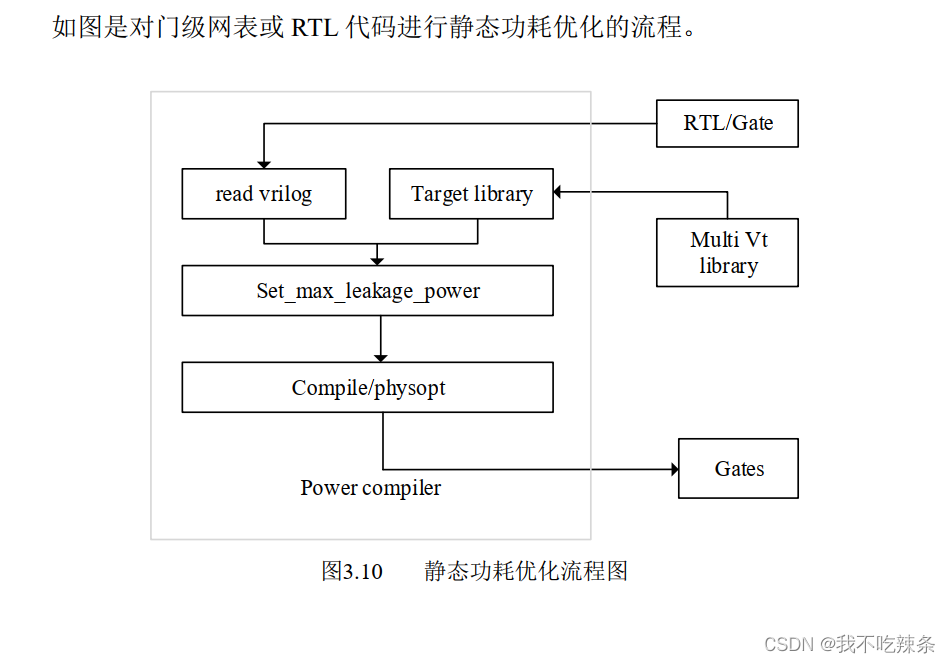

静态功耗和动态功耗的产生有着本质上的区别,因此优化静态功耗的方法和动态功耗不同。静态功耗是漏电流产生的功耗,漏电流的大小主要取决于工艺各方面的参数。考虑到电路内部的工作温度难以控制,优化静态功耗主要从控制晶体管的阈值电压和电源供给入手。在逻辑综合单元库的选择上, 不同阈值的晶体管有各自的特点,高阈值晶体管时序差漏电流小,低阈值晶体管时序好漏电流大。如果需要控制功耗, 选用高阈值的晶体管可以有效的减少漏电流,如果需要实现高性能,选用时序较好的低阈值晶体管可以减小电路延时。当系统中某个模块长时间的处于空闲状态,可以通过切断其电源供

给,降低该模块的静态功耗。

低功耗优化方法:

在低功耗设计中,一般在越高的层次上做优化,其优化的幅度越大。系统级的设计方法处于设计流程的金字塔顶端,在这一层次上动态功耗和静态功耗均可以得到有效的优化。 电路设计者在芯片设计流程中优先从系统层面入手,采用门控电源技术、动态电压频率调整技术(DFVS)、门控时钟技术和功耗管理技术(PM) 等多种低功耗技术。 接下来,将对这几种典型的低功耗技术进行详细的分析。

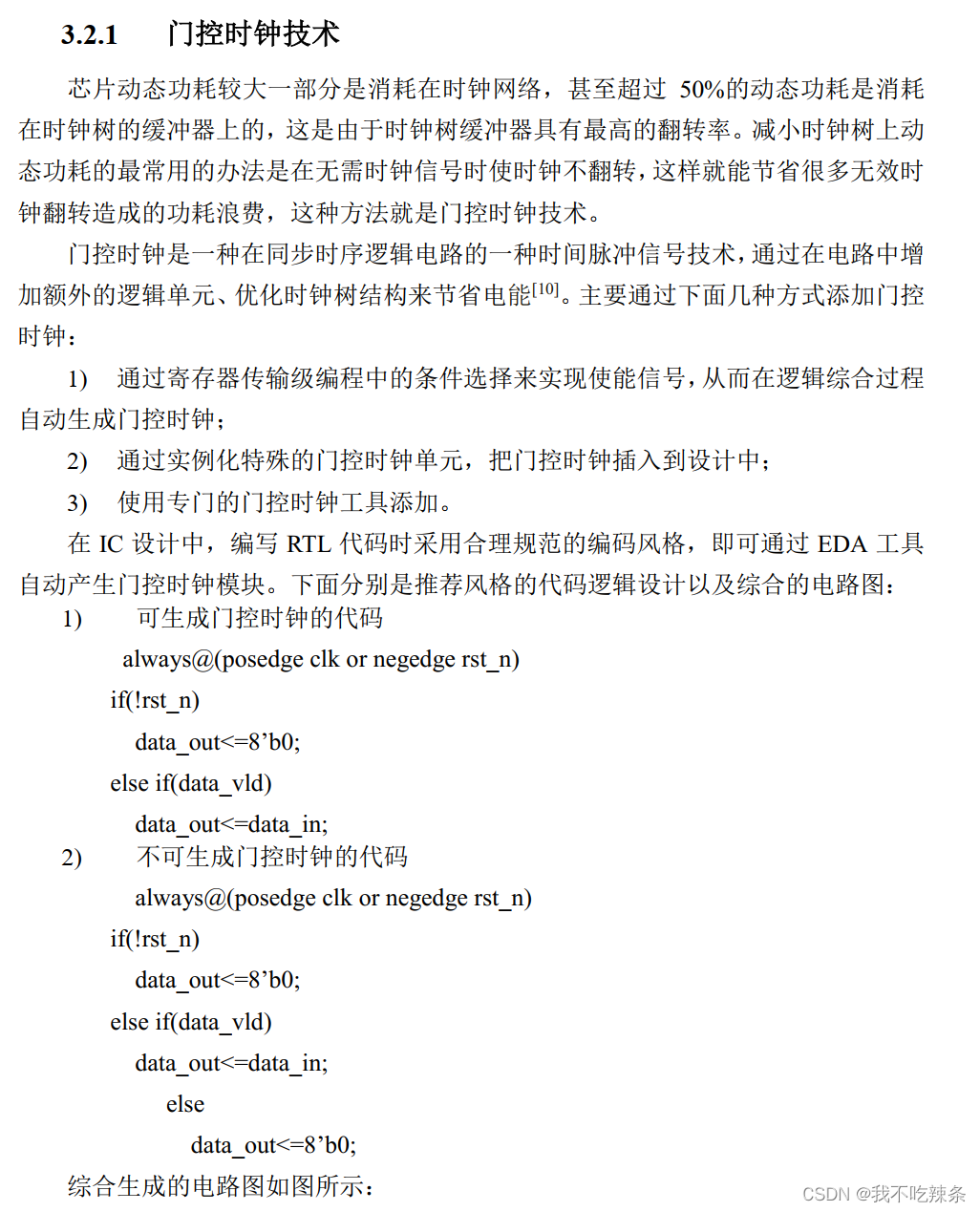

1) 门控时钟

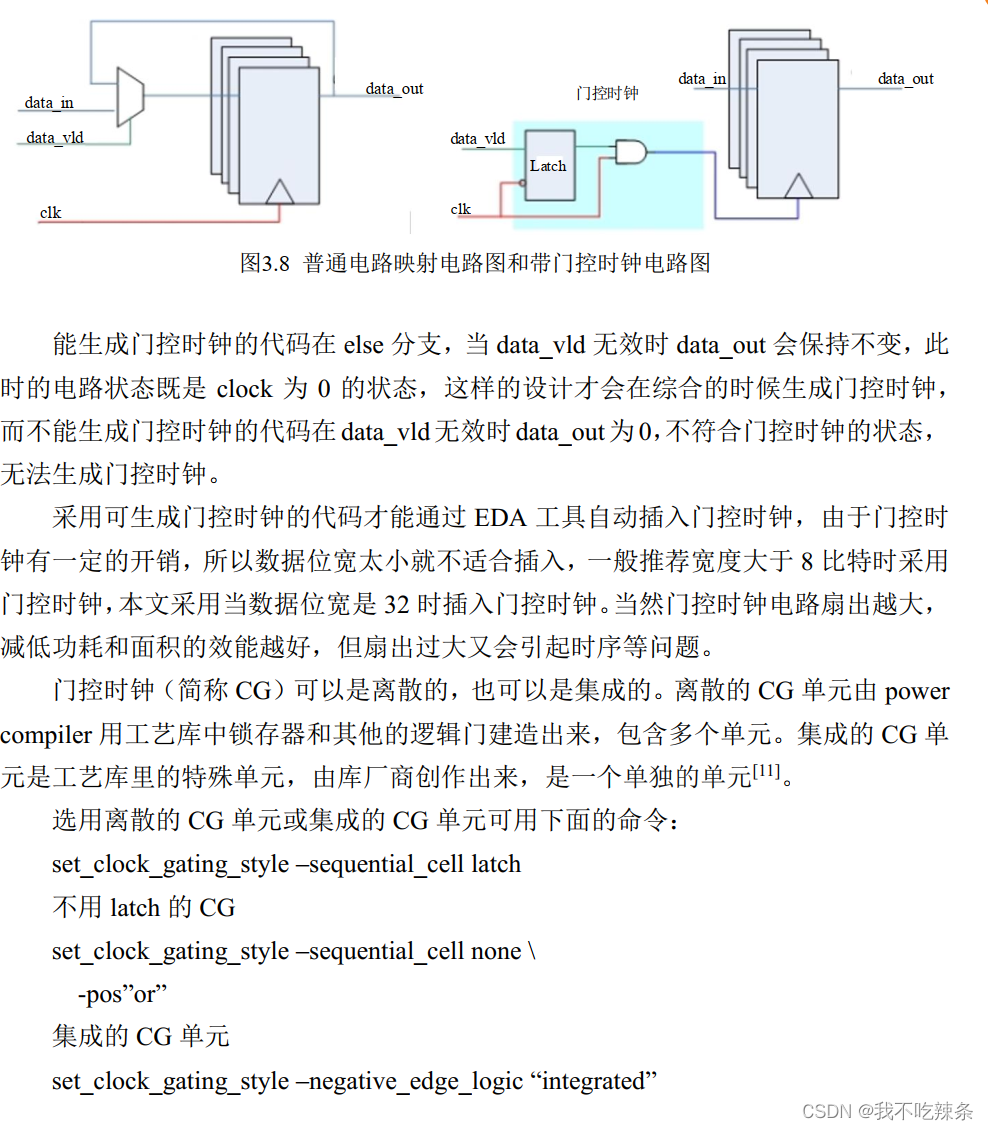

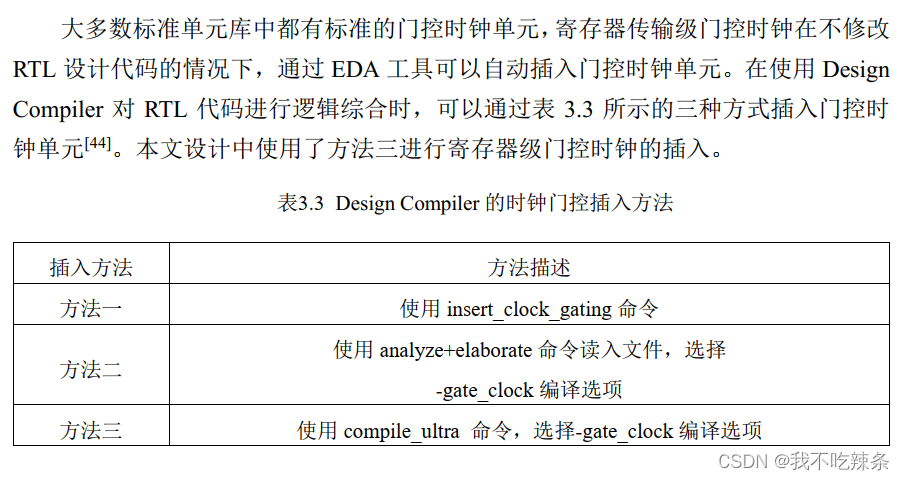

由前面一节对功耗原理的分析可以知道,芯片的动态功耗和信号的翻转速率成正相关。由于电路中每一个寄存器都需要时钟信号的驱动,时钟网络是整个芯片中最为密集的信号。 时钟信号的翻转频率非常高,在每一个周期都会翻转一次, 因此芯片的时钟网络产会生大量的动态功耗。系统在工作过程中, 即使某些单元处于空闲状态,时钟信号仍然会不断跳转。 虽然输入信号没有变化,时钟的跳转不会让这些空闲单元的输出发生改变,但是时钟信号对触发器不断充放电,内部的逻辑门仍然会产生动态功耗。门控时钟技术就是为时钟信号引入一个开关,在某一部分电路空闲的时候,关闭它的时钟从而节省这一部分动态功耗[39]。经过多年发展,门控时钟技术在应用上已经十分成熟,它作为最有效的低功耗方法在芯片设计中被广泛使用。门控时钟在实际应用中根据控制的寄存器数量不同,一

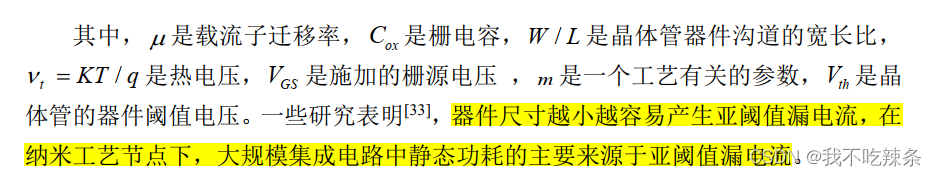

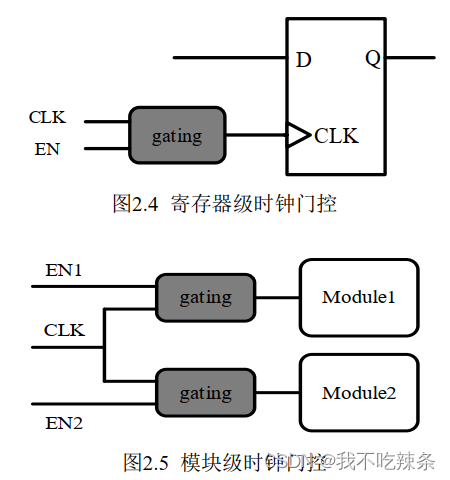

般分为寄存器传输级(RTL)和模块级时钟门控, 分别如图 2.4 和图 2.5 所示:寄存器传输级的时钟门控在寄存器的输出状态未发生改变时,不提供时钟,该级别的门控单元插入由自动化工具插入,不需要对设计进行改动。模块级的门控时钟由设计人员自主插入,电路中某个模块或者某几个功能模块处于空闲时,可以选择切断这些模块的时钟节省动态功耗。一般而言,门控单元距离时钟源越近,关断产生的功耗优化效果越明显。

2)多阈值电压设计

3)门控电源设计

时钟门控技术通过切断时钟供给,减少逻辑电路内部的无效反转,对芯片的动态功耗进行优化。门控电源技术在思想上与门控时钟是一致,电路工作过程中, 有些模块并不是一直都处于工作状态, 切断空闲上电区域的电源供给, 可以减少电路的静态功耗,达到优化静态功耗的目的。工艺节点进入到 65nm 以后,电路的静态功耗增长速度明显,很多电路中静态功耗已经达到了 mW 级别,这个数量级的静态功耗对于那些依靠电池供电的设备是不能接受的, 因此越来越多的设计采用了门控电源技术。

门控电源技术可以对静态功耗进行大幅优化,但是门控电源技术在实现上更为复杂,门控电源在实现过程中需要考虑很多问题。首先是对控制的电源区域进行划分,不同的电源区域可以独立的控制供电状态。这样一来在关断一些模块的电源时,不会影响其他电源区域的供电状态。其次,为了避免上下电操作错误对系统运行产生无法挽回的影响,电源区域的上电和下电过程需要遵守严格的顺序,在这个过种中需要添加门控电源控制器对上电和下电的过程进行控制。然后,门控电源的技术会涉及到低功耗特殊单元的插入。例如,当某一个模块空闲时,通过门控电源开关来关闭该区域的供电, 掉电区域会因为失去了电源驱动输出呈现未知的状态。如果这个不定态输出传递到了上电区域,会对上电的区域产生未知的影响,甚至可能导致严重的逻辑错误。因此,需要在掉电区域的输出信号端口插入隔离特殊单元,使断电后的输出钳制为一个明确的无效值。在部分系统中,模块需要在掉电后仍然保持数据,以便在重新上电以后能够恢复之前的运行状态,此时需要插入保持寄存器特殊单元来保存模块断电前的运行状态。最后,电源门控在后端实现时,需要考虑不同区域上电或者掉电过程的电压降造成的影响,较大的电压降会破坏芯片的功能和结构。

4)功耗管理技术

功耗管理是一种系统层级的低功耗设计方法,功耗管理的核心思想是避免功耗浪费,功耗管理通过对电路进行设计和划分,将芯片正常工作过程分为多个模式,在系统满足要求情况下,有选择的关闭那些暂时闲置的功能单元,让系统处于最小的负载状态。功耗管理通过门控时钟,门控电源等低功耗设计方法,调节系统性能和功耗之间的平衡。

功耗管理的方式一般分为两种,一种是动态的功耗管理方式,另一种是静态的功耗管理方式。动态功耗管理在系统运行时,通过调度系统使系统中非活跃的模块关闭或者减小它的性能等级来避免功耗浪费。静态功耗管理主要是对待机模式的系统进行管理,如果系统长时间工作在非活跃状态,那么可以认为系统在相当一段时间内没有任务执行。此时,可以通过关闭系统时钟或者电源的方式让芯片进入挂起状态,进入挂起状态后会很大程度的降低系统的动态和静态功耗。

功耗管理这种设计方法基于这样一个现实,那就是对一个系统而言,所有的模块并不是时刻都在被调用,系统的中一些单元在大部分运行时间内是不被需要的。系统管理的作用就是在满足系统功能需求的条件下,尽可能的使系统处于低功耗水平运行。

功耗管理涉及到多种工作模式的切换与唤醒,由于功耗模式的转换过程需要消耗额外的能量,功耗管理的本质也就变成了一个关于功耗约束的问题。例如系统进入低功耗模式时长过短就被唤醒,造成的结果可能是切换过程消耗的额外功耗会比进入低功耗模式节省的功耗更多,因此,合理的切换策略显得尤为重要。

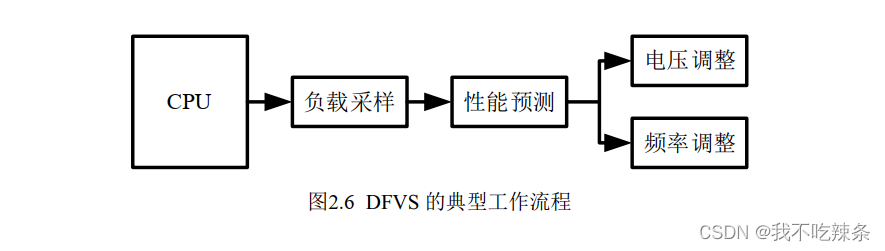

5)动态电压频率调整

动态电压频率调整技术是较为主流的能够提高系统能效比的低功耗技术。其核心思想是,在系统处于低负载状态下降低电路的时钟频率和供电电压,通过适当的牺牲性能大幅降低功耗。动态调整电压频率的基本流程如图 2.6 所示,系统的负载采样模块完成对负载信号的检测,通过监测结果判断目前的系统处于何种工作状态, 性能预测模块根据已有的监测结果,结合相关的预测算方法预测下一个阶段系统需要的性能。之后,性能等级请求被送到电压管理模块和时钟管理模块,性能请求会转换频率和电压。

在调整过程中有一个重要的问题需要注意,电路的供电电压和频率不是独立的工作条件,供电电压的变化会影响电路时序,降低供电电压会导致电路延时变大。 因此,电压和频率调整有明确的顺序。 当性能请求为降低性能时, 应该先降低电路的工作时钟频率,而后降低电路的供电电压。 当性能请求为提高性能时, 先提高电路的供电电压,再提高工作时钟频率。

398

398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?