学习第一步:安装tcl编译软件

点击这里进入activestate的官网,下载你喜欢的操作系统所需的安装包。这里我下载的是windows下的安装包。一步一步安装即可。

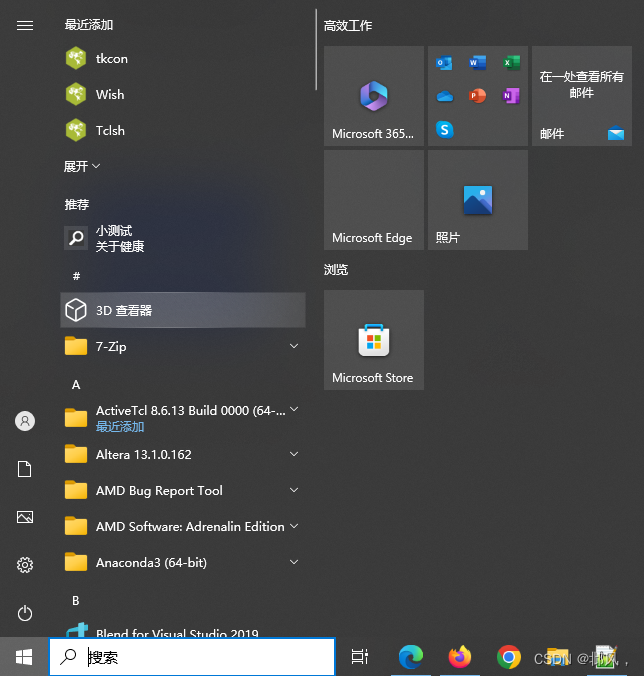

那么,安装后,我们可以在开始的菜单栏处看到三个应用程序。

那么,安装后,我们可以在开始的菜单栏处看到三个应用程序。

其中,wish(windowing shell)比tclsh多了TK的命令。tkcon同样可以运行TK的命令,而且可以将你写过的tcl命令保存为文件。具体的不同就要在今后的学习中自行发现啦。

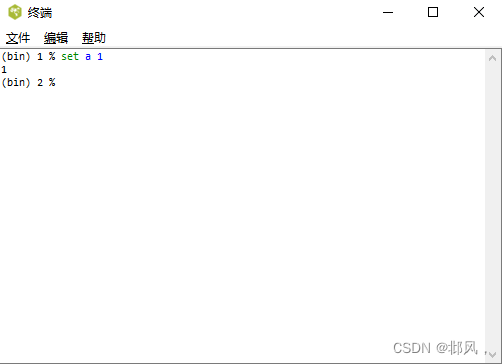

下面,我们在wish下,键入第一个tcl命令吧!

set a 1

这行代码的意思就是将a设置为1,显示结果如下:

推荐书籍:

TCL/TK入门经典(第2版),大家可以在网上找到这本书进行学习。

————————————————————分割线————————————————————

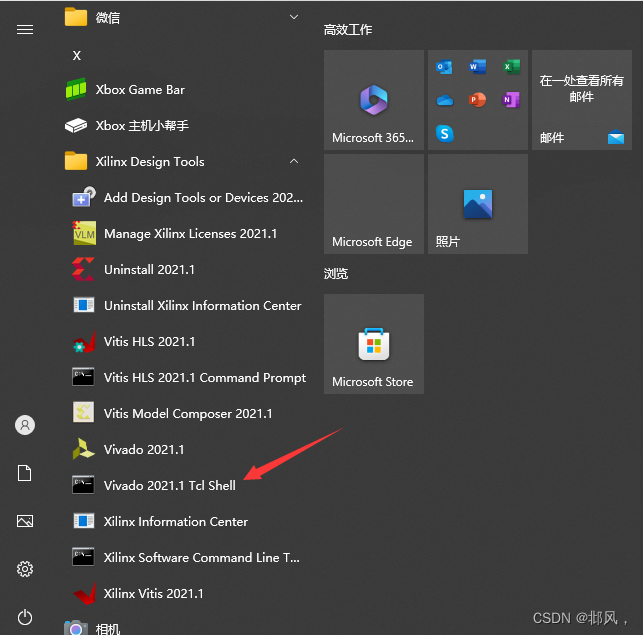

Vivado与TCL

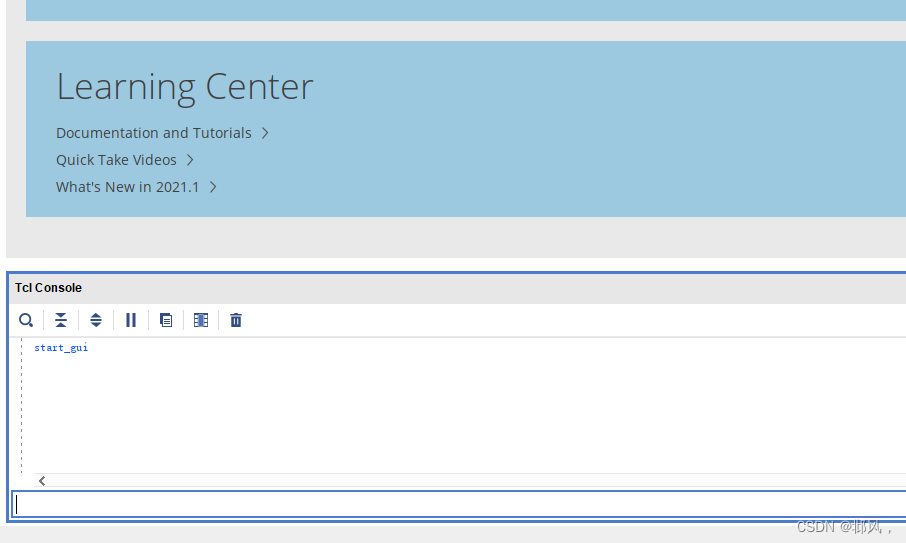

对于以及安装了Vivado的小伙伴,就不需要安装上述环境了,我们可以直接在Vivado的GUI界面上找到Tcl Console 或者在开始菜单栏上找到Vivado Tcl Shell即可。

附图!!

7796

7796

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?