Using FPGA-Based Parallel Flash Loader

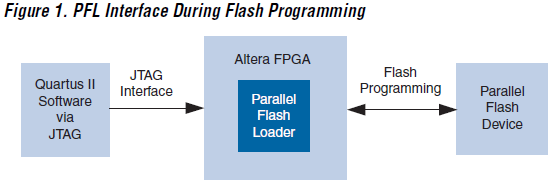

PFL: parallel flash loader

AP: active parallel

SOF: SRAM object file

POF: Programmer object file

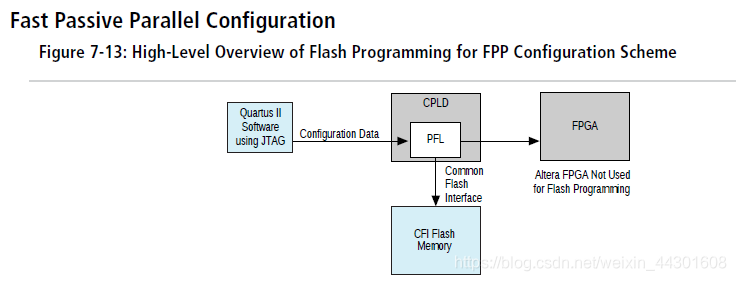

parallel flash具有更高的带宽与更大的容量,但是没有JTAG接口,所以不能直接由JTAG编程

FPGA-based PFL是FPGA内部的一个IP,用来对JTAG与parallel flash做桥接,使用户可以通过JTAG接口将bitstream写到flash中

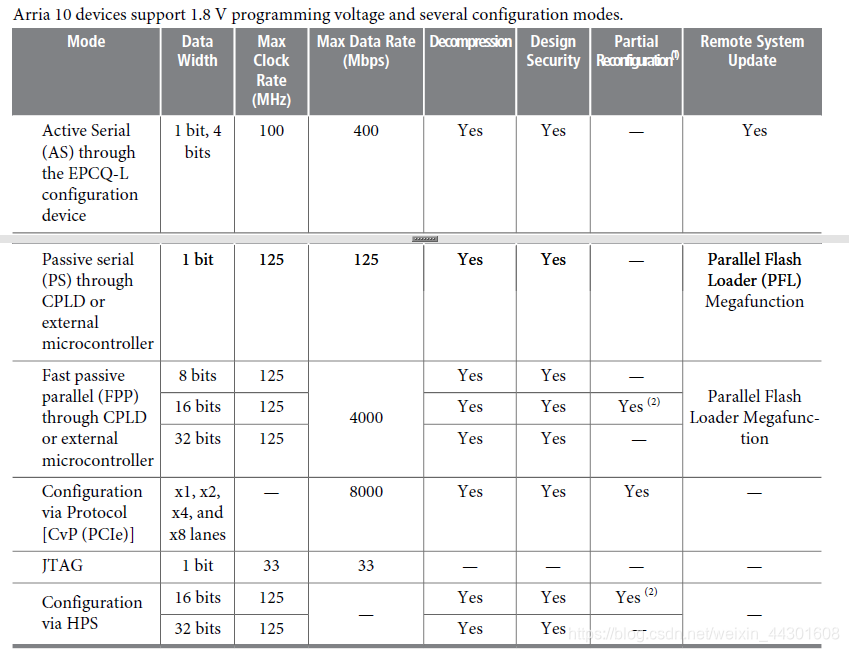

This scheme is the fastest method to configure Arria 10 devices

reference file: Configuration, Design Security, and Remote System Upgrades in Arria 10 Devices

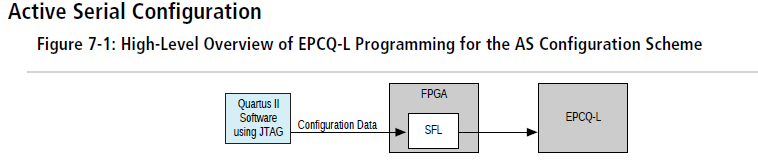

本文介绍使用FPGA-Based Parallel Flash Loader (PFL) 技术,该技术利用FPGA内部的IP实现JTAG与并行闪存之间的桥接,允许通过JTAG接口配置Arria10设备,这是目前最快的方法。并行闪存虽然没有JTAG接口,但其高带宽和大容量特性使其成为理想的存储解决方案。

本文介绍使用FPGA-Based Parallel Flash Loader (PFL) 技术,该技术利用FPGA内部的IP实现JTAG与并行闪存之间的桥接,允许通过JTAG接口配置Arria10设备,这是目前最快的方法。并行闪存虽然没有JTAG接口,但其高带宽和大容量特性使其成为理想的存储解决方案。

1148

1148

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?