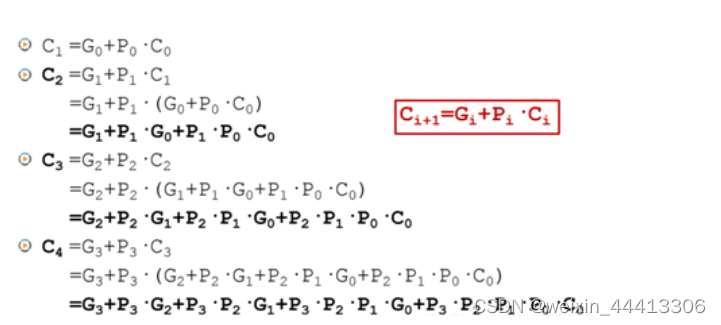

超前进位加法器公式如下所示:

Ci+1 = (Ai·Bi)+(Ai·Ci)+(Bi·Ci)=(Ai·Bi)+(Ai+Bi)·Ci;

设

Gi= (Ai·Bi)

Pi = (Ai+Bi)

则一级进位加法器公式为:

Ci+1= Gi + Pi·Ci

则 4级超前进位加法器各位可推出:

编写两个子模块 分别是一位加法器子模块 以及四级进位逻辑子模块

1、一位加法器子模块代码:

module Add1

(

input a,

input b,

input C_in,

output f,

output g,

output p

);

//f =c_in_1 g = a&b p = a|b

assign f = a^b^C_in;

assign g = a&b;

assign p = a|b;

endmodule

四级进位逻辑模块:

module CLA_4(

input [3:0]P,

input [3:0]G,

input C_in,

output [4:1]Ci,

output Gm,

output Pm

);

assign Ci[1]= G[0]|P[0]&C_in;

assign Ci[2] = G[1]|P[1]&G[0]|P[1]&P[0]&C_in;

assign Ci[3] = G[2]|P[2]&G[1]|P[2]&P[1]&G[0]|P[2]&P[1]&P[0]&C_in;

assign Ci[4] = G[3]|P[3]&G[2]|P[3]&P[2]&G[1]|P[3]&P[2]&P[1]&G[0]|P[3]&P[2]&P[1]&P[0]&C_in;

assign Gm=G[3]|P[3]&G[2]|P[3]&P[2]&G[1]|P[3]&P[2]&P[1]&G[0];

assign Pm=P[3]&P[2]&P[1]&P[0];

endmodule

第一步是CLA_4通过输入的数值,一次性算出四个加法器的进位。第二步,由于已经确定了每位的进位数值,ADD1分别例化四次,对四位同时进行加法。

顶层模块代码为:

`timescale 1ns/1ns

module 4jinwei//四位超前进位加法器

(

input wire [3:0]A,

input wire [3:0]B,

output wire [4:0]OUT

);

//**code//

wire [4:1] Ci;

wire [3:0] G;

wire [3:0] P;

wire [3:0] F;

Add1 u1

( .a(A[0]),

.b(B[0]),

.C_in(1'b0),

.f(F[0]),

.g(G[0]),

.p(P[0])

);

Add1 u2

( .a(A[1]),

.b(B[1]),

.C_in(Ci[1]),

.f(F[1]),

.g(G[1]),

.p(P[1])

);

Add1 u3

( .a(A[2]),

.b(B[2]),

.C_in(Ci[2]),

.f(F[2]),

.g(G[2]),

.p(P[2])

);

Add1 u4

( .a(A[3]),

.b(B[3]),

.C_in(Ci[3]),

.f(F[3]),

.g(G[3]),

.p(P[3])

);

CLA_4 uut

(

.P(P),

.G(G),

.C_in(1'b0),

.Ci(Ci)

);

assign OUT = {Ci[4],F};

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?