描述

请用Verilog设计十六进制递增计数器电路,每个时钟周期递增1。

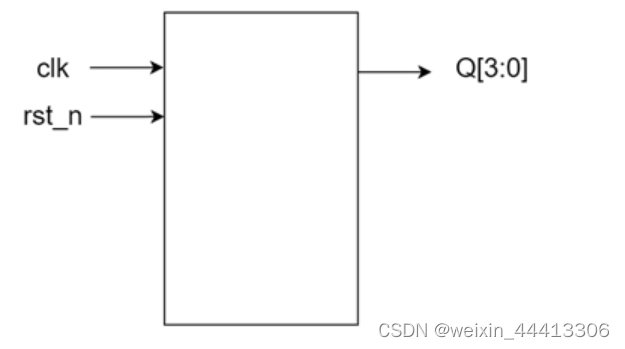

电路的接口如下图所示。Q[3:0]中,Q[3]是高位。

接口电路图如下:

代码如下:

题目的意思应该是设计一个四位十六进制计数器,从0000-1111-0000跳转。初始化后,Q[0]在时钟上升沿反转,其余位在前一位下降沿时翻转,代码如下:

`timescale 1ns/1ns

module counter_16(

input clk ,

input rst_n ,

output reg [3:0] Q

);

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

Q[0]<=0;

else

Q[0]<=~Q[0];

end

always@(negedge Q[0] or negedge rst_n)begin

if(!rst_n)

Q[1]<=0;

else

Q[1]<=~Q[1];

end

always@(negedge Q[1] or negedge rst_n)begin

if(!rst_n)

Q[2]<=0;

else

Q[2]<=~Q[2];

end

always@(negedge Q[2] or negedge rst_n)begin

if(!rst_n)

Q[3]<=0;

else

Q[3]<=~Q[3];

end

endmodule

本文介绍了如何使用Verilog语言设计一个四位十六进制计数器,计数器在每个时钟周期递增1。初始状态下,Q[0]在时钟上升沿反转,后续位在前一位下降沿时翻转。

本文介绍了如何使用Verilog语言设计一个四位十六进制计数器,计数器在每个时钟周期递增1。初始状态下,Q[0]在时钟上升沿反转,后续位在前一位下降沿时翻转。

1538

1538

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?