通过MATLAB,使用AD9361 Filter Design Wizard App设计Tx/Rx FIR滤波器,生成的.fir文件可以在 AD936x 配置软件(AD936x Evaluation Software) 2.5节 ,采用自定义Rx/Tx FIR 系数文件时使用

得到的.c文件可以用在 **AD9361 ADI官方例程( No-OS ) (未完成 )**中 ,在SW部分通过ad9361_set_rx_fir_config和ad9361_set_tx_fir_config 函数配置FIR

参考资料

一、安装

下载地址:AD9361 Filter Design Wizard App

该地址有MATLAB App安装程序(mlappinstall)和 压缩文件(zip或tarball)可以使用

该mlappinstall文件和平时安装 MATLAB APP 一样,安好后如下图所示,可以在MATLAB中的APP中打开

或者将.zip文件解压后,在MATLAB命令行运行命令“ AD9361_Filter_Wizard”

二、使用说明

2.1 Device Settings

我们可以自定义配置FIR滤波器,或者如果自己的需求和一些常规LTE应用配置类似,可以直接采用自带的LTE默认参数配置文件。

Store Filter Settings :可以将自己喜欢的参数设置保存起来,以后使用时所有参数将自动填充,不需要重新配置

Data :30.72 MHz 采样率

Clock 和 PLL:ADC、DAC时钟和PLL。根据数据采样率、滤波器的内插和抽取因子,可以确定ADC_CLK,进而确定DAC_CLK和PLL。可以与 AD936x 配置软件介绍 上 的2.4 采样率与带宽相互学习,加深理解。

- DAC_CLK可以设置为ADC_CLK,也可以设置为ADC_CLK/2。

- PLL Div :PLL = PLL Div * ADC_CLK

2.2 magnitude specification 幅度 和frequency specifications 频率

Apass :通带平坦度(通带衰减) 0.1dB

Astop :阻带衰减 80dB

Fpass :通带边界频率 9 MHz

Fstop :阻带边界频率 11 MHz

2.3 AD936x Decimation/Interpolation Rate 内插/抽取 速率

FIR : Rx/Tx FIR 滤波器 抽取或内插因子

HBs : 半带滤波器 抽取或内插因子

2.4 生成滤波器

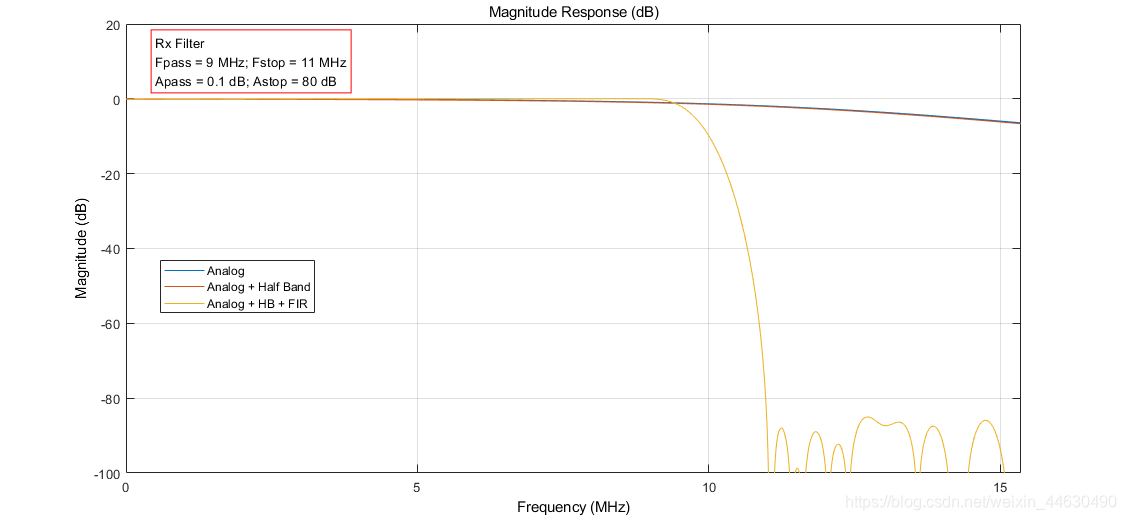

这些参数都设计好后,点击 Filter Design 中的 Design Filter设计滤波器 ,设计完成后,可以在GUI的上半部分看到滤波器的幅度谱,其中指定的Fpass、Fstop、Apass和Astop参数在图中突出以红线显示。

- 横轴是0到数据速率的一半。

在幅度谱下方的右侧,是“ Filter Results”部分,显示了实际的Apass,Astop,FIR抽头数和通带组延迟方差。从 Filter Results 可以看出,设计的该滤波器是否满足需求。

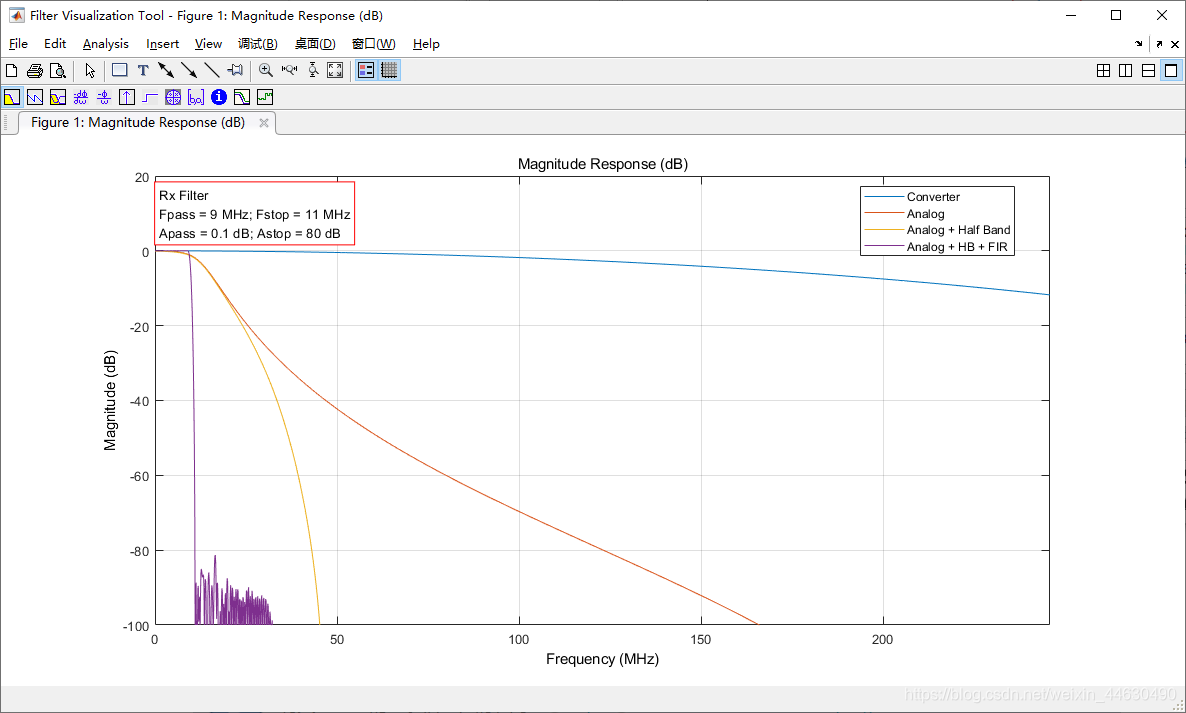

如果想知道滤波器的更多细节,可以点击“ FVTool to 15.36”或“FVTool ConverterRate/2”按钮,启动MathWorks提供的“滤波器可视化工具”(fvtool)。 APP在两个不同的频率范围内提供此工具:一个是从0 Hz到数据速率的一半“ FVTool to 15.36”,另一个是从0 Hz到转换器(A/D或D/A)速率的一半“ FVTool ConverterRate/2”。

2.4.1 FVTool to half of the data rate

如果主要对通带感兴趣,可以选“ FVTool to 15.36”按钮,可以看到以下三幅图:1)FIR滤波器的幅值响应 2)Analog+HB +设计的FIR滤波器的幅值响应 3)Group delay

除了幅值响应外,还可以使用左上角的工具栏(红色框内)查看其他响应,包括相位响应、群时延响应、脉冲响应、阶跃响应、极点/零点等。

1)FIR滤波器的幅值响应 。

2)Analog+HB +设计的FIR滤波器的幅值响应

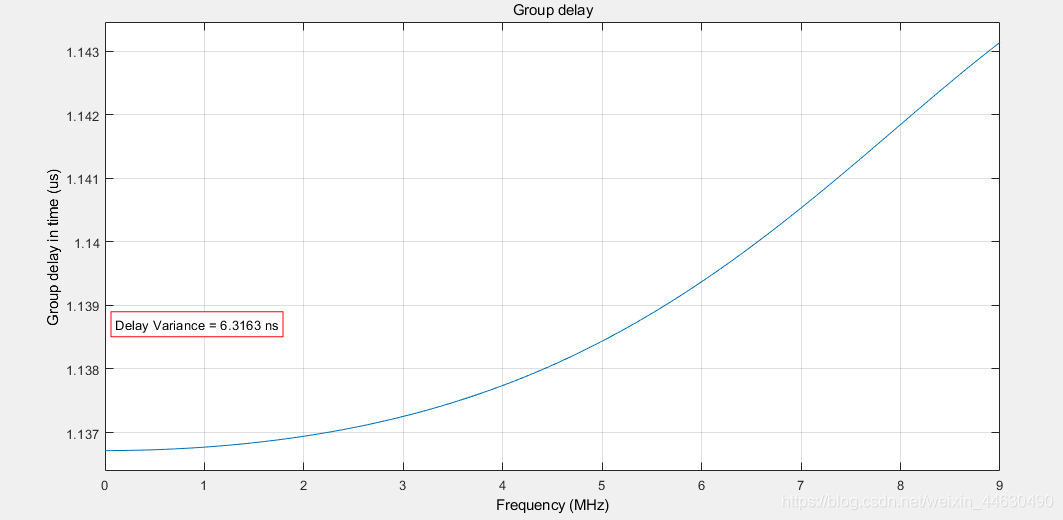

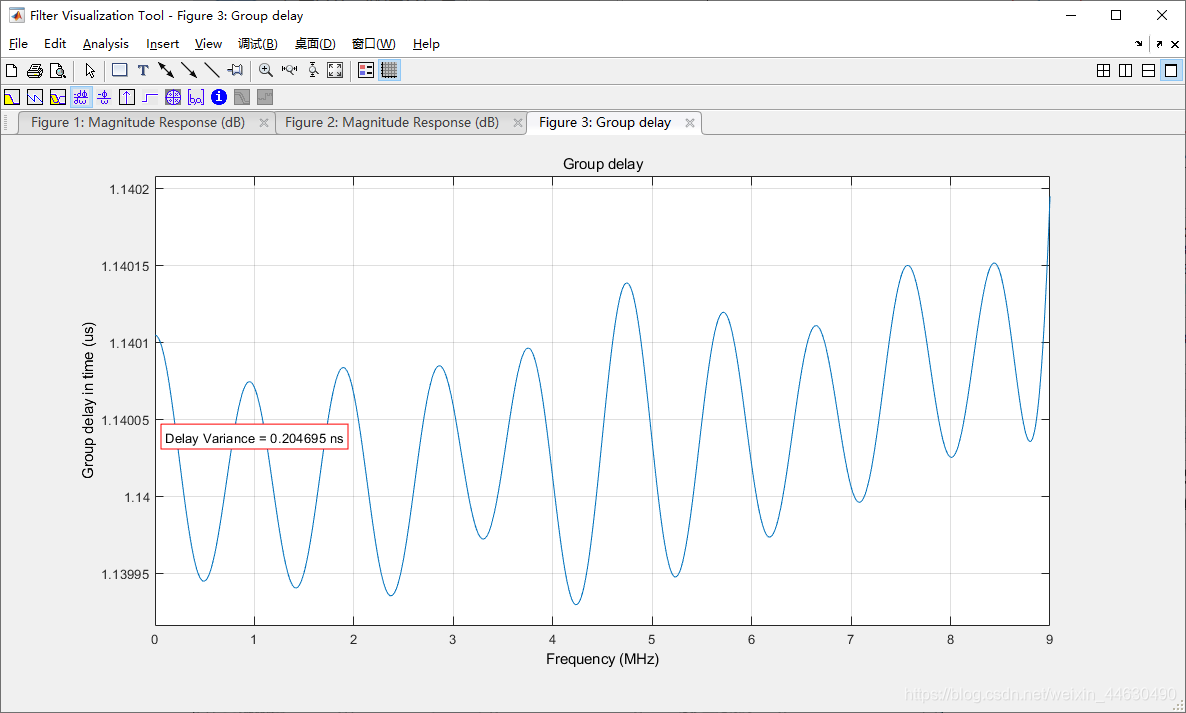

3)Group delay,已计算出群时延方差并在图中标出

2.4.2 FVTool ConverterRate/2

如果对整个频段感兴趣,可以选“FVTool ConverterRate/2”按钮,可以看到Analog+HB +设计的FIR滤波器的幅值响应

2.5 高级功能

如上图绿框所示,勾选Advanced后,APP提供了更多的高级选项。

Phase Equalization (相位均衡) :如果想让FIR滤波器进行相位均衡,可以勾选“相位均衡”选项。相位均衡的主要目的是减少由模拟滤波器、数字滤波器和FIR滤波器带来的通带群时延方差,以便对于不同频率的信号,它们在通过滤波器链时将延迟几乎相同的时间。

勾选Phase Equalization后,重新点击Design Filter,APP将执行FIR设计文件的相位均衡部分,从而得到更新的FIR滤波器设计。进行相位均衡后的 group delay如上图所示, 通过相位均衡 group delay variance 从6.3163ns 降到了 0.204695ns

- 由于相位均衡时APP会试图找到一个最优的 target delay(产生最小群时延方差),相位均衡过程可能要花费几分钟。

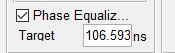

- 设计过程完成后,“Filter Options”部分会显示一个更新的Target delay (相位均衡之前该数字为0)

Astop (FIR) :它指定了FIR的衰减(不是复合响应),对应于设计文件中的“dBstop_FIR”输入。大多数情况下不需要此参数,可以将其保留为0。如果确实需要使用它,直接在那里输入所需参数。

- 如果想了解“dBstop_FIR”,可看Some Notes About dBstop_FIR这一节。

Fcutoff (Analog) :它指定了模拟巴特沃斯滤波器的截止频率。默认情况下,此参数由APP根据输入的Fpass和Fstop来计算,可以将计算结果保持原样。如果确实想使用它,可以直接输入所需参数。

HB1/HB2/HB3 :半带滤波器的内插或抽取因子

Use Internal FIR :某些情况下由于功耗的限制,可能不便使用AD936x上的FIR滤波器,而希望在FPGA上实现FIR滤波器,该APP也可以满足此要求。如果决定不使用AD936x 的FIR,不勾选“ Use Internal FIR”选项,如下图所示,然后点击“ Design Filter”。

- 不使用AD936x上的FIR滤波器时,FIR抽头的数量不再受任何限制,FIR将进行最小阶数设计。比较上图结果部分中的FIR抽头,如果不使用AD936x 内部的 FIR,抽头从128降低到108。

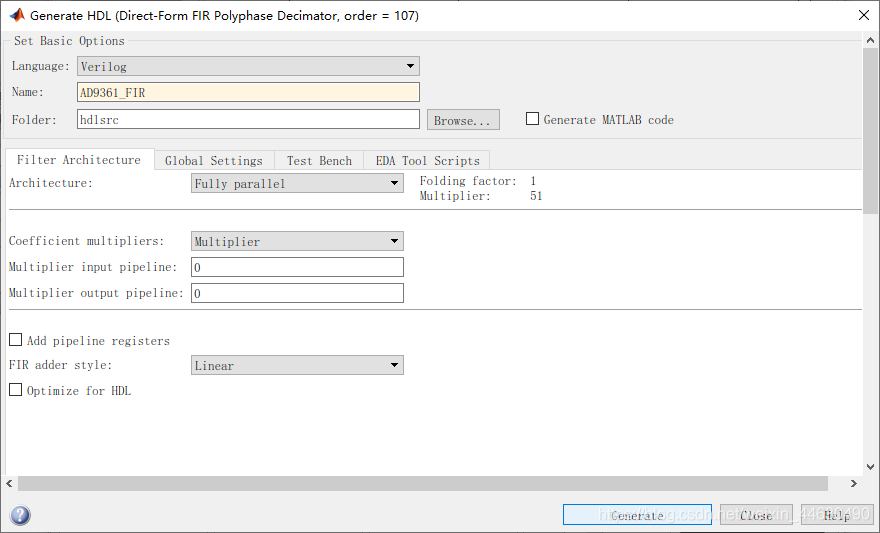

Generate HDL :不使用AD936x上的FIR滤波器时,当设计好FPGA使用的FIR后,会新增Generate HDL选项,APP可以生成HDL代码,点击“Generate HDL”,将调用“ fdhdltool”功能,弹出 Generate HDL对话框,如下图所示。配置好后点击“Generate”,生成HDL。

- 具体HDL生成方式的选项后续设计 脉冲成型滤波器(未完成) 中讲解。

三、保存和应用

如果APP生成的FIR滤波器符合需求,可以通过以下几种方式保存设计好的FIR滤波器。

3.1 Save to Workspace

将对象保存到工作区,后续可以将设计的滤波器链与其他一些MATLAB函数或Simulink模型一起使用,通过“Save to Workspace”按钮将其保存在工作区中。保存好且退出APP后,在MATLAB工作区可以找到名为“ AD9361_Tx_Filter_object”或“ AD9361_Rx_Filter_object”的mfilt.cascade对象。

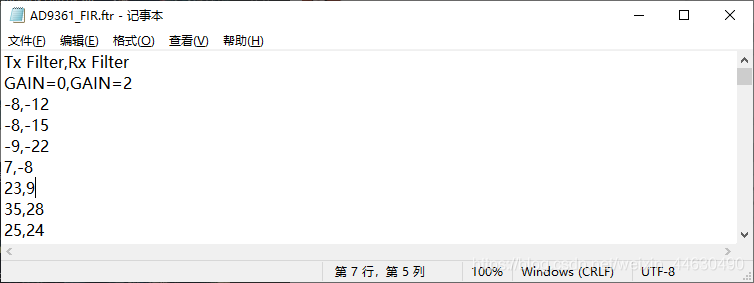

3.2 Coefficients to ftr File

将系数保存为ftr文件,可以在IIO示波器中使用此设计的FIR滤波器,通过“Coefficients to ftr File”按钮来保存FIR系数。需要先设计好Tx FIR 和 Rx FIR,然后才能使用该按钮,如果只设计了Rx FIR或Tx FIR ,此按钮是灰色,不能使用。

上图红色框中的含义一会在生成 .c 文件中讲解,红色框部分的内容可以替换成下述内容

Tx Filter,Rx Filter

GAIN=0,GAIN=2

得到的fir文件可以在 AD936x 配置软件(AD936x Evaluation Software) 2.5节 采用自定义RxFIR 系数文件时使用。

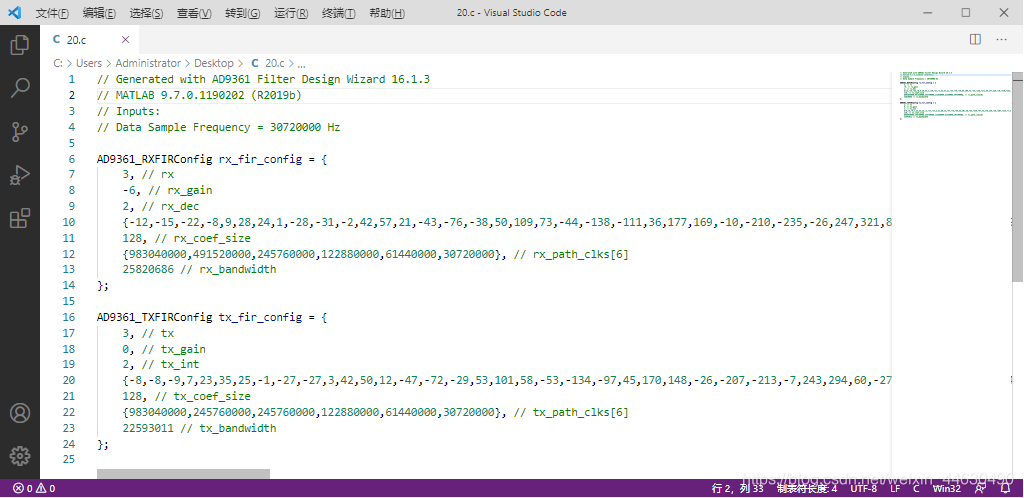

3.3 Coefficients to c File

保存为c文件,得到两个配置函数,文件具体内容如下,可以在 ADI 给的AD9361官方例程( No-OS )中,通过ad9361_set_rx_fir_config和ad9361_set_tx_fir_config 函数配置FIR。

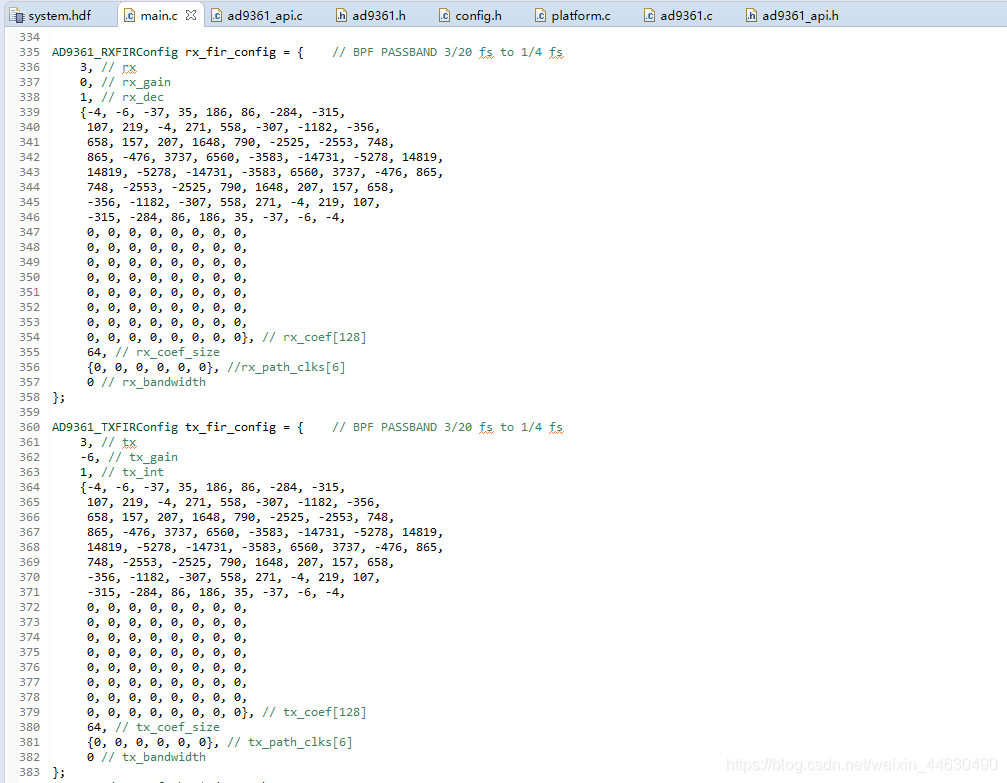

将 AD9361 Filter Design Wizard 生成的两个函数,替换到官方例程给出的配置滤波器函数(如下图所示)

进而可以通过zynq中的arm将滤波器系数写到AD9361中

下面讲解一下APP生成的函数各部分含义,Tx类似

AD9361_RXFIRConfig rx_fir_config = {

3, // rx

-6, // rx_gain

2, // rx_dec

{-12,-15,-22,-8,9,28,24,1,-28,-31,-2,42,57,21,-43,-76,-38,50,109,73,-44,-138,-111,36,177,169,-10,-210,-235,-26,247,321,86,-273,-419,-167,294,538,283,-297,-673,-434,280,832,641,-228,-1016,-916,130,1239,1302,48,-1522,-1873,-362,1926,2834,986,-2643,-4912,-2652,4728,14235,20875,20875,14235,4728,-2652,-4912,-2643,986,2834,1926,-362,-1873,-1522,48,1302,1239,130,-916,-1016,-228,641,832,280,-434,-673,-297,283,538,294,-167,-419,-273,86,321,247,-26,-235,-210,-10,169,177,36,-111,-138,-44,73,109,50,-38,-76,-43,21,57,42,-2,-31,-28,1,24,28,9,-8,-22,-15,-12}, // rx_coef[128]

128, // rx_coef_size

{983040000,491520000,245760000,122880000,61440000,30720000}, // rx_path_clks[6]

25820686 // rx_bandwidth

};

rx : 可以为 1、2或3,1 配置Rx1通道滤波器 ,2 配置Rx2通道滤波器,3 配置Rx1和Rx2通道滤波器

rx_gain :Rx FIR具有−12 dB,−6 dB, 0 dB,或+6 dB的可编程增益

rx_dec : Rx FIR 滤波器抽取系数,1,2,4 可选

rx_coef[128] : 滤波器系数

rx_coef_size : 抽头数

rx_path_clks[6] : 接收路径时钟,依次为 PLL、HB3(ADC)、HB2、HB1、FIR、Data 速率

rx_bandwidth : Rx 带宽 ,与模拟LPF有关

687

687

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?