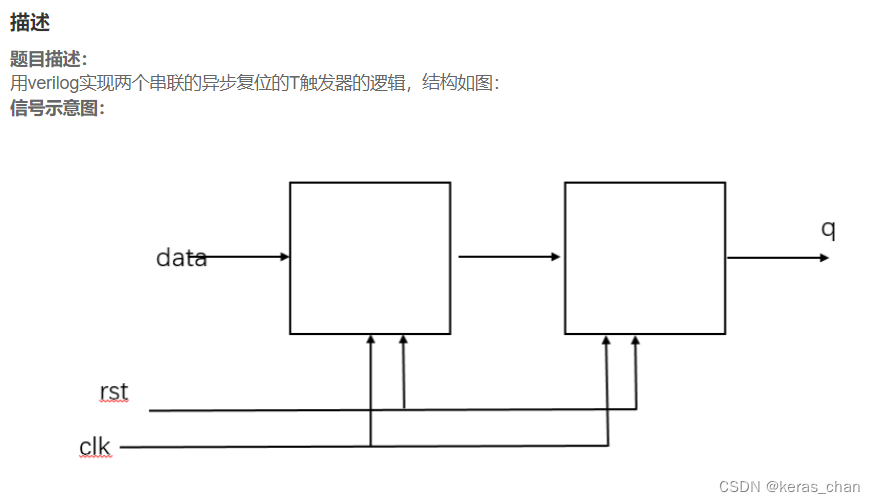

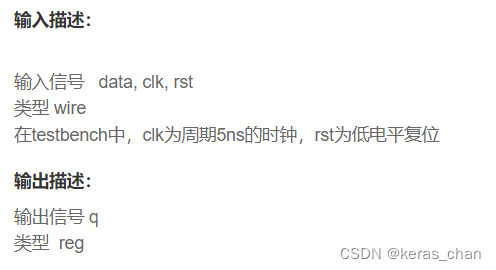

题目:异步复位的串联T触发器

原理介绍:

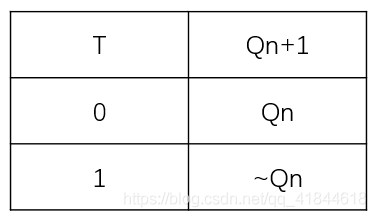

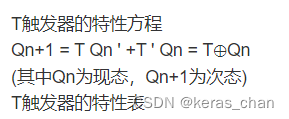

T触发器是一种边沿敏感的存储单元。只有一个信号输入端T,在时钟有效边沿到来时,T端输入有效信号,则触发器翻转,否则触发器保持不变。因此T触发器能够实现有效的计数功能,常用于实现数字计数器。T触发器逻辑功能为:当T=0时,触发器状态不变Qn+1=Qn;而当T=1时,在脉冲有效边沿到来时翻转。触发器的特性表如表所示:

使用verilog实现单个T触发器

module t(clk,rst,T,Q);

input clk,rst,T;

output Q;

reg Q;

always@(posedge clk or posedge rst)

begin

if (rst==1'b1) Q<=1'b0;

else if (T==1'b1) Q=~Q;

else Q=Q;

end

endmodule 同步、异步与置位、复位的概念

置位就是通过外部强制改变输入,从而把输入映射到输出的一种方式;

复位就是通过程序把输入的值变为通电时候的初始状态。

在功能上,置位就是使得输出为1,复位就是使得输出为0。比如开始没有输出,置位后输出1,再复位后就又变为0了。

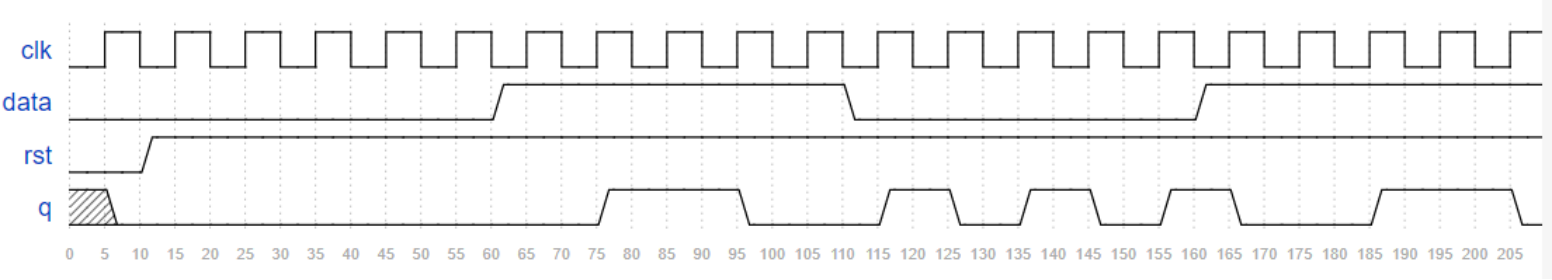

异步复位,指的是复位信号到来,所有寄存器输出清零。

T触发器的功能,是当T=1时,寄存器输出=计数状态;当T=0时,寄存器输出=保持状态。

特征方程:Qn+1 * = T Qn ' +T ' Qn=T⊕Qn;

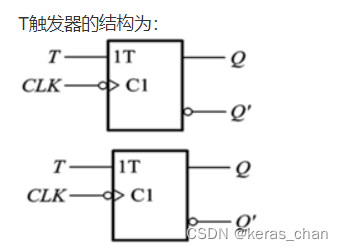

根据特征方程可知,T触发器可用D触发器实现其功能;

两个电路为串联,是指前一级的输出是后一级的输入。

寄存器输出的功能实现,采用时钟同步实现,所以时钟clk统一接到寄存器的时钟脉冲端。

在于使用信号rst的下降沿,作为always的触发,这样,无论时钟clk处于何种状态,都会对输出q进行置位操作(即:不管你clk是不是上升沿都可以进行置位操作),即:异步置位

always @ (posedge clk or negedge rst)

仅由clk上升沿事件作为always的触发,所以复位动作,需要与clk同步才能完成,即:同步复位;

always @ (posedge clk)

同理:异步复位与异步复位 只在if(!rst) q1 <= 1'b0;处不同

always @ (posedge clk or negedge reset ) always的触发方式相同

方法1:

T触发器可用一个异或门和一个D触发器来实现其功能。

reg data_1;

always @(posedge clk or negedge rst) begin

if(!rst)

data_1 <=1'b0;

else

data_1<=data^data_1;

end

always@(posedge clk or negedge rst) begin

if(!rst)

q<=1'b0;

else

q<=data_1^q;

end

方法2:

添加选择条件,如果数据选择是1,则寄存器计数,否则保持。

reg q1;

always@(posedge clk or negedge rst)

if(~rst) begin

q1<=1'b0;

q<=1'b0;

end

else begin

if(data)begin //对应的映射电路中就是选择器CE。

q1<=!q1;

end

if(q1) begin

q<=!q;

end

end

393

393

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?