前言

不知道大家有没有一个疑惑,为什么两级同步电路结构能够解决亚稳态问题,之前一直疑惑的地方在于,当第一级DFF发生亚稳态时,他的输出呈现不确定性,会出现0或者1任意一个值。若输入是1,第一级DFF亚稳态之后稳定到了0,那么第二级采样的话不就错了吗?这个问题困扰了很久,现在终于解决了,无非就是同步后的有效信号会延时1拍还是2拍的问题。

单比特CDC

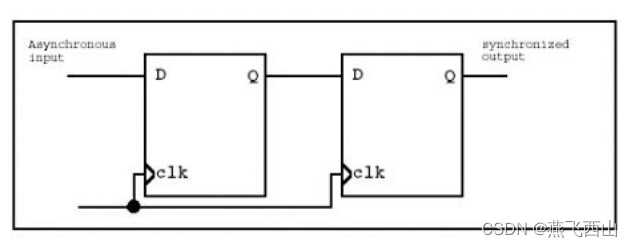

对于单比特信号在两个时钟之间传递时,一般都会使用两级DFF的电路结构来避免产生亚稳态。以前遇到这种问题都是无脑使用这种同步器,对其为什么能避免亚稳态和它的使用条件从没有考虑过,这不对呀,所谓学东西要学个明白,这次咱就来深入探究下~~

首先来了解下什么是亚稳态:

每个DFF都有一个由建立时间和保持时间定义的时间窗口,在这个窗口内,输入数据不能变化,如果输入数据在这个窗口内变化,就会引起输出端口的值的不确定性。也就是说它,它是稳定到高电平还是低电平这不好说。但是经过一段时间后输出端口最终会稳定到一个确定的值,这段时间会比正常的Tck->q大。(ps:有的文章说亚稳态之后DFF也可能一直输出震荡状态)

为什么会出现亚稳态:

在两个时钟的交界面上,由于外部数据到本地输入端口的稳定时间与本地触发器的采样窗口在时序上没有必然联系,因此会造成跨时钟域接口间的亚稳态问题。当一个信号跨越某个时钟域时,对新的时钟域来说这就是个异步信号,这时就需要特殊的电路结构把这个异步信号同步到新的时钟域。这种电路结构就是两级DFF电平同步器。

对于同步电路来说,它必须保证同步后数据(事件)的值,个数,顺序不能错,且同步后不会再出现亚稳态(亚稳态不可能完全避免)

两级电平同步器的使用是有要求的,它要求异步输入信号在新时钟域中至少稳定两个时钟周期(ps:一个时钟周期+set_up+hold time)。此外,在信号再次有效之前要先变成无效状态,每一次信号有效时接收逻辑会把它看作单一事件,不管它持续了多长时间。那么回答开始的问题,为什么两级DFF能避免亚稳态?当第一级触发器出现亚稳态时,它经过一定的时间恢复到稳定状态,再经过组合逻辑和走线延迟到达下一级触发器,假设总的延迟是4ns,那么若此时时钟周期大于4ns+第二级DFF的set up time,则第二级触发器就不会再出现亚稳态。

Q1: 为什么同步器之间不能插入组合逻辑?

Q2: 为什么同步器之前不能插入组合逻辑?

Q3: 为什么同步器之后可以添加组合逻辑了?

Q4: 如何约束?一个set_false_path就够了吗?

几个问题可以考虑一下

多比特CDC

对于多比特CDC问题,一般采用握手信号或FIFO的方式。那么问题来了,为什么多比特信号不能用两级DFF同步?这些后续文章会详细说明。

文章探讨了亚稳态现象在数字电路中的影响,以及两级DFF同步电路如何解决这一问题。同步电路的目标是确保数据在不同时钟域间正确传输,避免亚稳态导致的不确定性。两级DFF结构通过确保输入在新时钟域内稳定至少两个周期来防止亚稳态。同时,文章提出了同步器前后组合逻辑的使用限制,并提及多比特信号的同步通常需要握手信号或FIFO。

文章探讨了亚稳态现象在数字电路中的影响,以及两级DFF同步电路如何解决这一问题。同步电路的目标是确保数据在不同时钟域间正确传输,避免亚稳态导致的不确定性。两级DFF结构通过确保输入在新时钟域内稳定至少两个周期来防止亚稳态。同时,文章提出了同步器前后组合逻辑的使用限制,并提及多比特信号的同步通常需要握手信号或FIFO。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?