1. 利用Matlab生成滤波器系数COE文件

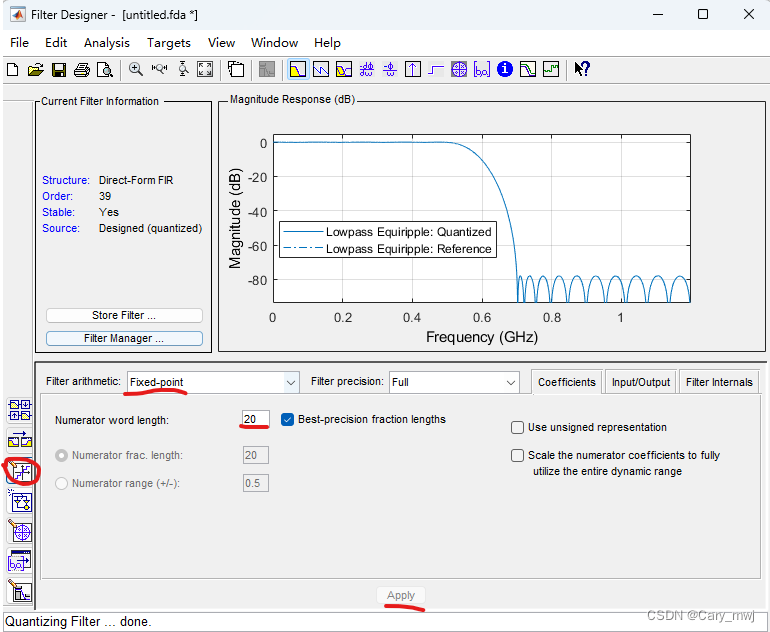

1.1 利用Maltab的filterDesigner命令,打开滤波器设计界面,设置滤波器参数

在数字下变频中,一般先抽样再滤波,除了滤除杂散信号,FIR还实现抗混叠,即过滤抽样后折叠回来的镜像频率。因此通道和阻带的设置很重要,要保证信号带宽和滤除折叠频率,也要使滤波器阶数不能太大(消耗更多乘法器资源)。

1.2 设置定点位宽

在FPGA内部一般采用定点数运算。

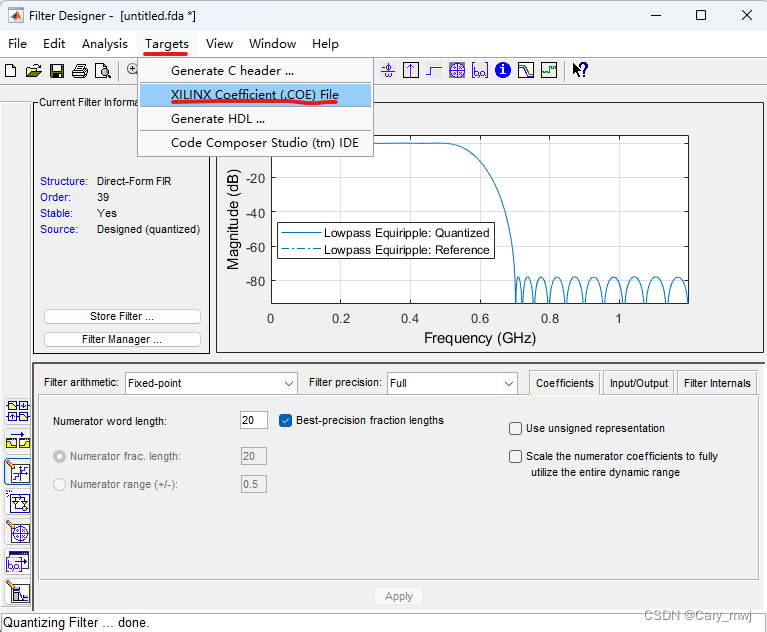

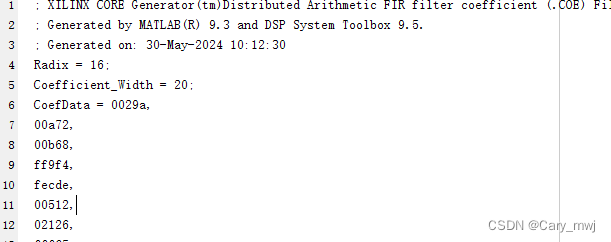

1.3 输出格式为COE文件

此时输出的系数有20bit的增益,即滤波后,信号幅度增大2^20倍。

注意:为了方便区分,COE文件的命名一般采用fs_fpass_fstop_d的格式,例:fs2400m_fpass500m_fstop700m_d2.coe,d2指2倍抽取。

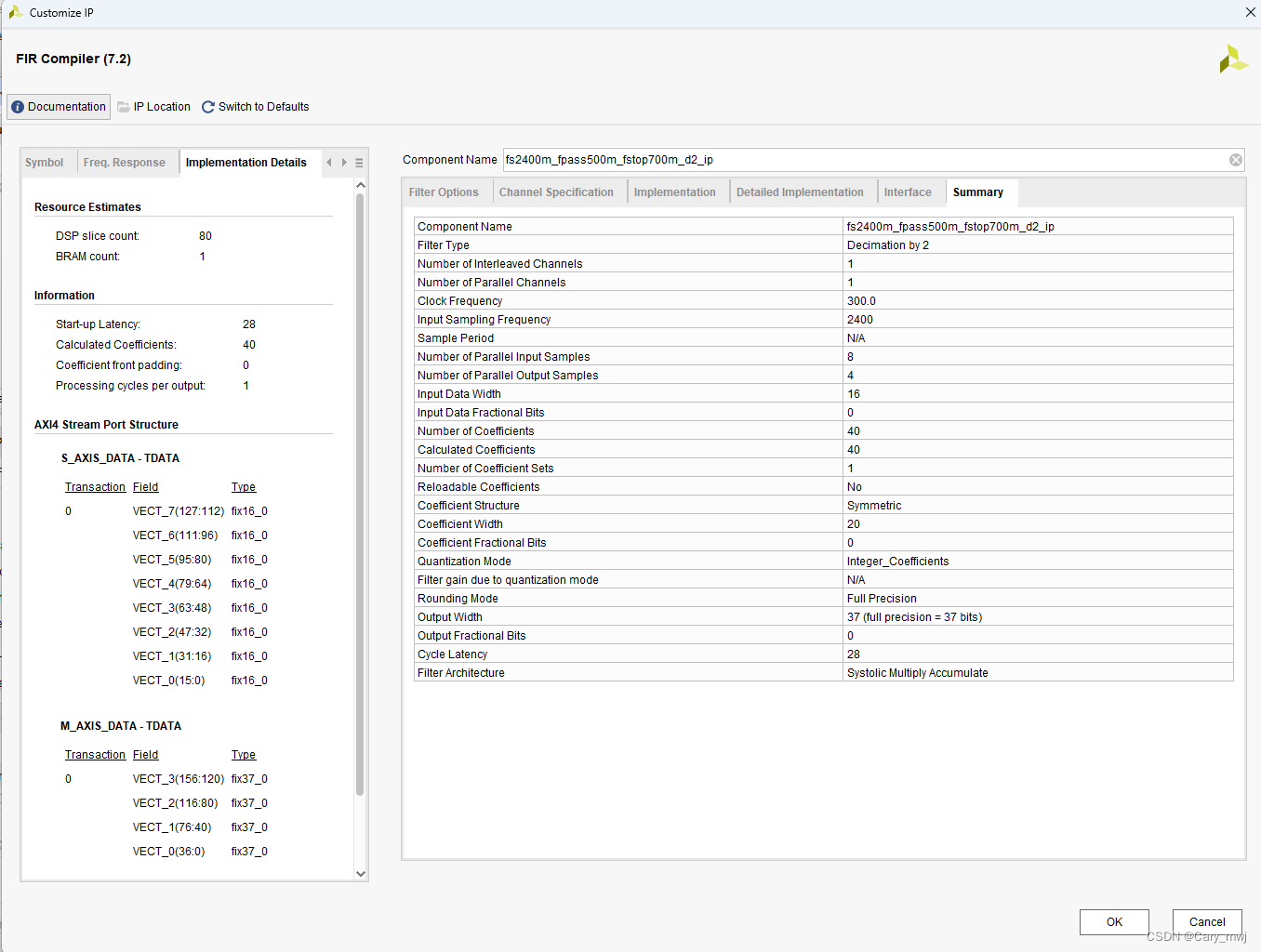

2. FIR IP核设置

首先将COE文件导入IP核,其次设置抽取倍数、输入采样率、系统时钟、位宽、对称结构等参数。

这里采用2.4G采样率的滤波器,实现了2倍抽取,即输出采样率为1.2G;系统时钟为300M,因此输入为8路并行,输出为4路并行。

注:IP核命名一般也采用与COE相同的名字。

3. 滤波器输出与截位

根据第2节设置,输入数据位宽为16bit,滤波器系数为20bit,输出为37bit(输出扩位是防止计算结果溢出),为了减小数据传输带宽,一般对输出结果进行截位处理。

前文提到滤波器对信号幅度有2^20倍的增益,为了保证滤波器的0增益效果,也需要对滤波器输出进行截位处理。

假设输出截取bit[34:19],即对滤波器输出除以2^19,算上系数增益,截位结果仍有2倍增益;此时需要提前将滤波器系数进行降增益处理,使其增益变为2^19倍。

对于如何截位,应该根据实际的输入信号幅度大小决定,保证截位后信号不溢出。

4729

4729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?