FPGA 数码管+超声波测距+UART

`timescale 1 ps/ 1 ps

module dis_top(

input clk,

input rst_n,

input echo,

output [3:0] seg_sel , // 数码管位选信号

output [7:0] seg_led, // 数码管段选信号

output trig,

output tx

);

wire tx_trigger;

wire [7:0] top_data;

ultrasonic u1(

.clk (clk),

.rst_n (rst_n),

.echo (echo),

.trig (trig),

.tx_trigger (tx_trigger),

.data (top_data)

);

uart_tx u2(

.clk (clk),

.rst_n (rst_n),

.tx_trigger (tx_trigger),

.tx_data (top_data),

.tx (tx)

);

//wire define

(*keep*) wire [7:0] uart_data; //UART发送数据

wire [7:0] data; // 数码管显示的数值

wire [ 5:0] point; // 数码管小数点的位置

wire en; // 数码管显示使能信号

wire sign; // 数码管显示数据的符号位

//计数器模块,产生数码管需要显示的数据

count u_count(

.clk (clk ), // 时钟信号

.rst_n (rst_n), // 复位信号

.uart_data (top_data),//uart_data

.data (data ), // 6位数码管要显示的数值

.point (point ), // 小数点具体显示的位置,高电平有效

.en (en ), // 数码管使能信号

.sign (sign ) // 符号位

);

//数码管动态显示模块

seg_led u_seg_led(

.clk (clk ), // 时钟信号

.rst_n (rst_n), // 复位信号

.data12 (data +20'd13 ), // 显示的数值

// .data34 (data ), // 显示的数值

.point (point ), // 小数点具体显示的位置,高电平有效

.en (en ), // 数码管使能信号

.sign (sign ), // 符号位,高电平显示负号(-)

.seg_sel (seg_sel ), // 位选

.seg_led (seg_led ) // 段选

);

endmodule

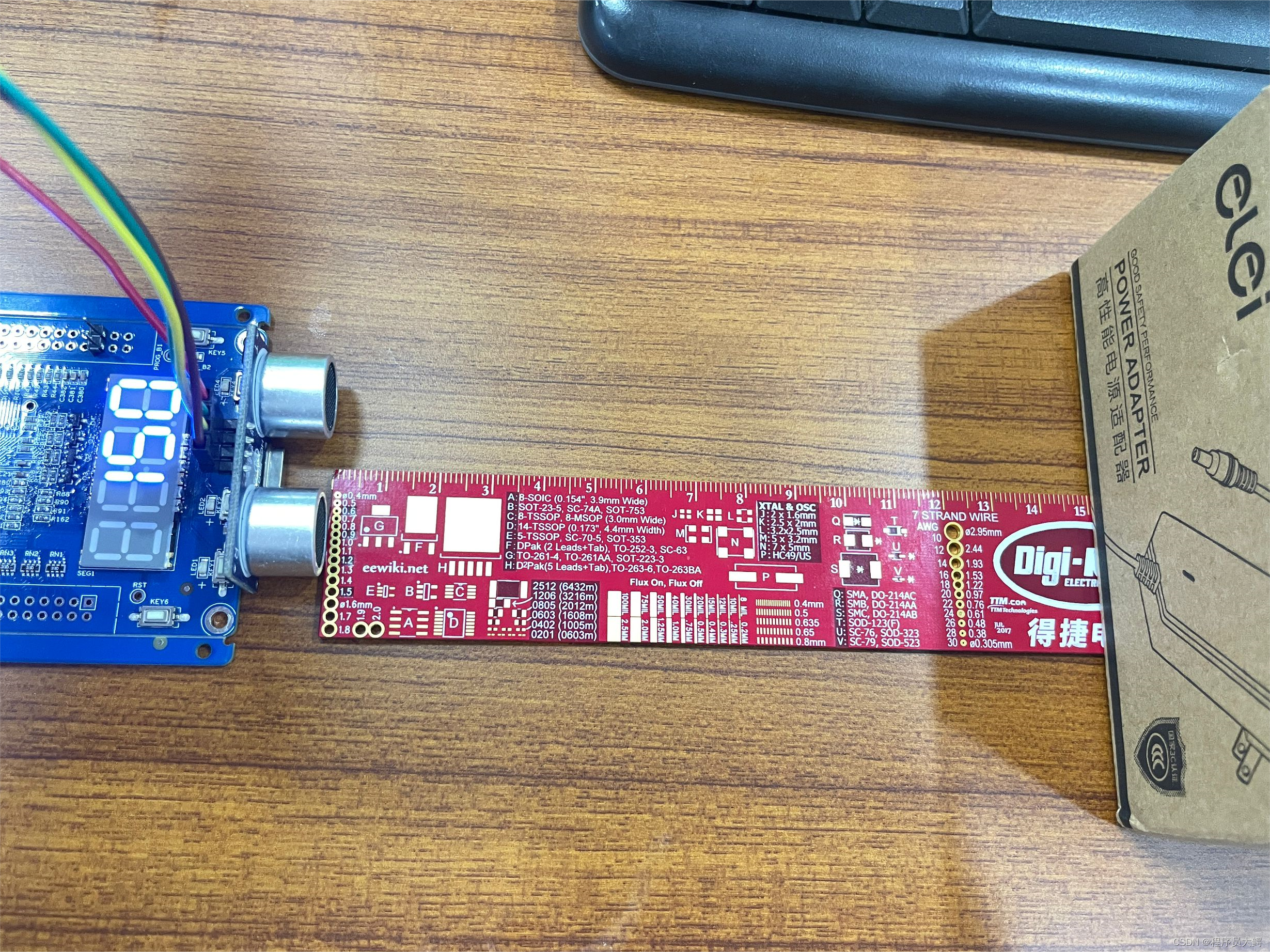

这篇文章详细描述了一个使用FPGA设计的系统,包括数码管动态显示、超声波测距功能以及与UART接口的集成,通过计数器模块生成数码管显示数据并控制其显示和符号。

这篇文章详细描述了一个使用FPGA设计的系统,包括数码管动态显示、超声波测距功能以及与UART接口的集成,通过计数器模块生成数码管显示数据并控制其显示和符号。

263

263

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?