FPGA电路逻辑的原理图方式设计与验证

实验1:拼接 4-16译码器

实验要求

用2片3-8 译码器拼接成4-16 译码器

仿真验证电路的正确性

注意观察输出信号的毛刺(竞争冒险)

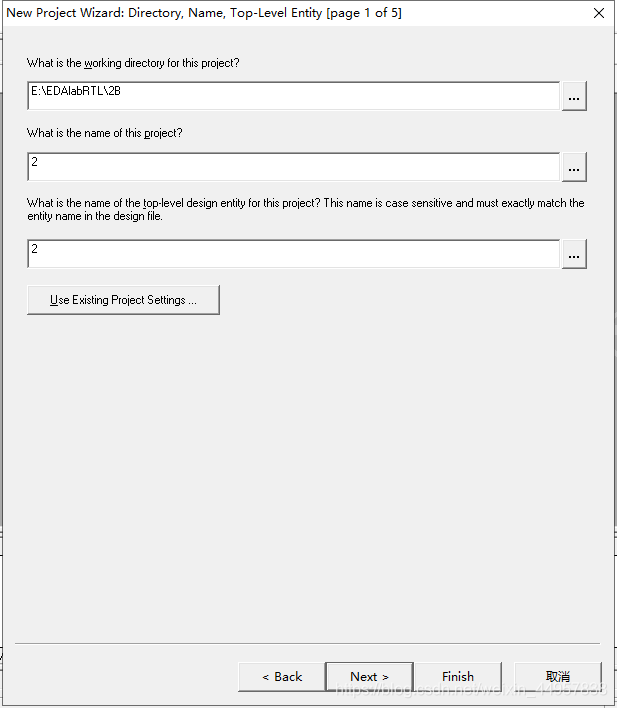

建立工程

- 打开 Quartus ,点击NEW …New project wizard…next…选择存放工程的目录,并给工程和文件命名。如图

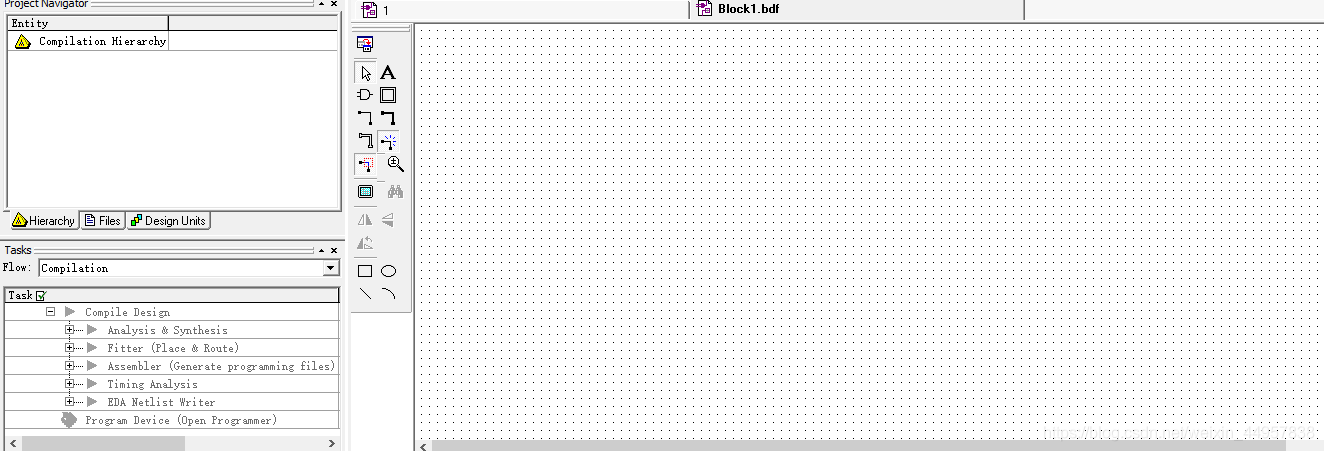

- 新建BDF文件。在上一步一路next finish之后,新建…选择BDF文件。即可完成工程创建进入如下界面

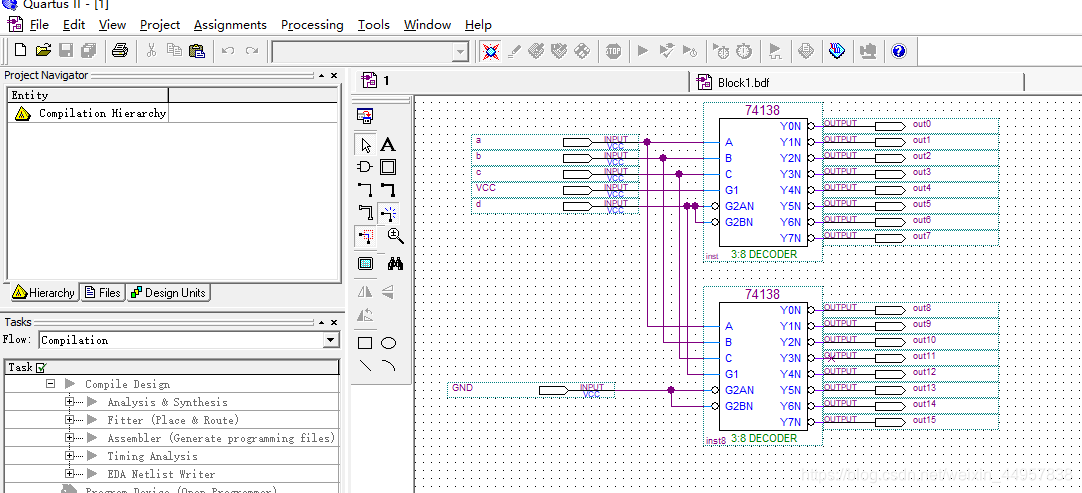

电路设计

完成工程文件创建之后,进行电路设计,电路图如下

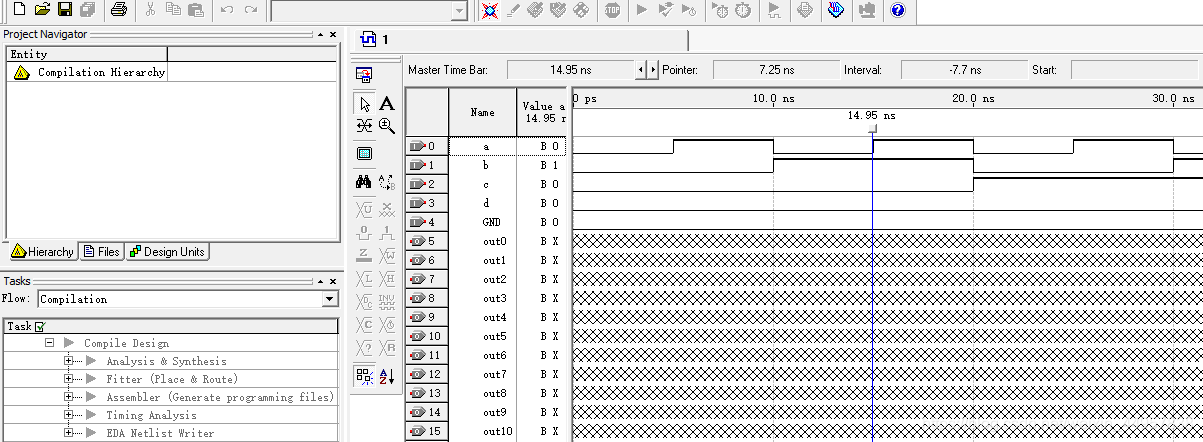

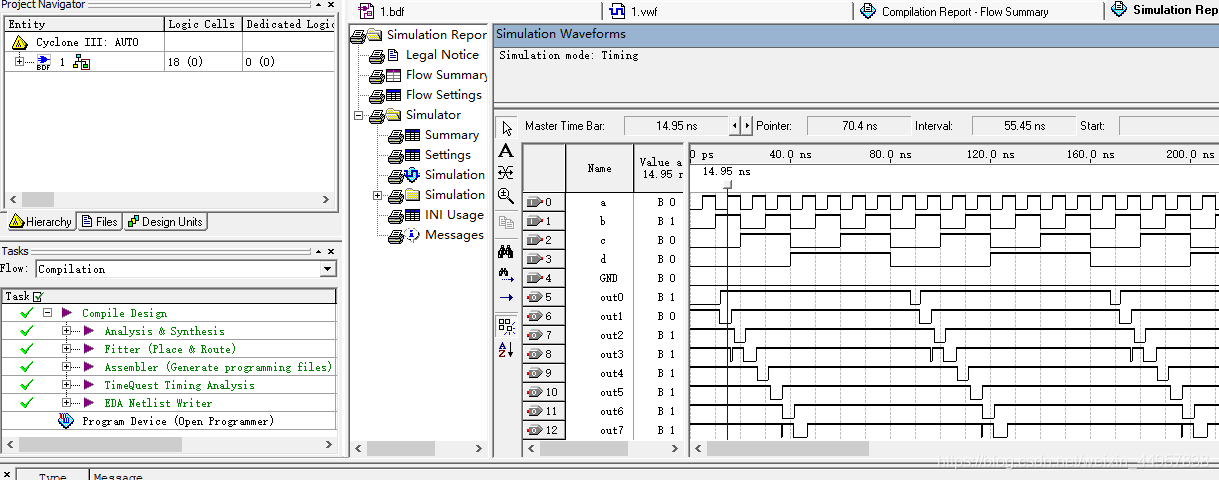

仿真设计

完成电路图设计之后进行仿真设计。

- 新建一个VWF文件。

- 添加信号。

- 进行仿真。

- 可以观察到毛刺现象。

实验2A : 设计M=12的计数器

实验要求

用161计数器芯片,设计一个M=12的计数器

上电后,对CLK信号,从0顺序计数到11,然后回绕到0

当计数值为11的CLK周期,溢出信号OV输出一个高电平,其他周期OV信号输出0

用波形仿真观察电路结果

建立工程

与上一个实验建立工程步骤相同

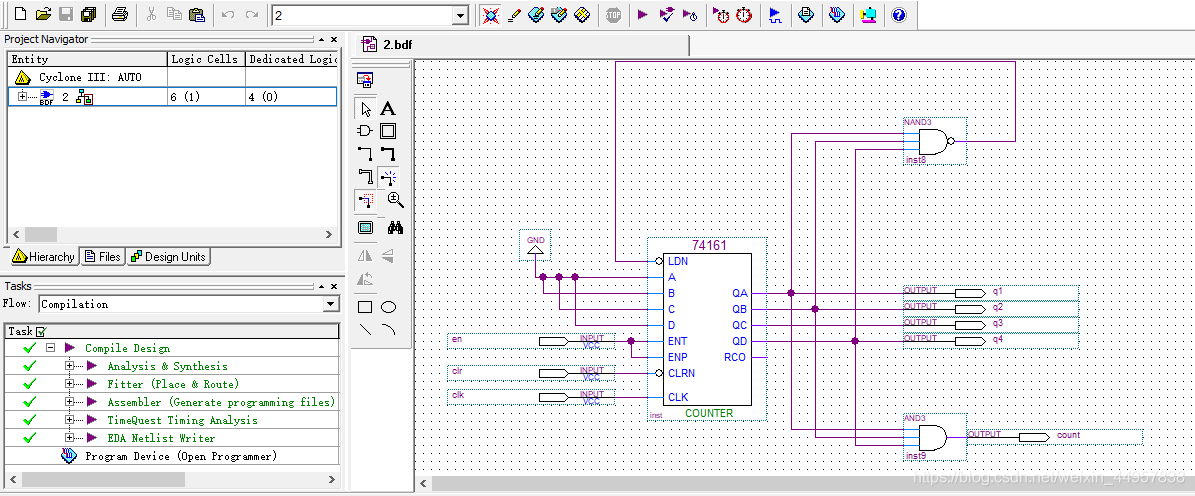

电路设计

仿真设计

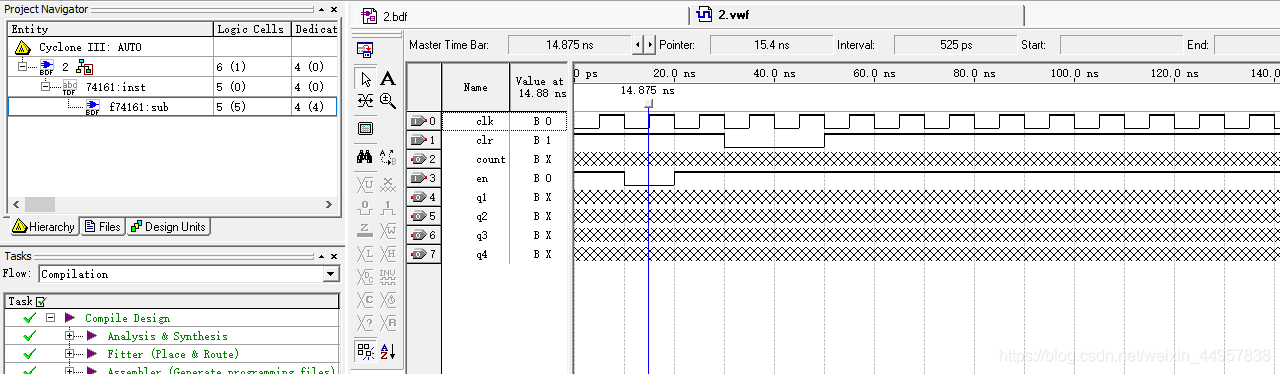

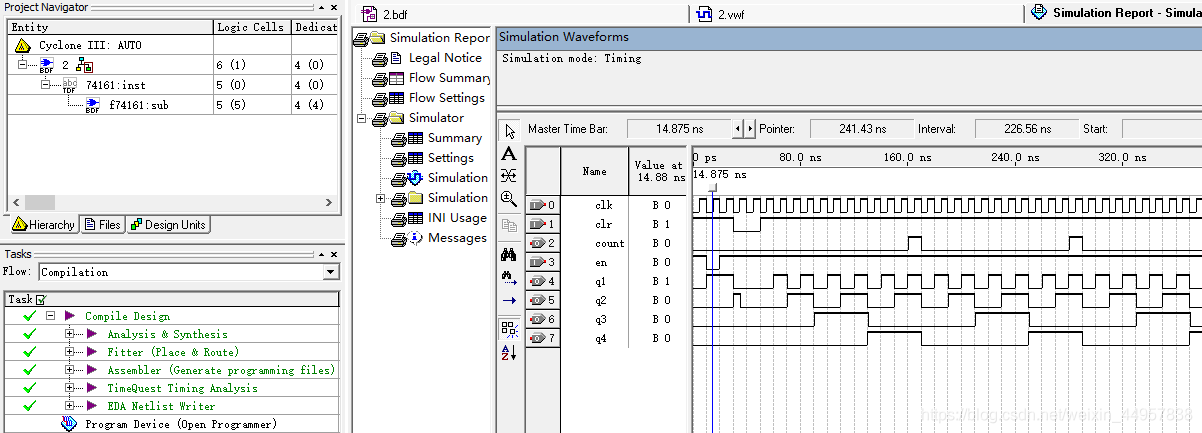

完成电路图设计之后进行仿真设计。

- 新建一个VWF文件。

- 添加信号。

- 进行仿真。

- 观察波形。

实验2B : 设计M=20的计数器

建立工程

与以上几个建立工程的步骤相同。

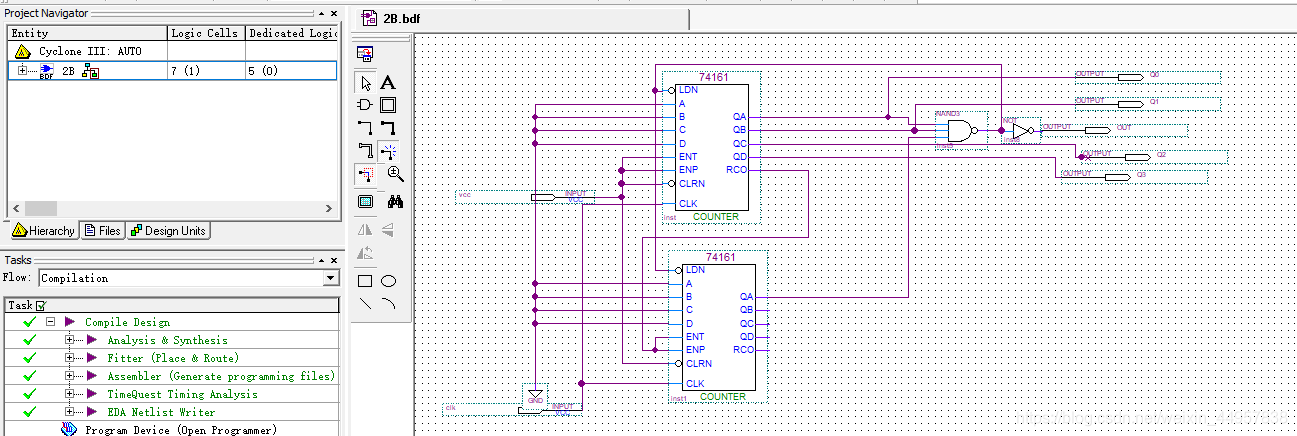

电路设计

仿真设计

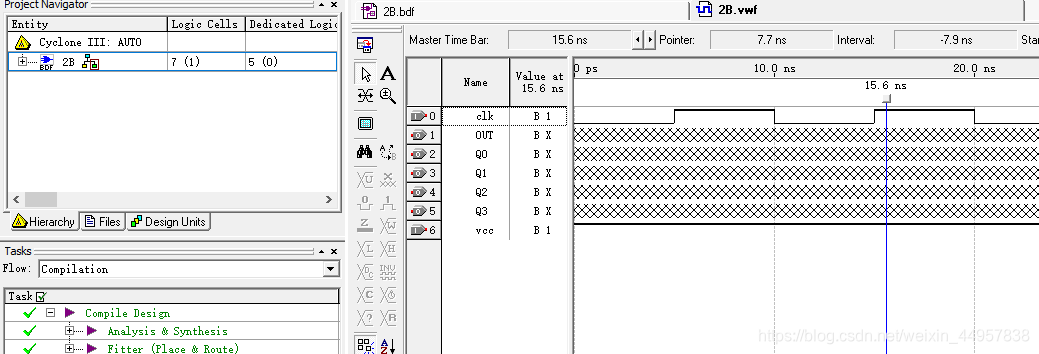

- 建立VWF文件

- 添加信号。

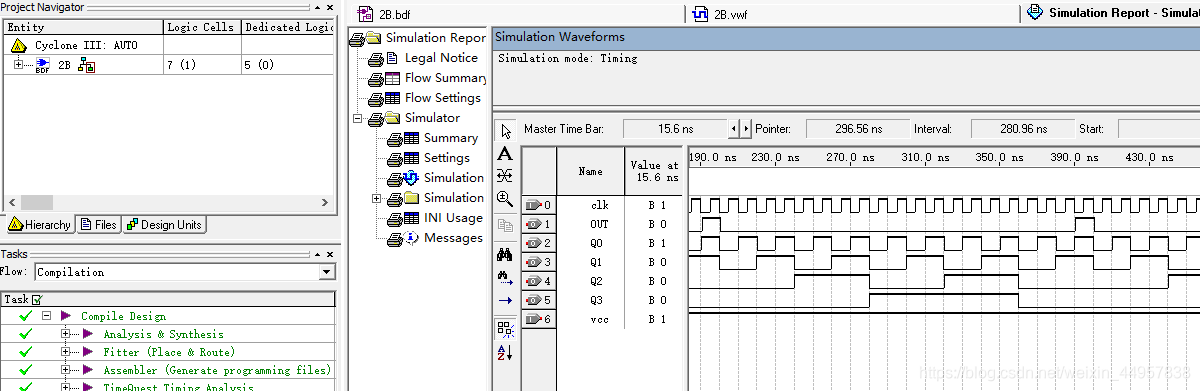

- 进行仿真。

- 观察波形,完成了20进制的计数器设计。

结束语

至此,完成了几个简单的FPGA电路逻辑的原理图方式设计与验证。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?