DFI接口协议(二)

文章目录

序

上篇文章介绍了DFI协议的overview和通用知识,本文开始介绍各个interface group的握手协议

DFI接口众多,本文开始一个个进行讲解,如有理解错误 还请及时纠正,只翻译协议中的干货,细节 如时序参数介绍等详情查看DFI协议,此系列参考资料未DFI 5.1

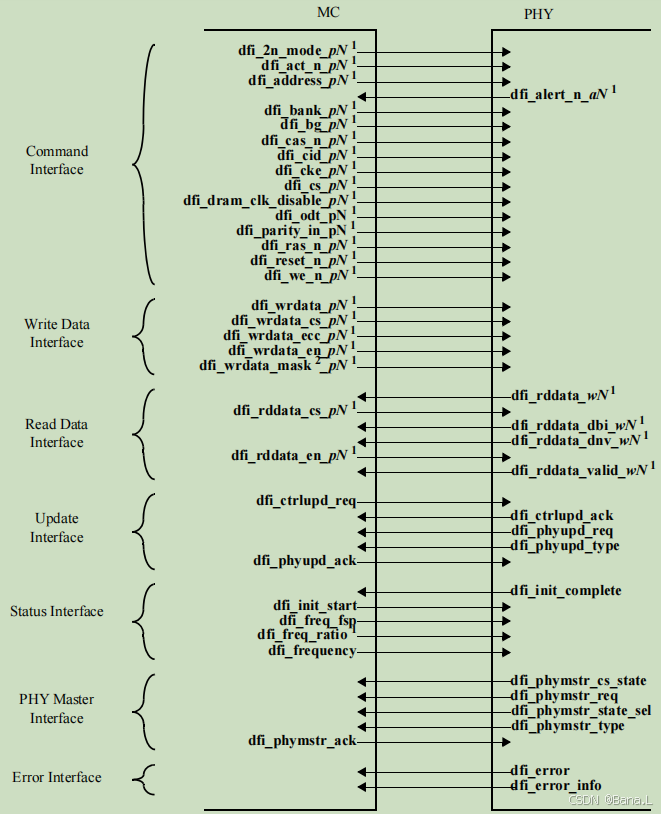

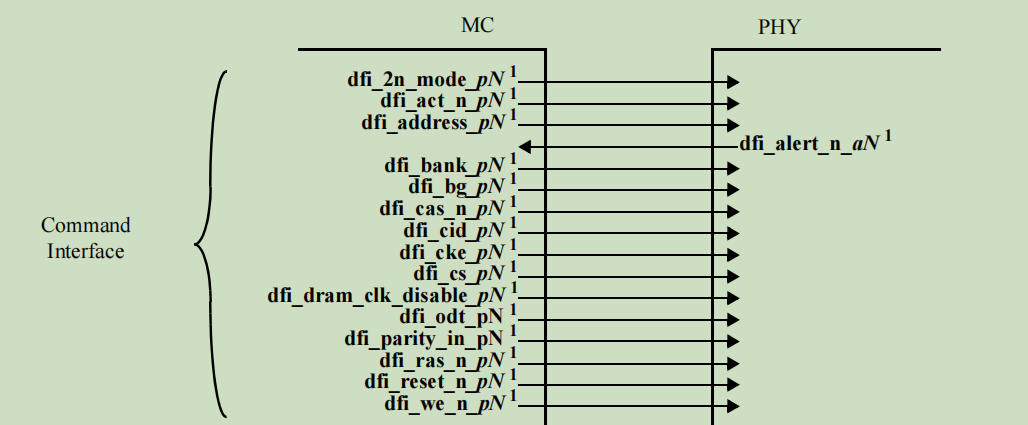

command interface

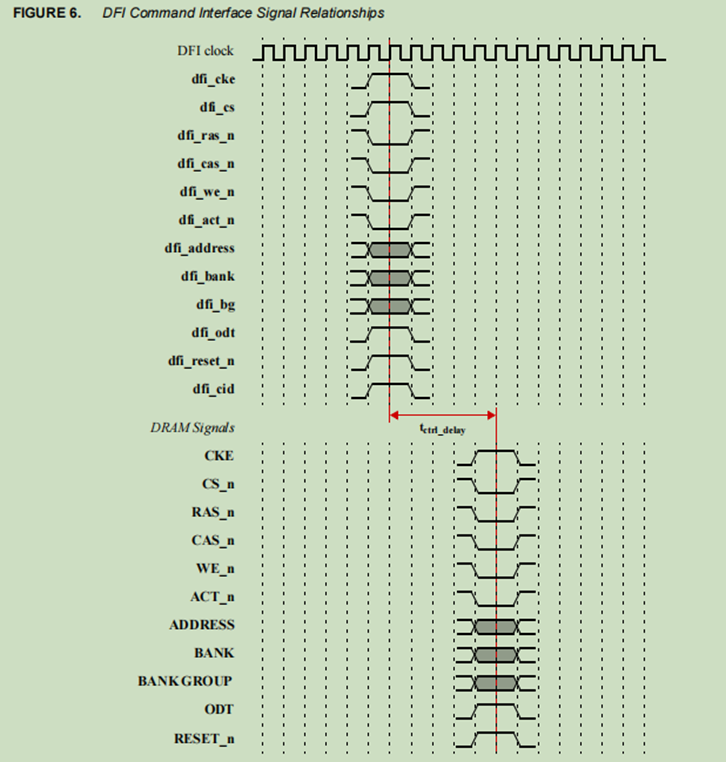

Command interface操控给DRAM设备的地址和command信号。

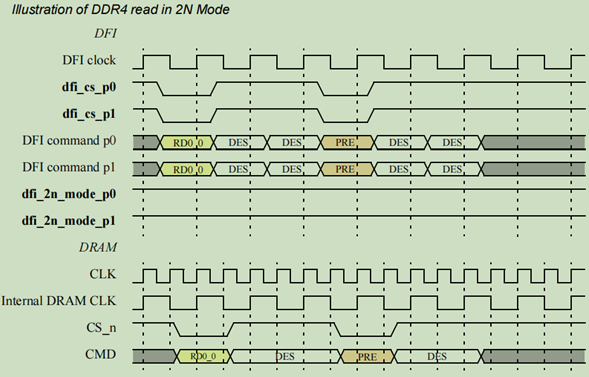

这组信号是要一直保持着DFI接口的时序信息一直到DRAM上,t ctrl_delay时序参数定义DFI接口和DRAM接口的延时。

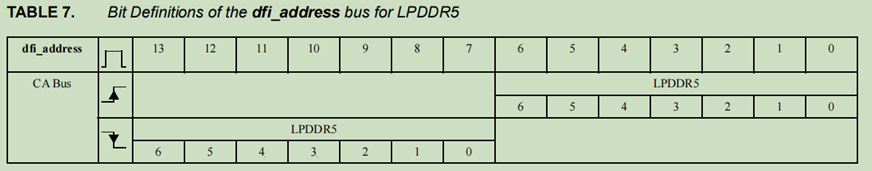

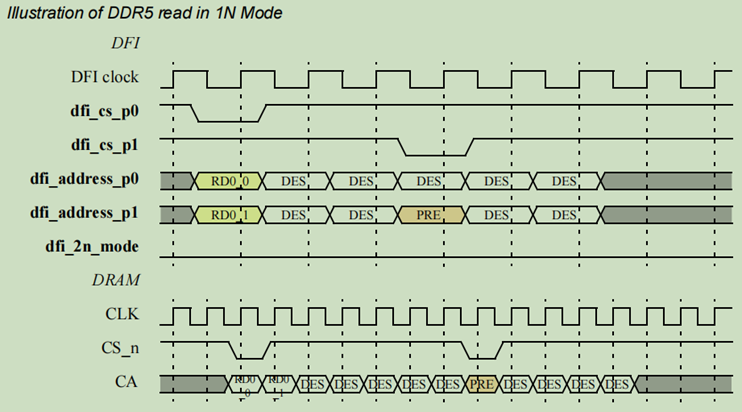

CA总线映射到dfi_address总线

对于low power存储器和最新的DDR DRAMS,CA总线会映射到dfi_address总线上。dfi_cid, dfi_bank, dfi_bg, dfi_act_n, dfi_ras_n, dfi_cas_n, and dfi_we_n 要保持恒定值。LP5和DDR5需要特殊的映射。

LP4是SDR(single data rate) CA总线,dfi_address总线是6bit宽

LP5 的CA总线是7bit位宽DDR(double data rate) 接口。因此dfi_address对于LP5是一个单相位信号,CA总线相位被连接起来,使上升边缘CA在下7位,下降边缘CA在上7位。

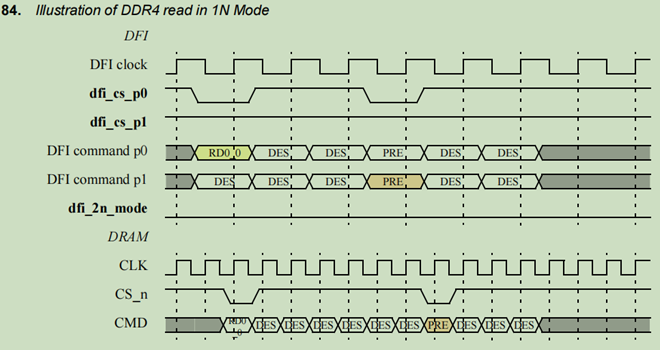

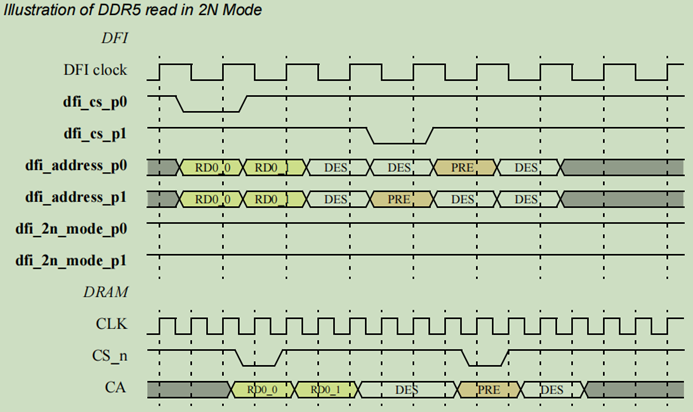

DDR5的CA总线是SDR(single data rate) 的CA 总线;因此 dfi_address总线宽度是和DDR5 CA总线宽度匹配的。对于1N mode,CA总线值由dfi_address总线驱动1 DFI时钟或1时钟相位频率比驱动CA总线值。对于2N mode是驱动2DFI clk或者2 clock phase。这命令能够启动在任何clock相位时,对于multi-clock command,必须要有连续的时钟或者相位,直到命令完成。

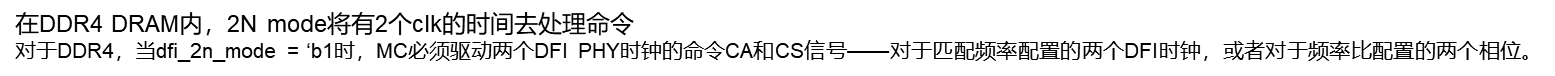

Dfi_2n_mode 在dfi_init_complete完成后的初始状态。0:1N;1:2N. —DRAM 有2N模式(也被称作geardown mode)来驱动命令总线在高频下的操作。

命令接口的时序参数

命令信号被驱动到DRAM上,并且命令信号的DFI关系将保持在PHY-DRAM边界上,因此所有信号之间的任何延迟都应该是一致的,并通过定时参数tctrl_delay来定义。

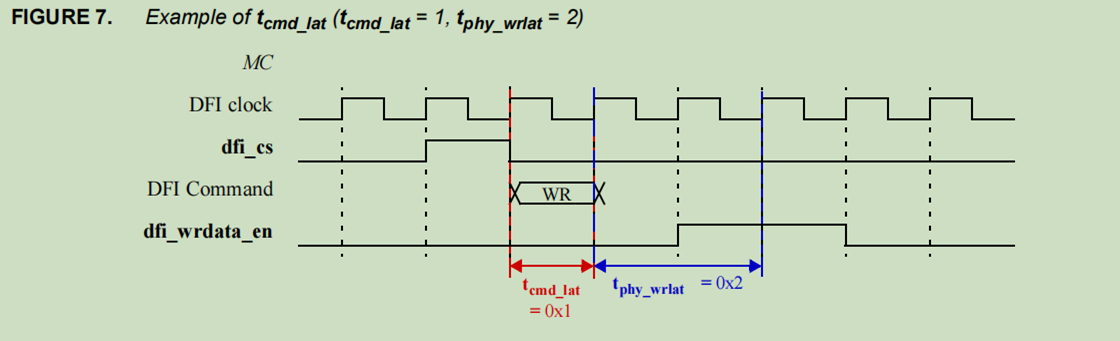

Tcmd_lat 指定断言dfi_cs信号后的DFI时钟数量,直到相关的CA信号被驱动。

Tphy_wrlat是写命令发出到dfi_wrdata_en有效之间的时间,这个图应该是标错了,后面写command会讲

2N mode

一些dram包括一个2N mode(也称为geardown mode) ,用于在高频下启用命令总线操作。

以前,系统将使用2T操作 来增加在命令总线上的设置和保持时间。

在2N模式下,所有的命令/地址(CA) 总线信号都可以从更大的setup和hold时间中获益。

此外,对于在geardown mode 下运行的DDR4存储器,CS信号 也可以受益于更大的setup和hold时间。

更大的setup和hold时间是通过在½的频率操作CA总线完成的 。DRAM每隔一个时钟对总线进行采样。

不同内存类型的要求:

对于在geardown mode下运行的DDR4 ,MC只能改变来自PHY的隔一个DFI PHY **同步脉冲 ** 定义的CA和CS信号。

对于在2N模式下运行的 DDR5 ,MC只能每隔一个的DFI PHY时钟改变CA信号,但是没有同步脉冲,对齐也没有限制。

对于2N模式,PHY可能需要改变内存命令的CA 和/或 CS相对于memory clk的对齐方式:

在正常操作中,memory命令通常与memory时钟的下降边缘对齐,以上升边缘为中心。

在2N模式下,命令应与命令的第一个时钟上升边对齐,位于命令的第二个时钟上升边缘的中心。

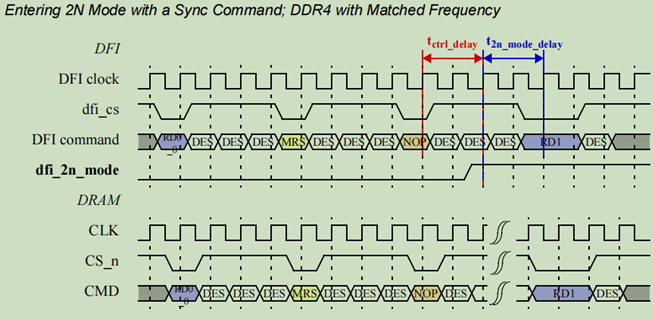

为了实现这一点,当内存在正常模式和2N模式之间改变时,PHY通过dfi_2n_mode信号接收通知。

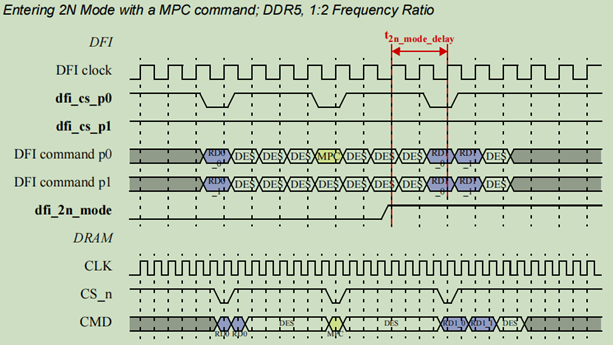

DDR5 2N mode

对于DDR5,当dfi_2n_mode = ‘b1时,MC必须驱动两个DFI PHY时钟的CA信号——对于匹配频率配置的两个DFI时钟,或对于频率比配置的两个相位。

要在DFI上进入2N模式,MC将进入DRAM 2N模式。

如果需要同步,当tctrl_delay时间从定义的同步脉冲经过时,MC将断言dfi_2n_mode信号。(T ctrl是用于同步的时间?)

如果不需要同步,MC将按照MPC命令断言dfi_2n_mode,以将DRAM置于2N模式。

在t2n_mode_delay参数中定义的时间内,CA总线信号必须保持在空闲或de-select状态,或两者都保持。在此期间,PHY会对CA和/或CS时序进行调整。要退出2N模式,要应用相同的时序,但不需要同步。

下图说明了进入2N模式发出同步和不同步命令:

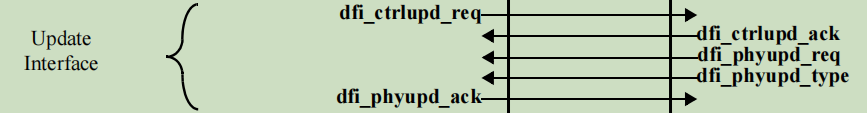

update

1 Updata interface 方便可能需要中断DFI接口信号的各种命令,包含时序调节,calibration等。

2 为了确保更新不会干扰DRAM接口上的信号,当DFI总线处于空闲状态时,DFI支持更新模式。

3 当DFI总线处于空闲状态,命令接口不发送任何命令,所有的读写数据已经在DFI总线上传输完成。数据已经达到了远端(DRAM或者MC) 并且写数据已经在DRAM总线上传输;DRAM总线的状态不被改变。

4 DFI协议支持MC发起的和PHY发起的更新。

MC 的update

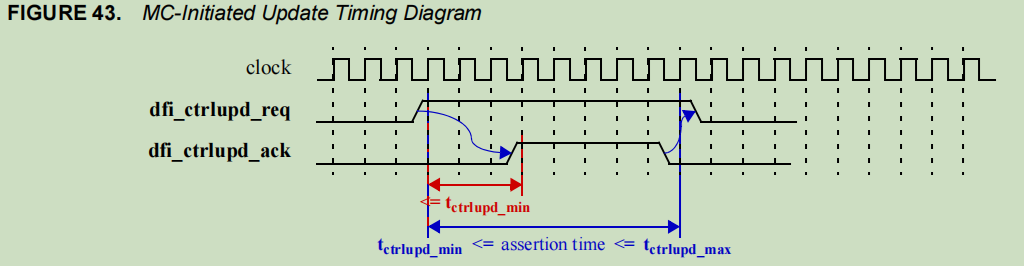

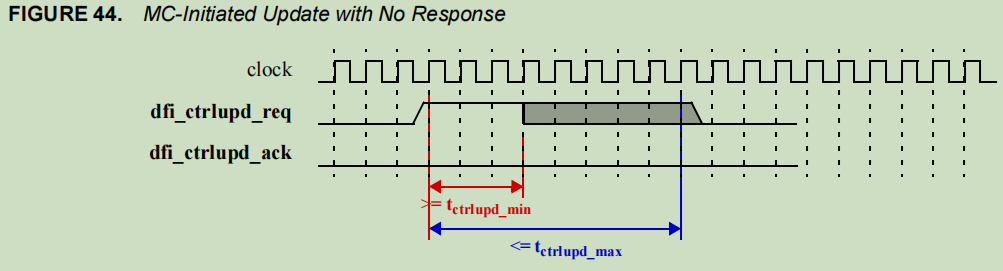

- 在正常操作期间,MC可能会遇到空闲时间,在此期间没有向dram发出命令,所有未完成的读写数据已在DFI总线上传输,写数据传输已在内存总线上完成。

- dfi_ctrlupd_req信号的断言表示DFI上的控制、读、写接口处于空闲。当断言dfi_ctrlupd_req信号时,DFI总线只能用于与更新过程相关的命令。List item

- PHY可以响应或忽略更新请求。List item

- 要ack这个req,必须在tctrlupd_max内断言dfi_ctrlupd_ack信号,同时断言dfi_ctrlupd_req信号。在tctrlupd_max结束之前,dfi_ctrlupd_ack信号必须至少无效了一个周期。List item

- 只要断言了dfi_ctrlupd_ack信号,MC就应该保持dfi_ctrlupd_req信号,尽管MC可以取消断言dfi_ctrlupd_req信号以通过断开协议断开握手。

MC保证dfi_ctrlupd_req信号被断言至少tctrlupd_min个周期,允许PHY时间响应。

PHY必须在tctrlupd_max内取消断言dfi_ctrlupd_ack信号

PHY的update

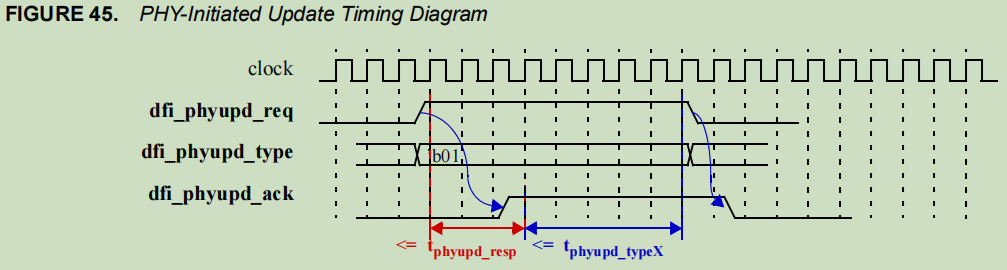

PHY更新过程利用了三个信号: dfi_phyupd_req、dfi_phyupd_type和dfi_phyupd_ack。

dfi_phyupd_req信号需要DFI在空闲时间,dfi_phyupd_type信号定义所需更新的类型,dfi_phyupd_ack信号是MC的响应信号。DFI指定了四种更新类型。

- 要请求更新,在声明dfi_phyupd_req信号时,dfi_phyupd_type信号必须有效。

- 在大多数情况下,dfi_phyupd_ack信号必须在断言dfi_phyupd_req信号后,在tphyupd_resp周期内进行断言。如果dfi_init_start、dfi_phymstr_req或dfi_ctrlupd_req与dfi_phyupd_req一起激活,则授予例外。

- 当断言dfi_phyupd_ack信号时,它应该一直保持断言,直到dfi_phyupd_req信号取消断言,除非控制器希望断开握手的连接。Dfi_phyudp_ack要在检测到dfi_upd_req取消断言后也取消断言。

- 在dfi_phyupd_req信号可以重新断言之前,必须取消声明前一个事务的dfi_phyupd_ack信号。当断言dfi_phyupd_ack信号时,DFI总线只能用于与更新过程相关的命令。

tphyupd_typeX参数表示被请求的DFI命令、读数据和写数据接口的空闲时间的最大周期数。

dfi_phyupd_req信号必须在tphyupd_typeX周期过期之前取消断言。

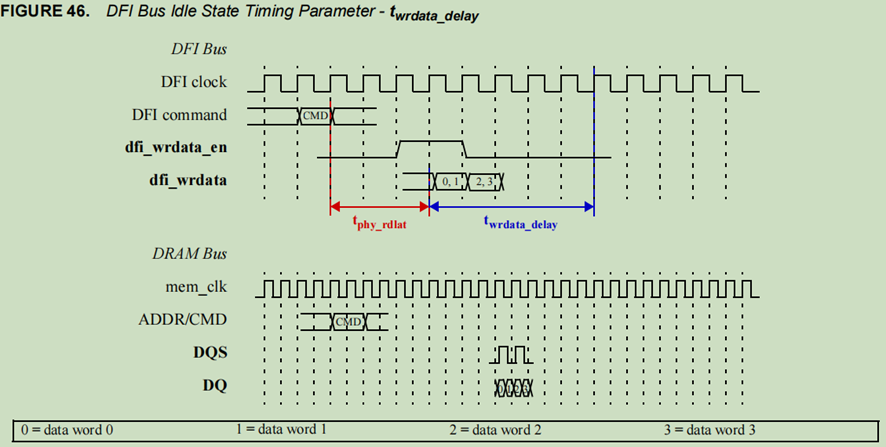

DFI BUS IDLE

当PHY在DFI总线上完成写入数据传输和空闲状态之间存在依赖关系时,twrdata_delay参数应该设置为足够大的值,以适应写入数据宽度、通过PHY的flight time和内存总线上的最坏情况时间。

当PHY在DFI总线上完成写入数据传输和空闲状态之间存在依赖关系时,twrdata_delay参数应该设置为足够大的值,以适应写入数据宽度、通过PHY的flight time和内存总线上的最坏情况时间。

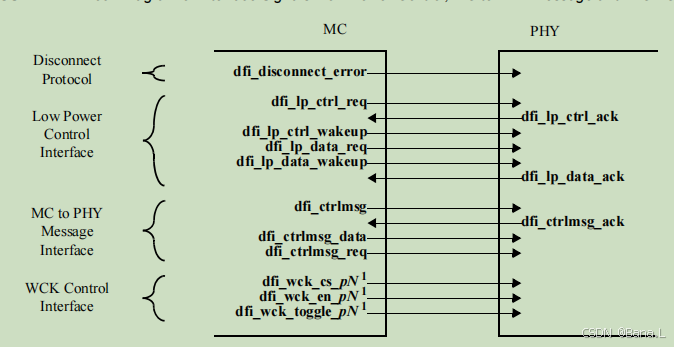

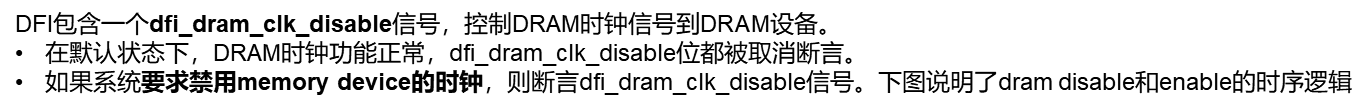

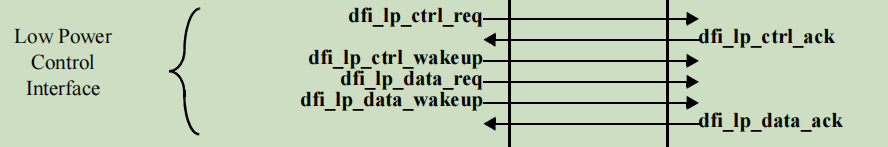

low power

-

低功耗控制接口处理进出空闲状态的信号传输;low power control是MC和PHY的一个可选择的功能,除非系统上要求低功耗接口。

-

当MC知道存储器子系统将在一段时间内保持空闲状态时,将PHY置于低功耗状态可能是有利的

-

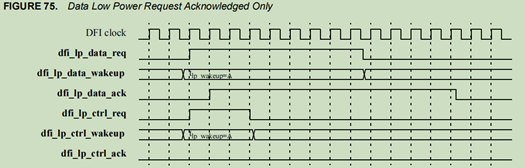

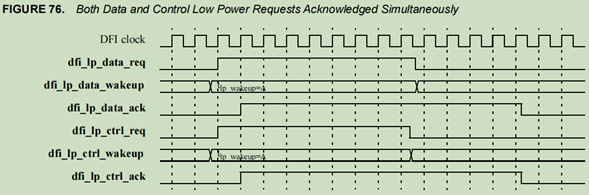

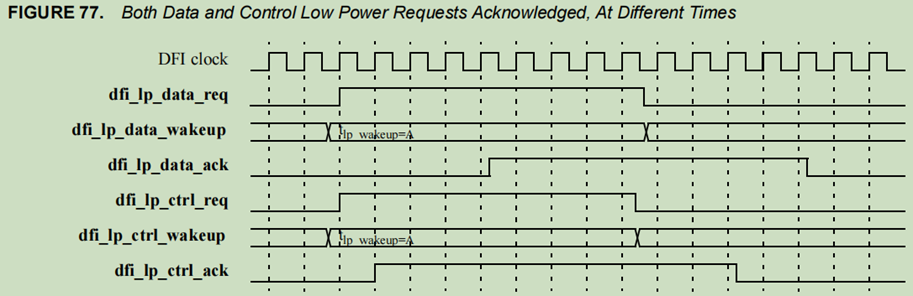

low power request(control and data)是独立的接口,他们之间没有任何关系

-

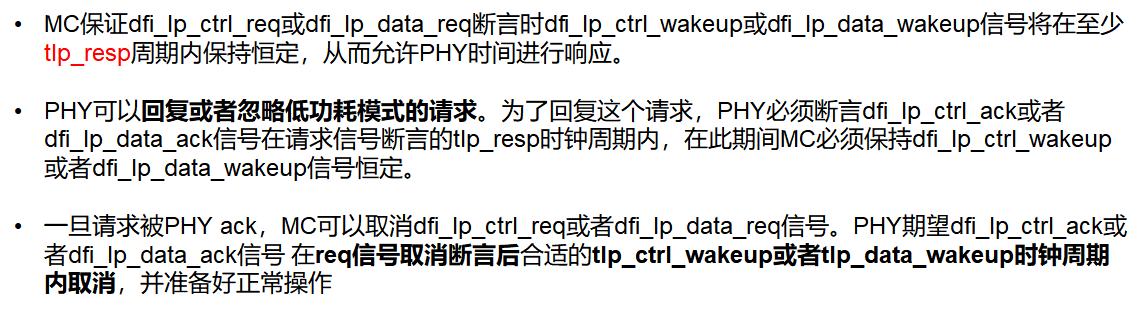

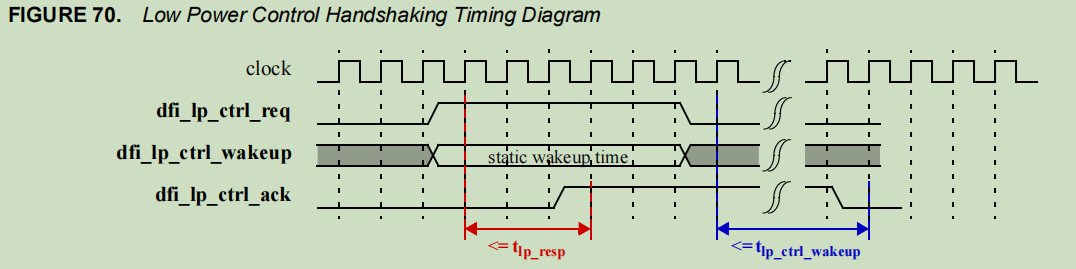

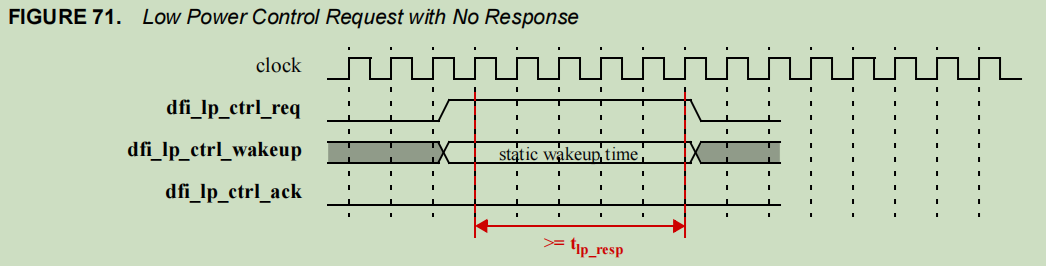

如果req由dfi_lp_ctrl_ack或dfi_lp_data_ack信号被acknowledged ,那么PHY可以进入低功耗状态as long as dfi_lp_ctrl_req或者dfi_lp_data_req信号保持断言的时间。一旦dfi_lp_ctrl_req或dfi_lp_data_req信号取消,那么PHY必须在dfi_lp_ctrl_wakeup或dfi_lp_data_wakeup信号表示的几个时钟周期内返回正常操作状态。

-

当dfi_lp_ctrl_req和dfi_lp_ctrl_ack已经断言时,MC将不会取消断言dfi_lp_ctrl_req来增加唤醒时间。为了使PHY认识到MC已经增加了唤醒时间,PHY必须监控dfi_lp_ctrl_wakeup信号。类似地,当dfi_lp_data_req和dfi_lp_data_ack信号已经断言时,MC将不会取消维护dfi_lp_data_req信号以增加唤醒时间,而PHY将需要监控dfi_lp_data_wakeup信号

-

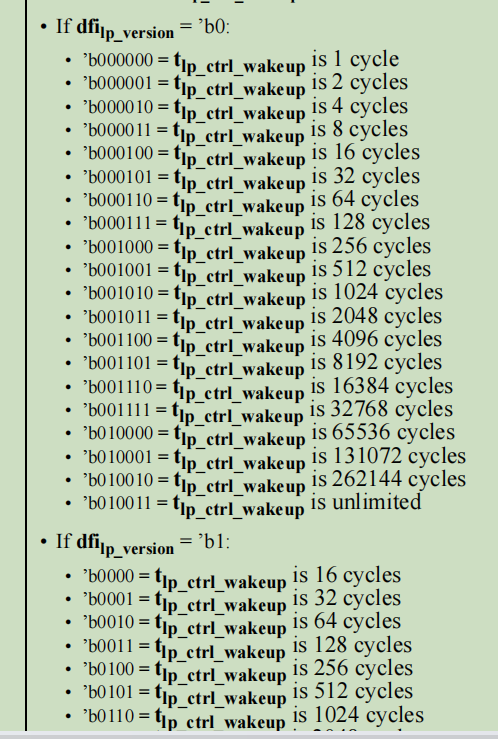

唤醒时间是一个特定的周期数(tlp_ctrl_wakeup或tlp_data_wakeup周期),其中PHY预计将响应DFI上的信号变化(取消确认dfi_lp_ctrl_req或dfi_lp_data_req信号)。DFI spec定义20种不同的wakeup时序;无论是MC或者PHY都要求支持所有的wakeup时间。Wakeup时间可以是平均值或者预估的delay;因此 超过唤醒时间不应被视为错误状态。

在确认请求后,MC可能会增加PHY必须响应的时间,以超过最初定义的时间。

这些请求是独立的,可以按顺序或同时断言,PHY可以在任何时候承认一个,两者都不承认。没有要求PHY必须按任何一种顺序进行响应。如下图:

status

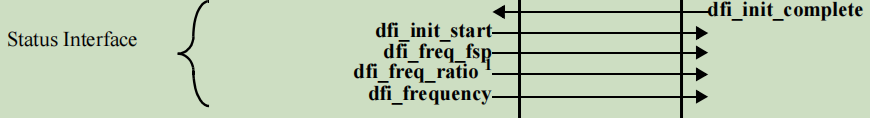

状态接口信号将初始化和PHY之间的状态信息传递到DRAM设备。

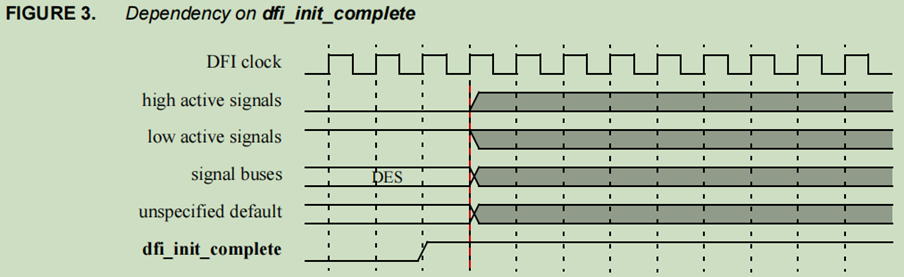

初始化

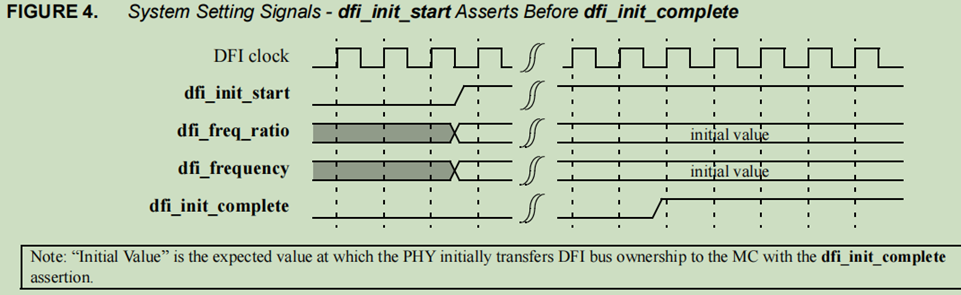

初始化使用dfi_init_start和dfi_init_complete信号。这些信号也在频率变化请求期间被使用。

在初始化时,dfi_init_start信号向PHY表示来自MC的可选DFI频率信号(dfi_frequency、dfi_freq_ratio和dfi_freq_fsp)已被定义并有效,而dfi_init_complete信号表示PHY已经准备好接受DFI事务。

频率变化

DFI频率变化协议是一种可以选择的feature。系统中可以选择使用non-DFI频率变化的方法,或者选择不支持频率变化的选项。

如果MC和PHY都选择使用DFI频率变化协议,MC和PHY必须服从由DFI spec定义的握手协议。

当频率变化的操作发起时,DFI时序参数也需要改变。

在频率变化协议期间,DFI时钟必须保持有效——工作在有效频率或门控高或低

· dfi_freq_ratio信号向PHY传递频率比信息。

· dfi_frequency信号报告了系统的工作频率。

MC启动频率变化操作,通过dfi_frequency信号编码报告新频率,通过dfi_freq_fsp信号报告新频率设定点,通过dfi_freq_ratio信号编码向PHY报告新频率比。

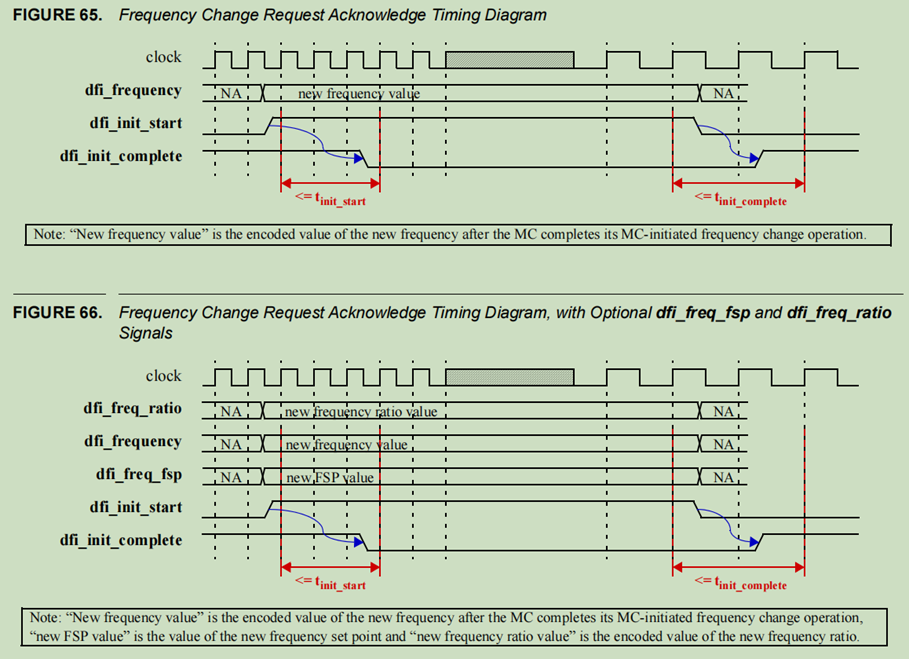

频率变化操作

- 在正常操作中,一旦 dfi_init_start和dfi_init_complete信号被断言,这个系统可以改变DFI时钟频率。

- MC断言dfi_init_start信号去表示一个时钟频率改变的请求已经产生,并且驱动新频率的编码值在dfi_frequenc信号上。

- PHY在dfi freq_change_state时序参数内 频率变化操作中 在dfi_init_start信号断言之前给到memory。

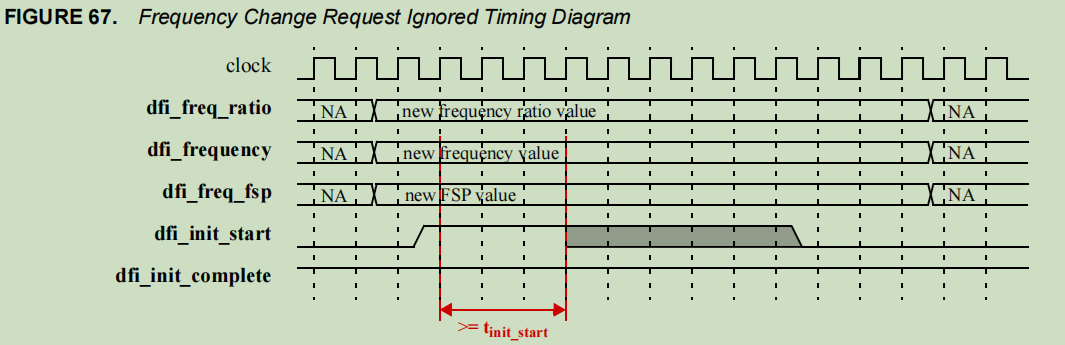

- MC认可dfi_init_start信号保持断言,在至少t init_start周期内,允许PHY有时间来响应。

- PHY可以回答或者忽略频率改变的请求。为了认可这个请求,dfi_init_complete信号必须取消断言在dfi_init_start信号断言的t init_start周期内,或进行DFI频率变化操作的机会被撤回,直到MC重新断言该信号。

- 在tinit_start到期之前,dfi_init_complete信号必须至少取消一个周期。

- 如果确认频率变化请求,只要频率变化操作继续,MC必须保持断言的dfi_init_start信号。

- 一旦频率变化操作完成,MC将de-assert dfi_init_start信号。

- PHY必须在此时完成所有的re-initialization (PHY和memory setup) ,以及对于新时钟频率的re-training,和在t init_complete周期内完成重新断言dfi_init_complete。

频率改变 –non acknowledged 当断言时,MC必须断言dfi_init_start信号至少为tinit_start个周期。需要注意的是,PHY并不需要响应频率更改请求。

error

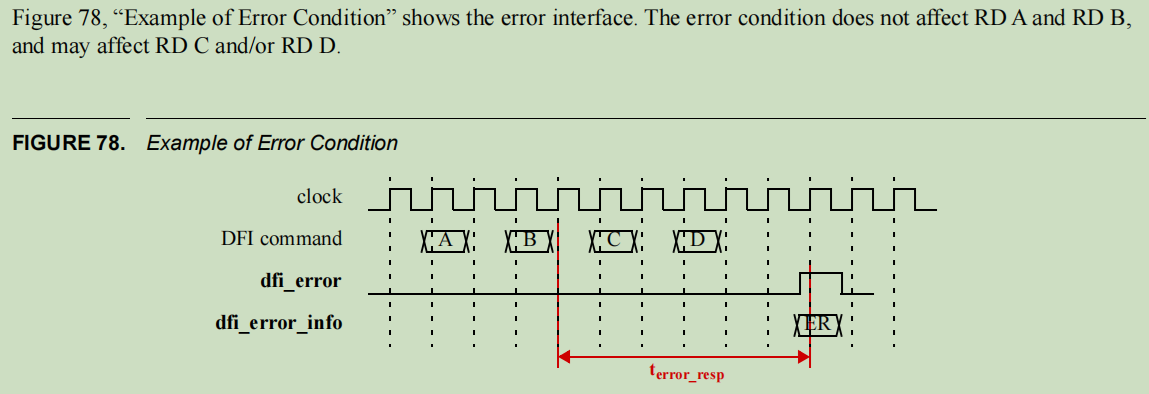

Error interface 处理错误信息的传输。是MC和PHY可选择的feature。

在DDR子系统中,PHY可以检测各种各样的错误条件,包括DRAM的错误(ECC)或者 PHY的错误(DLL lock丢失或者读DQS错误)。

在错误条件下,可能希望将来自PHY的错误信息传达给MC,以进行错误报告和其他可能的错误响应。MC除了报告错误外不能做任何其他操作。

信号如果没有被使用,必须tie LOW在MC上。

对于数据错误,,从dfi_wrdata_en或者dfi_rddata_en到dfi_error信号断言 定义了一个最大delay的时序参数。

对于命令错误,从command断言到dfi_error信号断言定义了最大时序参数。

因此时序参数是一个最大的delay,并不总是有可能将错误与特定的命令关联起来。

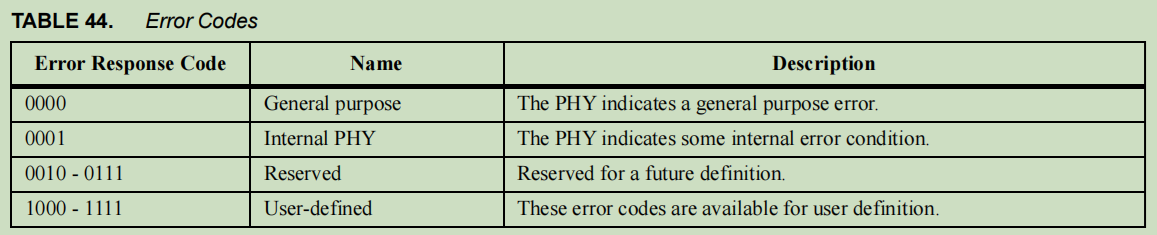

错误编码表,保留了可供将来使用的错误代码,以及可用于设计特定定义的错误代码。并非所有已定义的错误代码都适用于所有系统,而且所有错误类型都是可选的。

如果在单个时钟周期中出现多个错误,则PHY将负责通过错误优先级、使用多个时钟或通过其他方法来解决通信问题。

本文介绍了dfi的几个接口组,下篇文章继续介绍 dfi接口的读写interface、phy master和disconnecte功能接口。

8454

8454

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?