DFI接口协议(三)

文章目录

上一篇文章介绍了DFI接口的command 、2n mode、update、low power、status、error这些interface group,本章介绍write 、read data interface、 phy master、disconnecte接口功能

write data interface

写数据接口处理写数据从MC到PHY的DFI传输;该接口包括与写数据传输相关的信号、定时参数和可编程参数。

-

dfi_wrdata_en信号向PHY表示有效的dfi_wrdata和dfi_wrdata_mask将在tphy_wrdata周期中传输。

-

dfi_wrdata_mask信号有两个功能;如果DBI不使能,dfi_wrdata_mask定义dfi_wrdata将向DRAM写的数据byte数;如果DBI使能并且phy dbi_mode=0,dfi_wrdata_mask信号成为写DBI信号表示写数据是否翻转。

-

如果启用数据芯片选择,则dfi_wrdata_cs信号指示为相关的写数据访问的相应芯片选择,以独立补偿访问不同芯片选择的数据接口上的时间差异。在3DS解决方案是,将限制物理ranks的control和MRW激活。

-

对于frequency ratio系统,信号被复制到后缀“_pN”,定义PHY时钟的每个相位N的信号值。如果需要,相位0可以排除该后缀。

write data CRC

如果MC生成CRC,MC使用现有的dfi_wrdata信号通过DFI总线发送适当的CRC data word,并调整命令信号的时序来处理额外的data word。CRC发送和处理过程:

- PHY发送写命令,跟随一个数据和CRC值给DRAM。问题可以在传输这个值的时候发现

- 当DRAM逻辑比对数据和CRC的值和,如果不匹配,将在memory 总线上发送ALERT_N信号

- PHY通过dfi_alert_n信号传输这个ALERT_N值

Write data CRC时序参数:tphy_wrcsgap, tphy_wrcslat, tphy_wrdata, tphy_wrlat, twrdata_delay, tphy_crcmax_lat ,tphy_crcmin_lat.

MC可以使用这些时序参数来精确定位与错误条件相关联的命令或命令集,并在CRC错误被解决后重新发出命令。

write data timing parameter

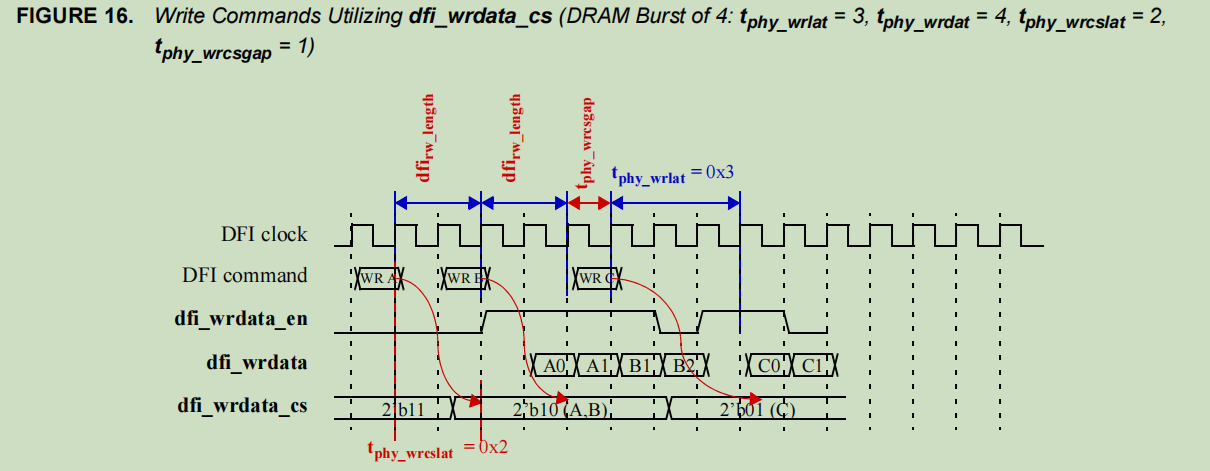

- T phy_wrcsgap时序参数用来确定切换cs驱动的时间, 由phy定义的最小延时。

- T phy_wrcslat时序参数用来联系dfi_wrdata_cs有效和写命令发出的最大时间的灵活性。两个不同cs目标的额外delay。

- T phy_wrdata时序描述dfi_wrdata_en信号有效到dfi_wrdata总线驱动的时间。

- T phy_wrlat时序参数描述写命令发出到dfi_wrdata_en信号有效之间的时间。

- T phy_wrdata_delay参数描述dfi_wrdata_en有效到数据在DRAM总线上传输完成的时间。

- PHY定义的T phy_crcmax_lat和T phy_crcmin_lat时序创建一个时间段,是CRC错误在DFI总线被发现的时间。

当命令在DFI总线上执行时,写时序参数(t phy_wrdata tphy_wrlat tphy_wrcslat)必须保持恒定,时序参数可以在DFI总线空闲时改变。T phy_wrdata和t phy_wrlat时序参数一起定义了从在DFI命令接口上发出些命令 到些数据在DFI总线被驱动的时钟数,并且一定要和DRAM时序相关的write latency 保持一致。

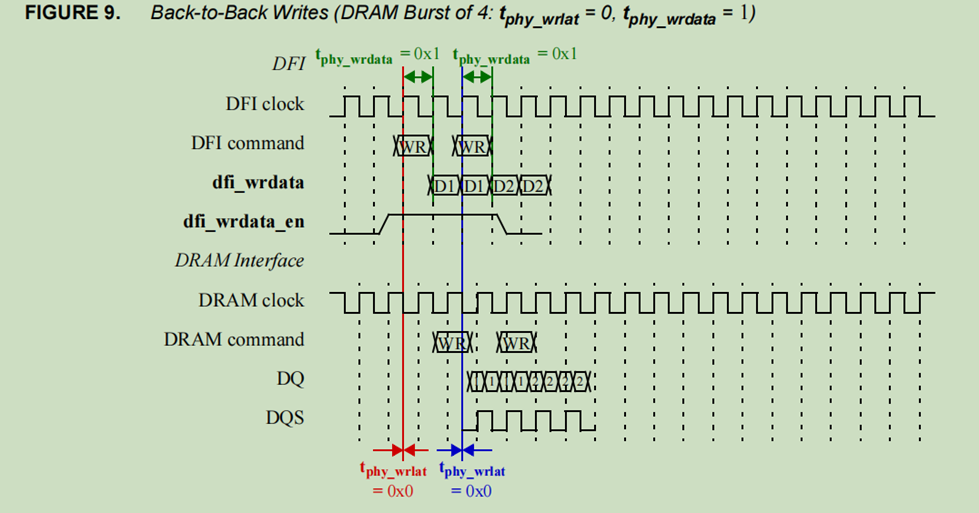

The sequence for DFI write transaction

- 写命令发出— a. t phy_wrlat时钟流逝; b. t phy_wrcslat时钟流逝

- MC驱动dfi_wrdata_cs一个最小DFI数据传输宽度(dfi rw_length)加上间隔时序(Tphy_wrcsgap); 相对于写命令,cs保证保持被驱动到PHY的最小时间由tphy_wrcslat + dfi rw_length + tphy_wrcsgap定义。

- 对于非连续写的命令,dfi_wrdata_en信号在t phy_wrlat 后在DFI总线发出,并且保持几个时钟周期的有效来完成写数据在DFI命令接口上发送

- 对于连续的写命令,dfi_wrdata_en 信号在t phy_wrlat满足后保持完整数据流的有效;t phy_wrlat可以是0。(如果启用CRC,MC将扩展dfi_wrdata_en信号以适应扩展的DRAM突发长度,每个突发可以断言信号的周期为奇数。)

- 等待t phy_wrdata时间的流逝

- dfi_wrdata和dfi_wrdata_mask发送

- 当在dfi_wrdata总线发送最后一个有效数据之前,dfi_wrdata_en信号无效tphy_wrdata个周期。

- tphy_wrdata_delay 个周期流逝,DFI bus进入空闲状态。

The first two commands (WR A and WR B) address CS0 while the third one (WR C) addresses CS1.

The two Frist command back to back, that is, spaced by dfi rw_length. The third command is also back to back, but with the required extra spacing, tphy_wrcsgap

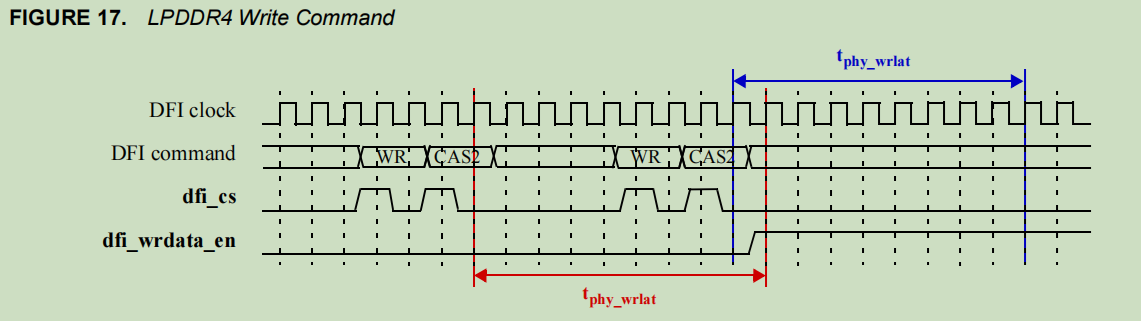

上图所说,读取命令和写取命令的DFI定时参数将从第二个命令的第二个刻度开始引用,其方式与JEDEC LPDDR4引用RL和WL相同。

DBI

我有发一篇文章说明DBI的具体时序和操作,可以移步参考一下。

在DBI模式下,PHY只需要通过PHY传输写DBI数据。当写入数据正在传输时,DBI数据在dfi_wrdata_mask信号上同时传输。dfi_wrdata_mask信号与相应的dfi_wrdata总线同步发送。

当在一个系统中同时启用DBI和CRC时,需要特别注意DBI和CRC的执行位置,以便正确操作。DBI倒置应在CRC编码之前生效。

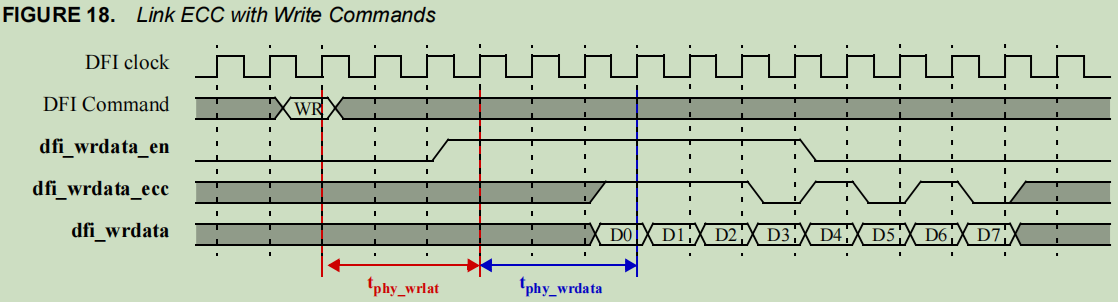

LINK ECC

如果MC正在处理link ECC操作,则MC将通过dfi_wrdata_ecc信号上的DFI总线传输写ECC

CRC时序说明

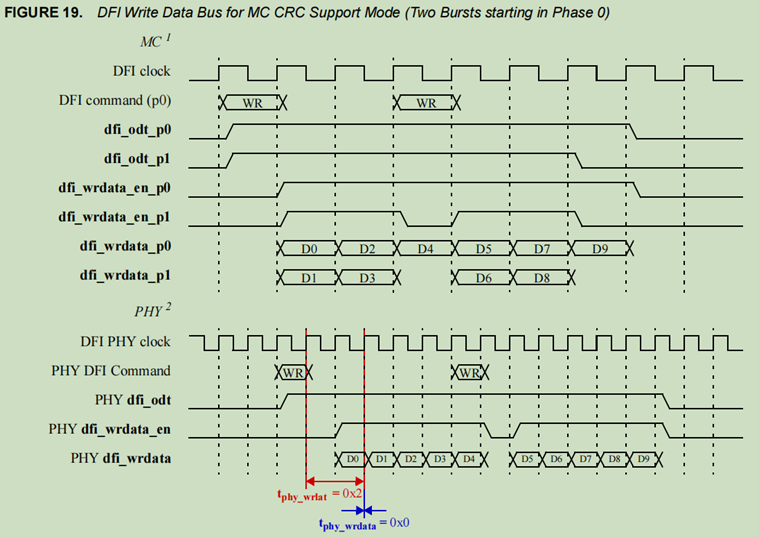

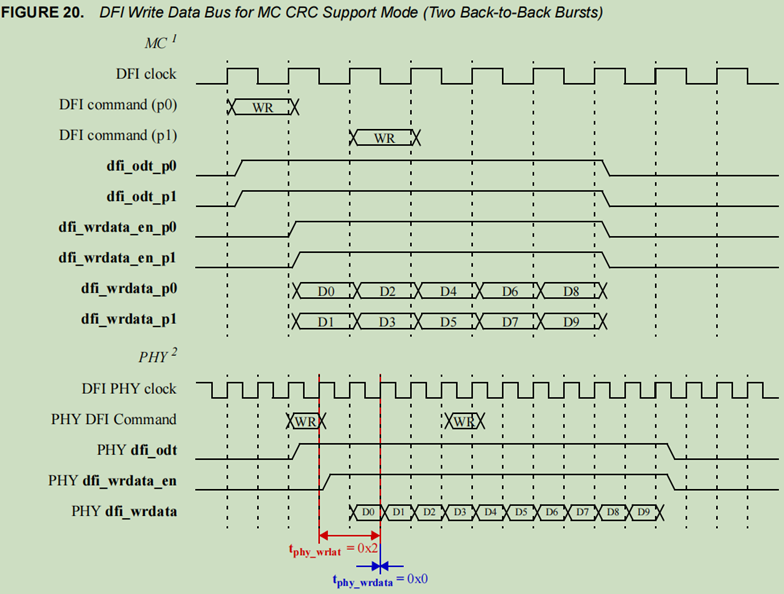

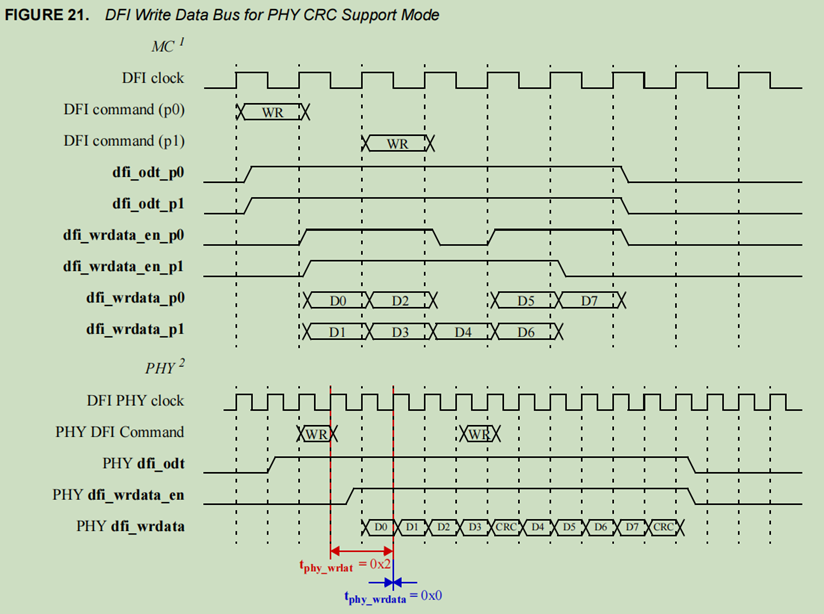

CRC将8个单位间隔(UI)的突发扩展到10个UI。

当使用CRC时,MC或PHY都可以生成CRC数据;但是,如果PHY没有生成CRC数据,则MC必须生成CRC数据。

PHY定义了phycrc_mode可编程参数的值。只有当DFI中支持CRC并使用以下定义来确定如何处理CRC时,才需要phycrc_mode参数:

phycrc_mode = 0 CRC generation is handled in the MC

phycrc_mode = 1 CRC generation is handled in the PHY

下面这个时序图包括MC时序和PHY如何在PHY时钟域中表达MC时序的说明:

- 在MC时钟图中,时序显示了DFI总线信令。

- 在PHY时钟图中,计时说明了PHY如何解释DFI总线。PHY时序仅用于说明目的

MC 插CRC:

PHY 插CRC:

CA总线时序

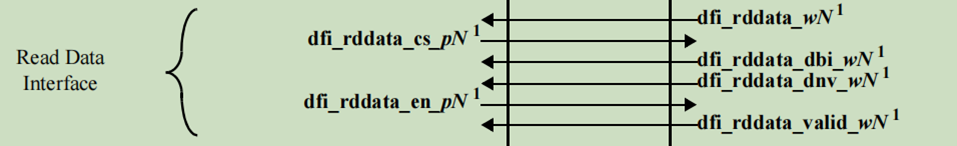

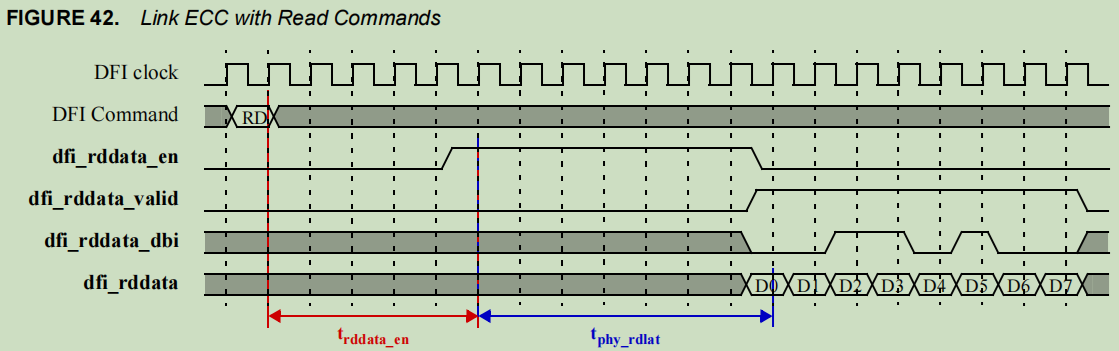

read data interface

读取数据事务处理跨DFI的数据捕获和返回;该接口包括信号、时序参数和可编程参数。

- Dfi_rddata_dbi 读数据DBI或者link ECC,由phy dbi_mode和phy link_ecc_mode控制。

- dfi_rddata_valid 读有效

- Dfi_rddata_dnv 读数据无效

dfi_rddata_valid信号允许每个PHY data slice独立返回dfi_rddata。dfi_rddata_valid信号的宽度相当于PHY data slice的数量。

dfi_rddata_valid信号是对dfi_rddata_en的响应,在dfi_rddata_en有效的时钟数和dfi_rddata_valid有效的时钟数之间存在一对一的对应关系。

dfi_rddata_en断言的时钟的数量必须与在DRAM总线上执行的数据传输的数量相关联。

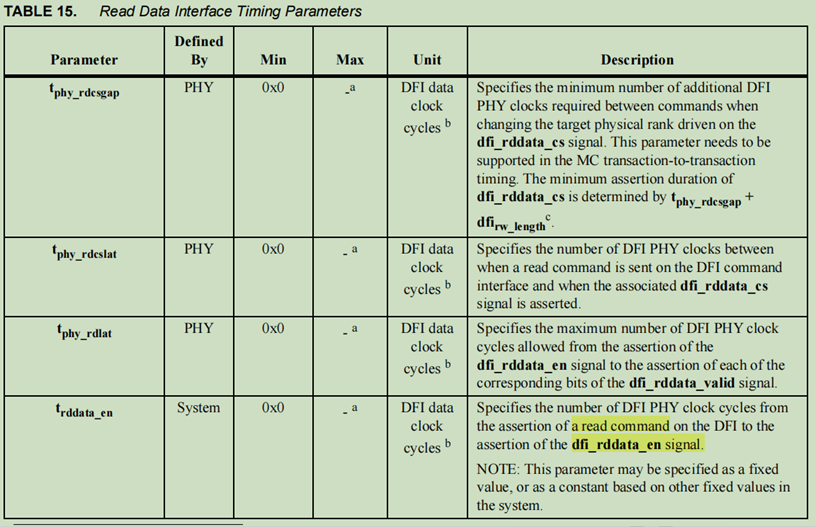

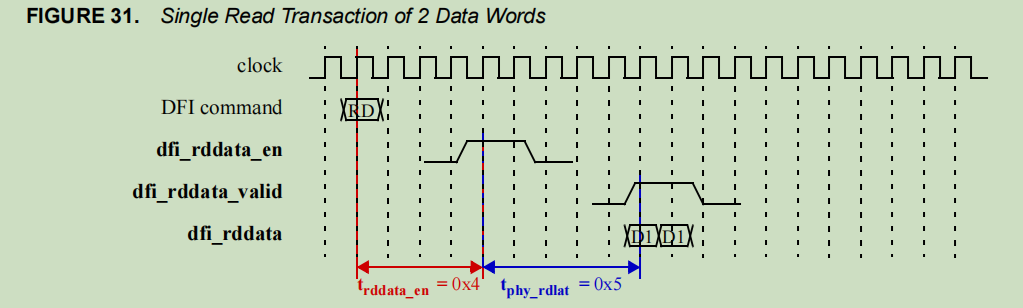

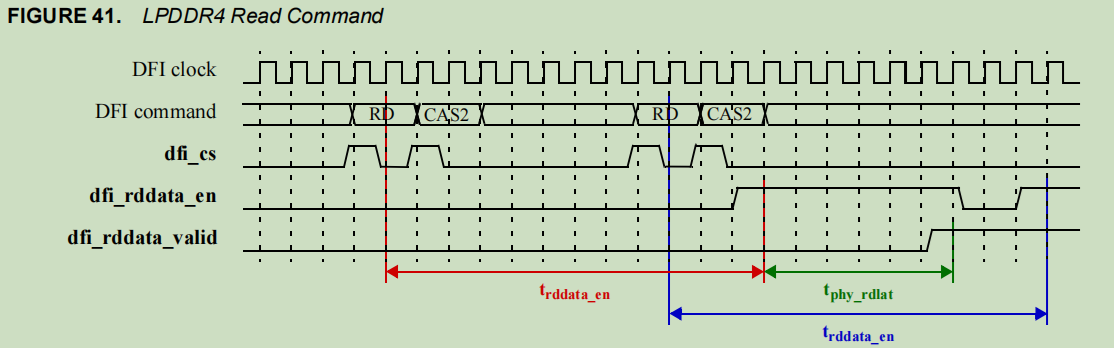

DFI读取数据必须在由trddata_en和tphy_rdlat时序参数之和定义的最大延迟范围内从PHY返回。

trddata_en是一个固定的延迟,但tphy_rdlat被定义为一个最大值。

The sequence for DFI read transaction

- 读命令发出

- t rddata_en 周期流逝

如果使用chip select, tphy_rdcslat周期流逝。不同的芯片切换的时候tphy_rdcsgap时序参数可能不同,比如从chip0chip1可能不需要额外的delay,但是chip0->chip2需要。 - 对于非连续的读命令,trddata_en周期流逝,dfi_rddata_en信号会在DFI上有效,并对预期读取数据的连续周期数保持一直有效。

- 对于连续的读命令,trddata_en周期在此次的第一个stream之后开始流逝,dfi_rddata_en信号开始有效,并持续完整的数据流。

- 对dfi_rddata_en信号的一个连续的断言可能包含了针对多个读取命令的数据。dfi_rddata_en信号取消有效,表示DFI读命令期望没有更多的连续数据。

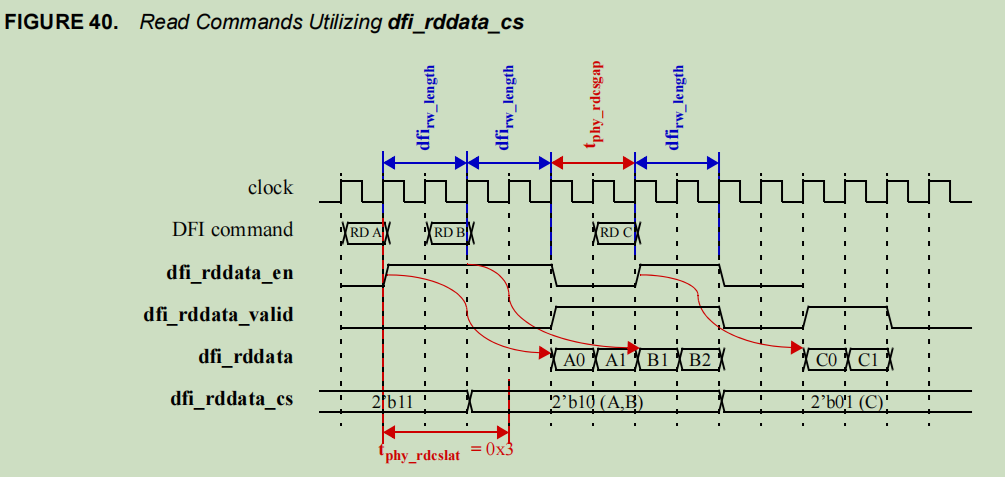

MC相对于读取命令继续驱动dfi_rddata_cs信号到PHY的最短时间由tphy_rdcslat + dfirw_length + tphy_rdcsgap定义。 - 数据随着dfi_data_valid信号的有效返回

- 相关的读数据发送(dfi_rddata)。

在上图这种情况下,dfi_rddata_en信号被断言两个周期,以通知DFI期望两个周期的DFI数据,数据在dfi_rddata_en信号断言之后返回tphy_rdlat周期。

上图显示一个单个读取事务,其中数据返回的时间小于最大延迟。该数据返回的周期比最大PHY读取延迟小一个周期。

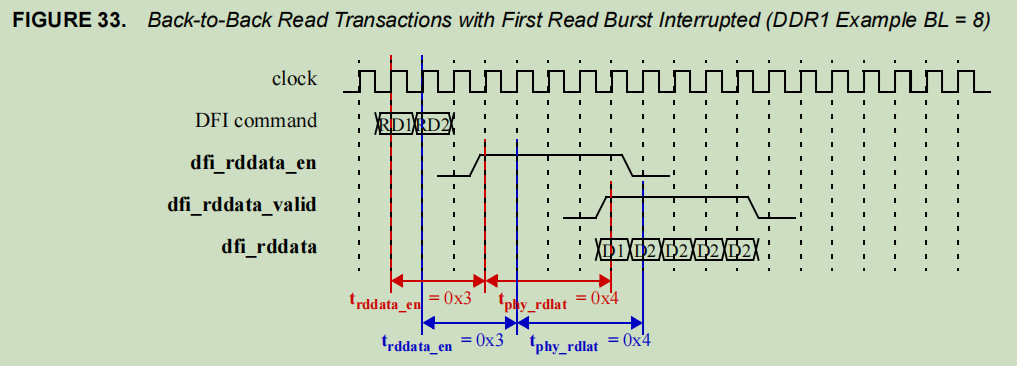

上图说明 对于每个这些读取的事务,dfi_rddata_en信号必须被断言为4个周期。然而,由于第一次读取被中断,因此对于第一事务和完整的第二事务的一部分断言dfi_rddata_en信号。

在这种情况下,dfi_rddata_en信号将不会在读取命令之间取消断言。

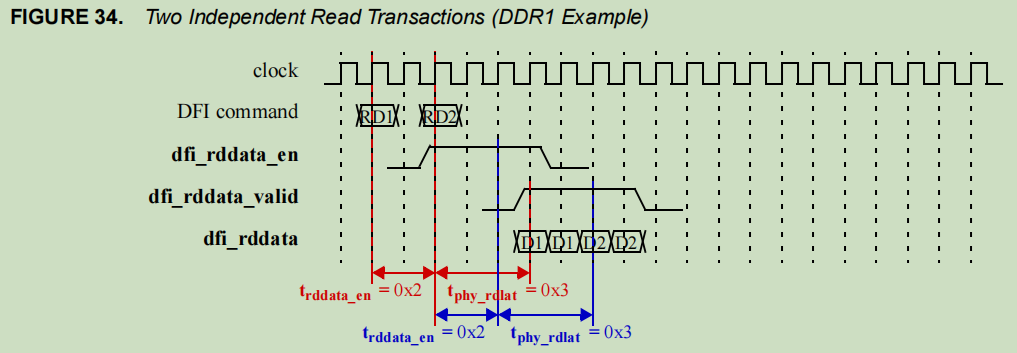

上图表示两次独立的读transaction。每个读取事务声明dfi_rddata_en信号为两个周期。

时序参数使读取的数据在两个transaction的连续数据流中返回。因此,dfi_rddata_en信号和dfi_rddata_valid信号分别为完整读数据流。

dfi_rddata_valid信号在命令之间被取消断言,而dfi_rddata流是不连续的。

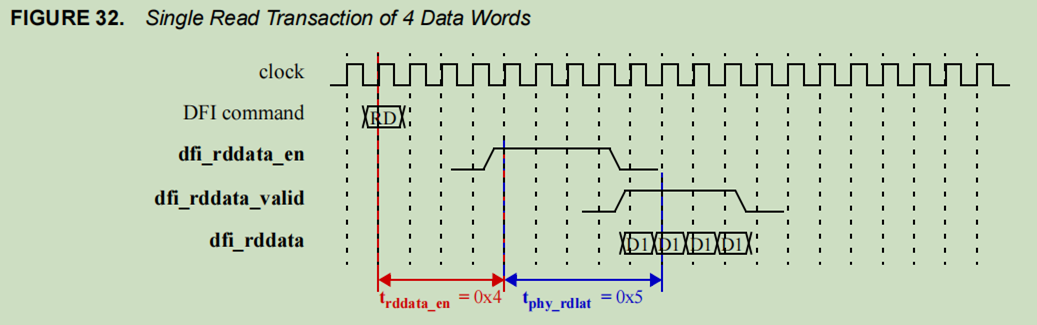

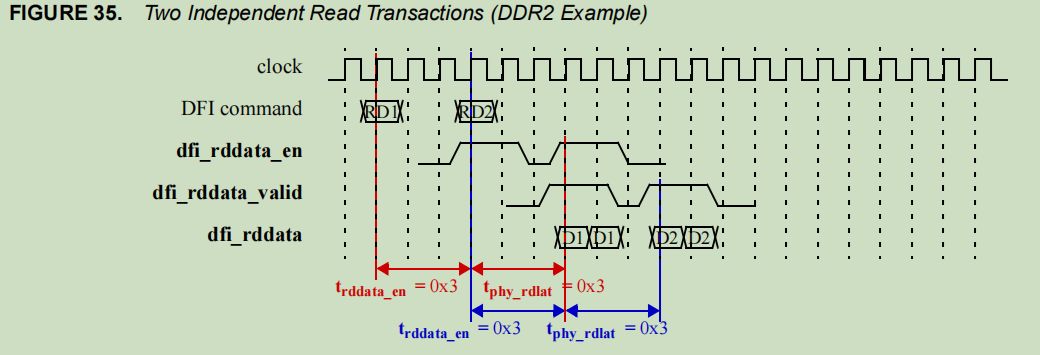

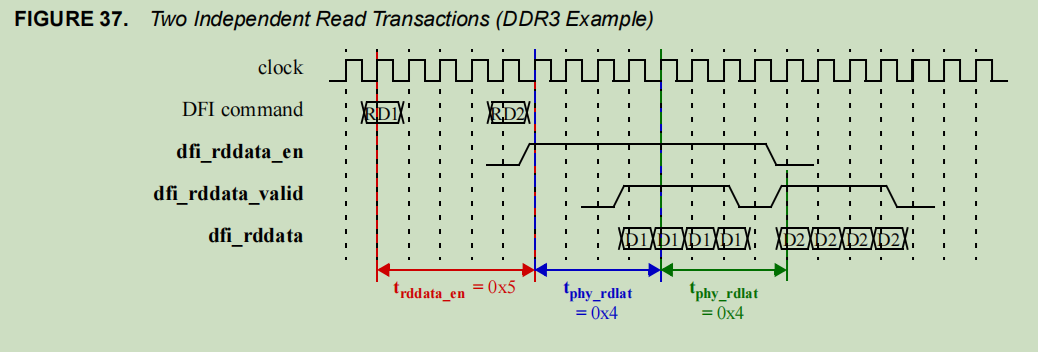

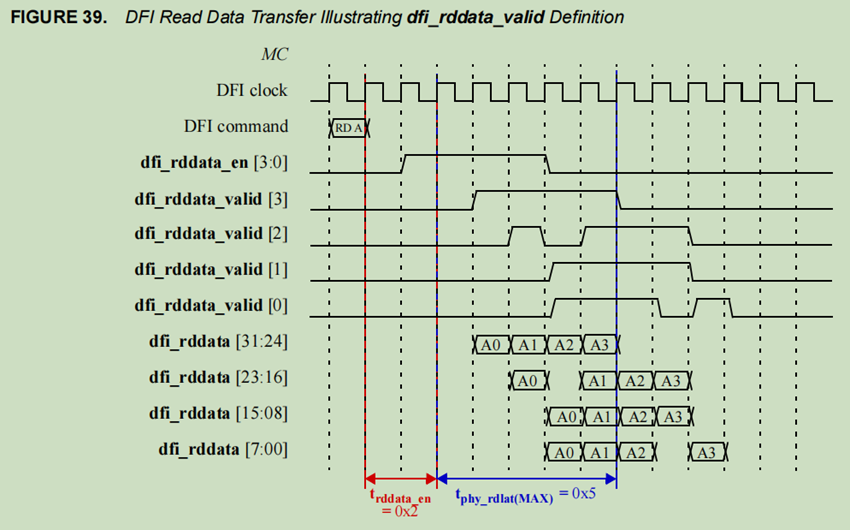

上图说明 数据可以以比最大延迟最少的周期返回到DFI。

第一次读取数据传输在三个周期中返回,即使tphy_rdlat定时参数被设置为四个周期。

第二次读取数据传输在最多四个周期内返回。

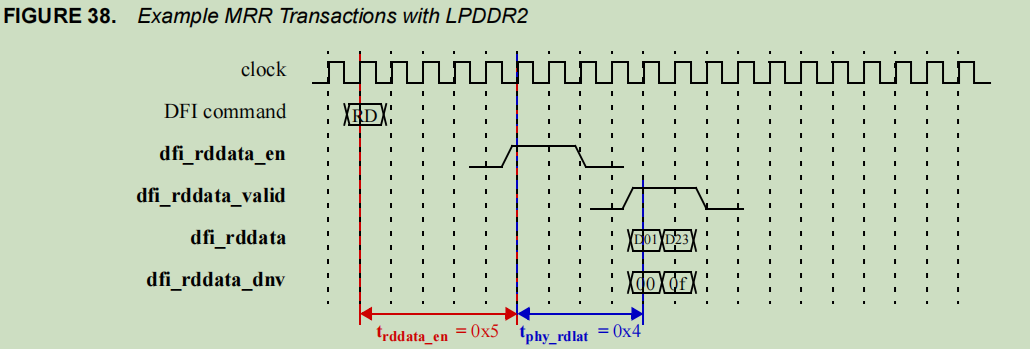

上图表示一些DRAMs定义了模式寄存器读取(MRR)的事务类型。从DFI的角度来看,模式寄存器读取可以像任何其他读取命令一样处理,并利用相同的信号。

上图显示了dfi_rddata_en和dfi_rddata_valid的数据字之间的一对一对应关系;dfi_rddata_valid字不需要是连续的。

上图三个读取命令,在第二个和第三个命令之间有一个间隔。

读取命令和写取命令的DFI定时参数将从第二个命令的第二个刻度开始引用,其方式与JEDEC LPDDR4引用RL和WL相同。

DBI

-

DBI是用于读取数据传输的可选DFI特性。只有当在DFI中支持DBI时,才需要phydbi_mode参数。如果系统中需要DBI,则必须接收DRAM DBI输入,并用于选择性地反转读取命令的数据

-

PHY捕获DRAM读取的DBI数据,并使用dfi_rddata_dbi信号通过DFI将数据传输给MC。

-

dfi_rddata_dbi信号的时序与dfi_rddata信号的时序相同,并且DBI数据与相应的dfi_rddata总线同步发送。

-

对于频率比系统,dfi_rddata_dbi信号被扩展,类似于dfi_rddata,每个相位定义一个信号。例如,在一个4:1的频率系统中,DBI信息通过dfi_rddata_dbi_w0、dfi_rddata_dbi_w1、dfi_rddata_dbi_w2和dfi_rddata_dbi_w3信号进行传输。

link ecc

Link ECC是一个可选的DFI特性,用于读取数据传输。当DFI中支持Link ECC时,需要使用phylinkecc_mode参数。如果MC正在处理link ECC操作,则DRAM将通过dfi_rddata_dbi信号上的DFI总线传输写ECC。在link ECC模式下,PHY只需要通过PHY传输读取的link ECC。

在LPDDR5中,链路ECC和读取DBI &链接ECC和读取数据复制功能是互斥的。需要遵循JEDEC spec

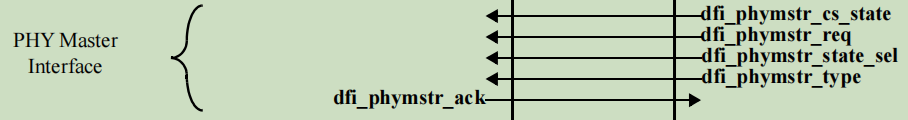

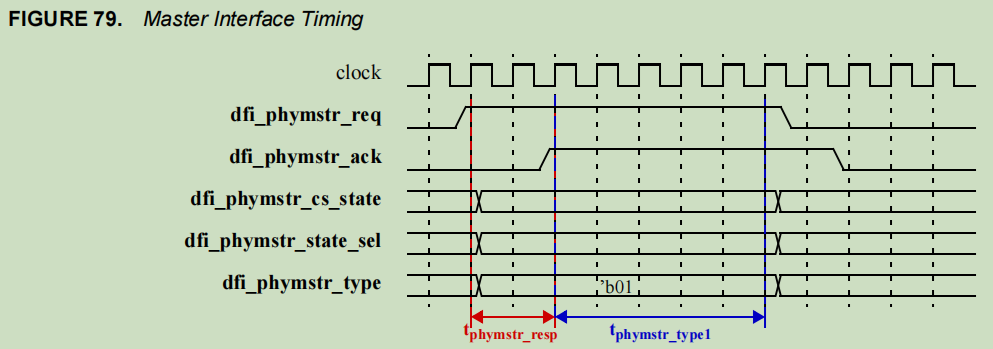

phy master

PHY master接口提供了一种PHY来控制DFI和DRAM总线的方法,在DRAM处于定义的状态时。当PHY控制总线时,通过访问或不访问DRAM,它将执行独立于MC的所有操作。

当PHY在控制期间,DFI总线必须保持空闲,除了MC可以发送内存刷新,因为MC将维护系统的内存刷新时序。 PHY将在将DFI总线释放回MC之前,负责将所有刷新信息转发给dram。

DFI的sepc没有规定任何training方法,但是training可以通过PHY master接口的方法 在PHY完成

当PHY请求控制总线时,为了inactive chip select (cs没有选中的chip?),MC应遵循以下准则:

- Maximum power saving mode(MPSM)或者deep power-down (DPD)mode

MC不应不必要地将内存从低功耗模式带到IDLE或SREF状态。在MPSM/DPD模式下,memory 的内存内容可能不会由DRAM进行维护。MC应将内存保持在当前状态。 - 没有初始化的memory

内存应该保持未初始化,直到系统确定。 - chip select that unpopulated(未填充)或者powered off

chip select应该保持off-line 直到系统确定

由于 dfi_phymstr_req/dfi_phymstr_ack信号是只有1bit,并且PHY要求MC不发出acknowledge 直到所有chip selects都在一个请求的状态,所以在acknowledge发出之前需要经过很长一段时间。

这对于未初始化的芯片选择或在MPSM或DPD中选择的芯片选择尤其如此**,需要一个具有完整初始化例程的软件干预**。

这可能会导致违反tphymstr_resp参数。系统违反tphymstr_resp的行为依赖于系统控制,系统的行为超出了本文档(DFI)的范围。

使用此接口的步骤如下:

- PHY断言dfi_phymstr_req信号以及dfi_phymstr_cs_state和dfi_phymstr_state_sel信号,以便在交接总线之前向MC表达要求的内存状态。PHY驱动dfi_phymstr_type向MC指示它请求控制的时间长度。

- 如果dfi_phymstr_cs_state信号被清除,MC将DRAM置于dfi_phymstr_state_sel信号中指定的状态。

- 在大多数情况下,MC在dfi_phymstr_req断言的t phymstr_resp周期内断言dfi_phymstr_ack。如果dfi_phyupd_ack、dfi_lp_ctrl_req或dfi_lp_data_req与dfi_phyupd_req一起活动,则授予例外。

- MC在dfi_phymstr_req信号采样时取消dfi_phymstr_ack信号。如果PHY在断言dfi_phymstr_ack信号之后的tphymstr_typeX周期内(其中X是dfi_phymstr_type信号的值)没有取消断言dfi_phymstr_req信号,就会发生DFI协议违反。

- PHY必须将DFI总线的控制权返回给MC,DRAM与它接收到的状态相同,包括内存的状态。此外,必须关闭所有memory pages,并且刷新计数必须与MC刷新计数对应。

刷新是MC唯一可以在phy master状态发的命令。

为了满足DRAM刷新的时序要求,PHY和MC应该遵循以下步骤: - MC行为:

MC发送刷新命令到DFI总线

MC必须保持满足所有刷新的时序要求

MC会考虑到满足所有DRAM刷新时间的PHY延迟(tphymstr_rfsh参数)。 - PHY行为:

PHY会在tphymstr_rfsh周期内生成对DRAM的刷新命令。

PHY确保满足所有DRAM刷新时间。

PHY确保所有DRAM刷新时间在将控制权返回给MC之前已经执行。

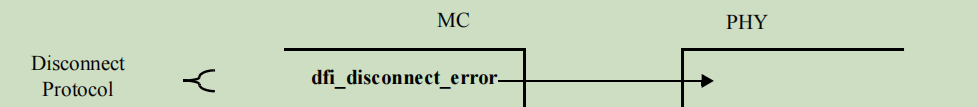

disconnect

DFI 定义了MC和PHY之间的几个接口的握手,DFI disconnect protocol可以用于中断两个DFI信号之间的握手

一些可能导致disconnect的情况是:

- 系统必须继续全面操作的高优先级操作

- 即使系统停止全面操作,也要响应错误条件

- 如果系统没有在合理的时间内断开连接,就会发生的时序或其他此类的violation

当这种情况发生时,断开的时间应该相对较短,具有可预测的断开时间,使系统处于已知状态

当发出断开连接时,用户将指定断开连接是否会使系统处于完全运行状态(QOS),或者系统是否不再保证可运行(error condition)。该信息通过dfi_disconnect_error信号传递。

- 使用disconnected协议的MC与一个更早DFI版本的PHY会违反更早版本的协议,并产生不可预测的错误。

- 对于DFI4.0版本的MC与一个更早版本的PHY,MC应该执行disable disconnect协议的方法。

- 与早于DFI 4.0的MC一起工作的PHY不会检测到断开连接,因此不会有任何问题。

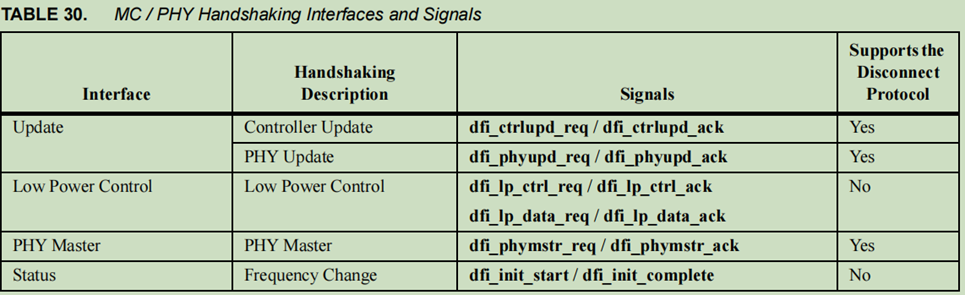

DFI定义了如下几组握手信号。Disconnect 协议定义了8对时序参数(t * disconnect_error),都表示的最大值。

Ctrlupd\phymstr\phyupd

对于update interface 有两种握手,controller-initiated 和 PHY-initiated。对于这两种,都是只有PHY可以disconnect握手。虽然有时间参数来定义最大握手时间(tphyupd_typeX,tctrlupd_min),但在某些情况下,延迟可能会长得令人无法接受。

为了打断握手,MC将违反协议来取消dfi_ctrlupd_req或者dfi_phyupd_ack信号。这两个信号的取消断言告诉了PHY MC要disconnect握手。

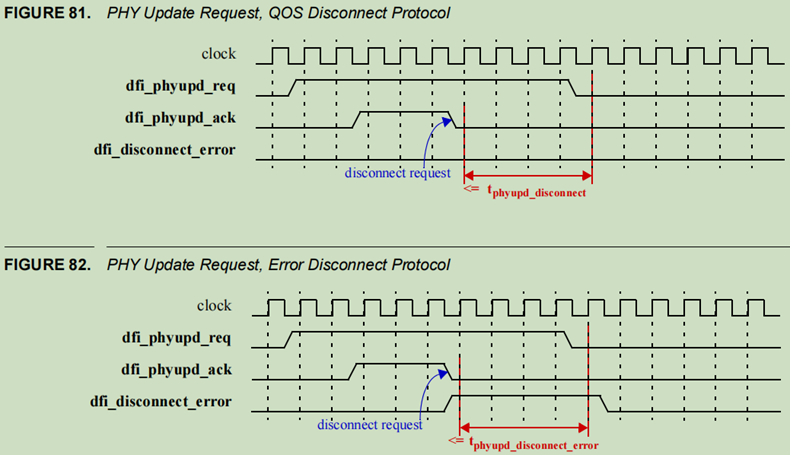

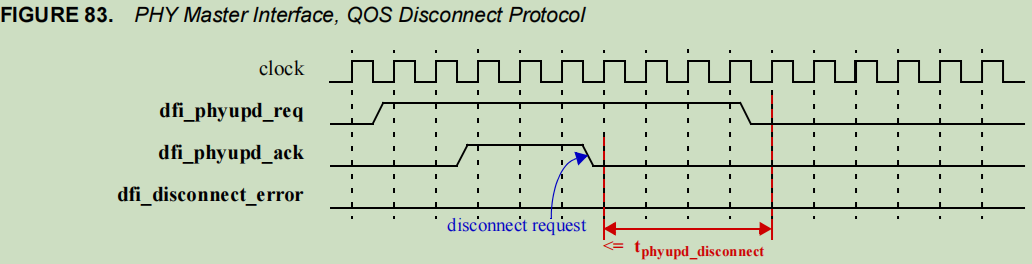

Dfi_disconnect_error信号定义了disconnect 是一个error条件或者是一个QOS事件。当disconnect发生时这个信号的值决定了期望的系统行为:QOS \ error

如果dfi_disconnect_error信号被取消断言(QOS),则PHY必须在tctrlupd_disconnect或tphyupd_disconnect时钟中取消断言相应的信号(dfi_ctrlupd_ack或dfi_phyupd_req)。此时,PHY必须完全正常运行。

如果断言dfi_disconnect_error信号被断言(error),PHY必须在tctrlupd_disconnect_error或tphyupd_disconnect_error时钟周期内取消相应的信号(dfi_ctrlupd_ack或dfi_phyupd_req)。在断开错误条件之后的PHY的状态由PHY定义,并应在PHY规范中进行说明。理想情况下,PHY在保留最多内存服务的边界上断开。

Phy mstr的接口和upd接口的disconnect行为类似:

DDR DFI接口协议所有的interface group 介绍完毕,如有遗漏欢迎补充~

3039

3039

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?