Verilog RTL 代码设计新手上路

做一个4选1的mux,并且进行波形仿真 和2选1的mux对比,观察资源消耗的变化

-

实验代码

-

RTL 视图

-

仿真波形

-

资源对比

2选1

4选1

-

实验结论

通过实验发现,4选消耗的资源更多。

编写一个8输入的优先编码器,然后编译,看RTL View

-

实验代码

-

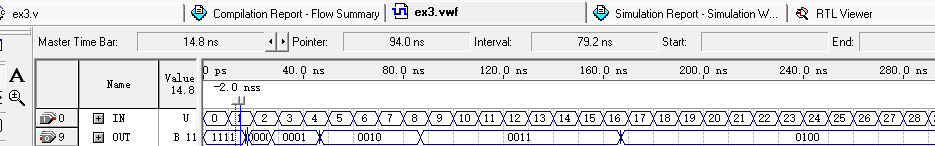

RTL视图

-

仿真波形

-

资源对比

4位优先编码器

8位优先编码器

-

资源对比

8位优先编码器消耗资源更多。

编写一个4-16的译码器,编译

- 实验代码

- RTL视图

- 资源对比

3-8译码器

4-16译码器

无符号加法器

- 4位输入4位输出

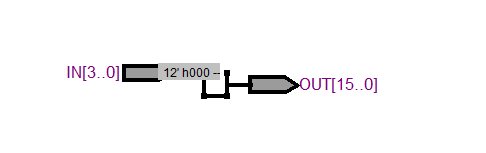

波形仿真

- 8位输入5位输出

实验代码

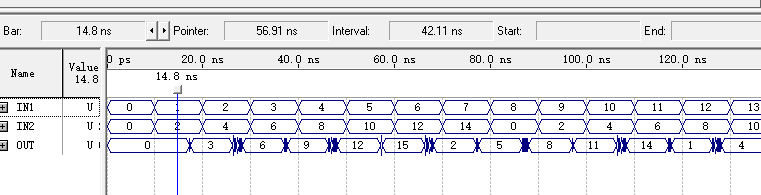

波形仿真

- 实验总结

4输入4输出的加法器在结果大于16的时候只能输出最后一位。

8输入5输出的加法器在结果大于32的时候输出结果就不正确。

8输入的信号,输出延时比较大。

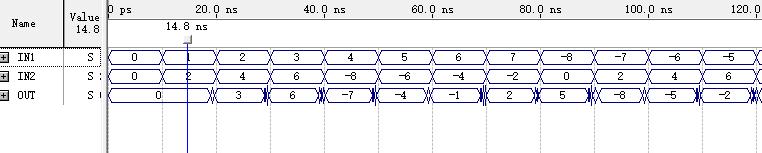

补码加法器

- 4输入4输出的补码加法器

实验代码

波形仿真

2. 8位输入5位输出的补码加法器

实验代码

波形仿真

3. 实验总结

与无符号加法器原理类似,只是换成了补码运算。

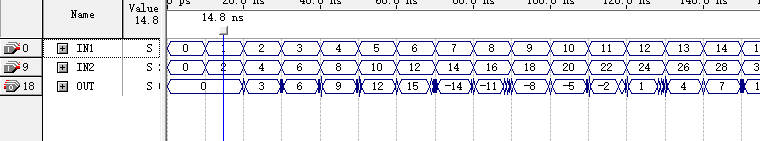

带流水线的加法器

- 8输入5输出的带流水线的加法器

实验代码

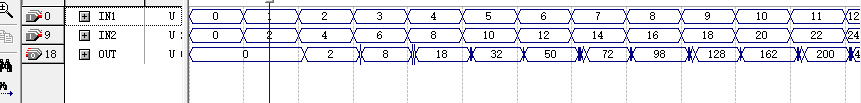

波形仿真

- 8输入5输出再加一级流水线

实验代码

RTL视图

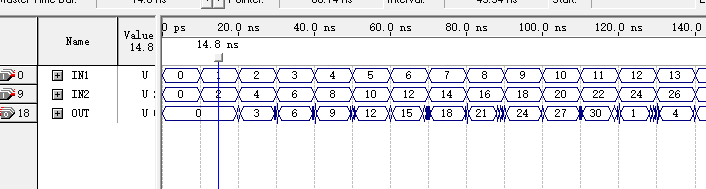

波形仿真

- 实验结论

与普通的加法器相比,带流水线的加法器增加了D触发器,减少了毛刺的产生。二级流水线的加法器,延时是一级流水线加法器的一倍。

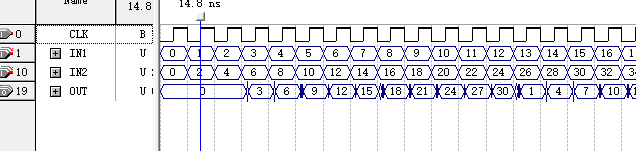

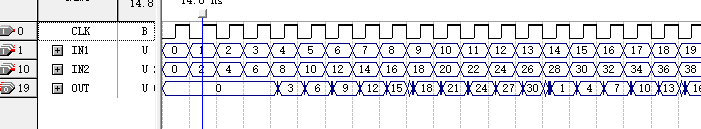

乘法器

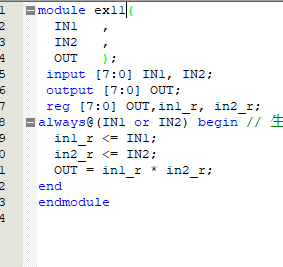

- 8输入8输出的乘法器

实验代码

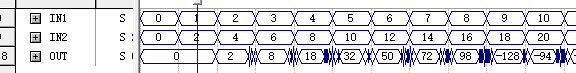

波形仿真

2. 带流水线的乘法器

实验代码

波形仿真

- 实验结论

8输入8输出的乘法器,毛刺较多。带流水线的乘法器毛刺较少,时延延后一个周期。

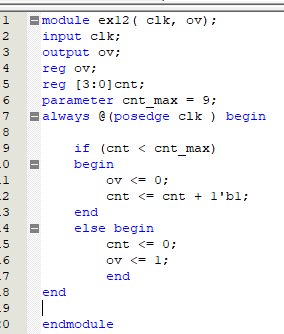

计数器

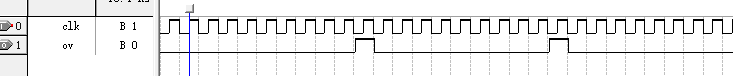

- 只有ov和clk的计数器

实验代码

仿真波形

- 设计复杂的计数器,带有多种信号,其中同步清零CLR的优先级最高,使能EN次之,LOAD最低。

实验代码

仿真波形

状态机

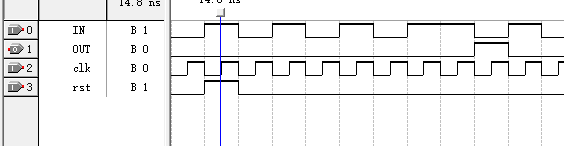

设计一个用于识别2进制序列“1011”的状态机

基本要求:

电路每个时钟周期输入1比特数据,当捕获到1011的时钟周期,电路输出1,否则输出0

使用序列101011010作为输出的测试序列

扩展要求:

给你的电路添加输入使能端口,只有输入使能EN为1的时钟周期,才从输入的数据端口向内部获取1比特序列数据。

实验代码

波形仿真

状态转换表

6557

6557

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?