AD19 PCB板完整绘制过程

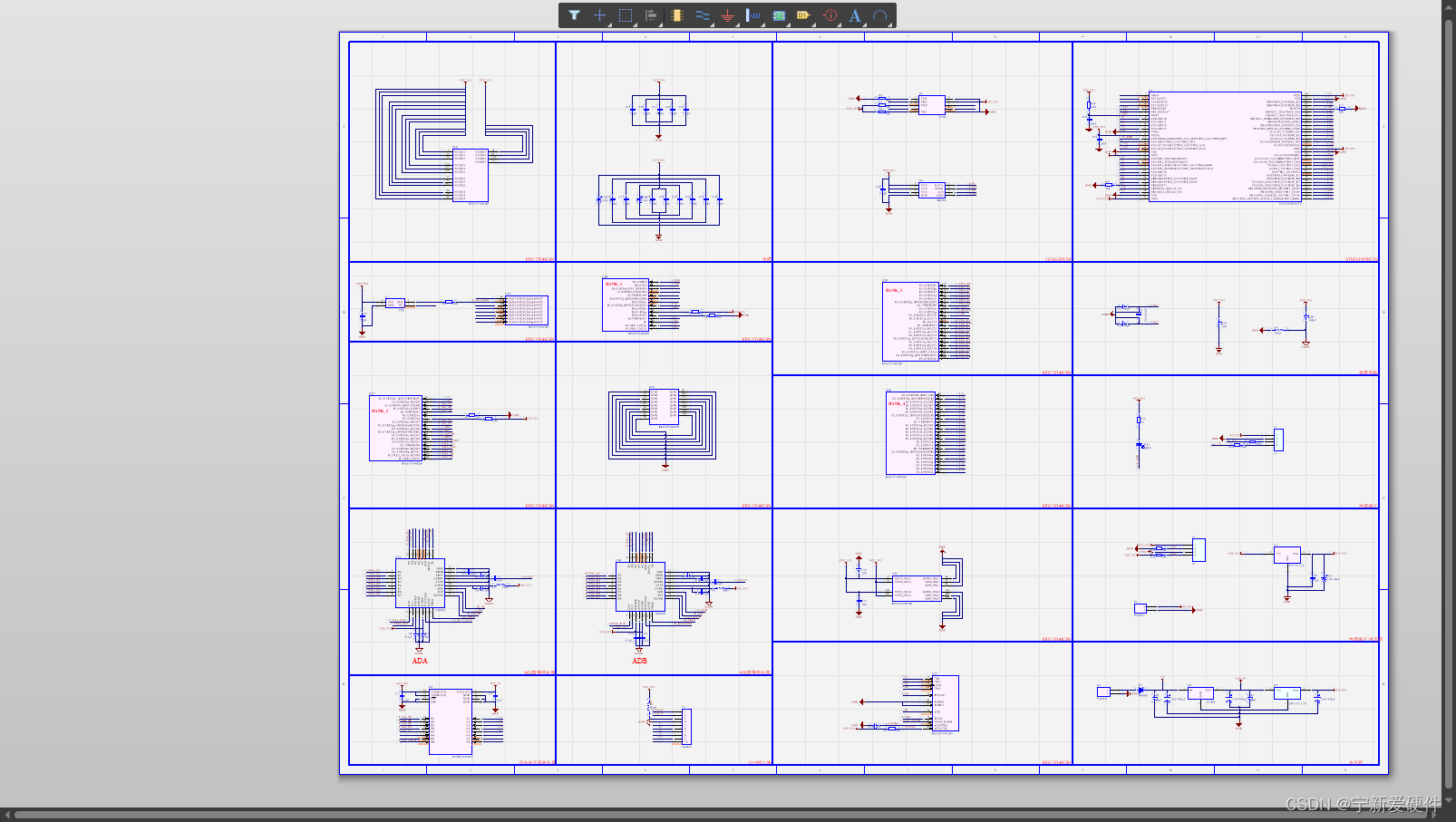

1、原理图导入

一个项目的电路原理图完成后,我们需要在Design选项下Update PCB Document xxxx.PcbDoC。

Fig 1

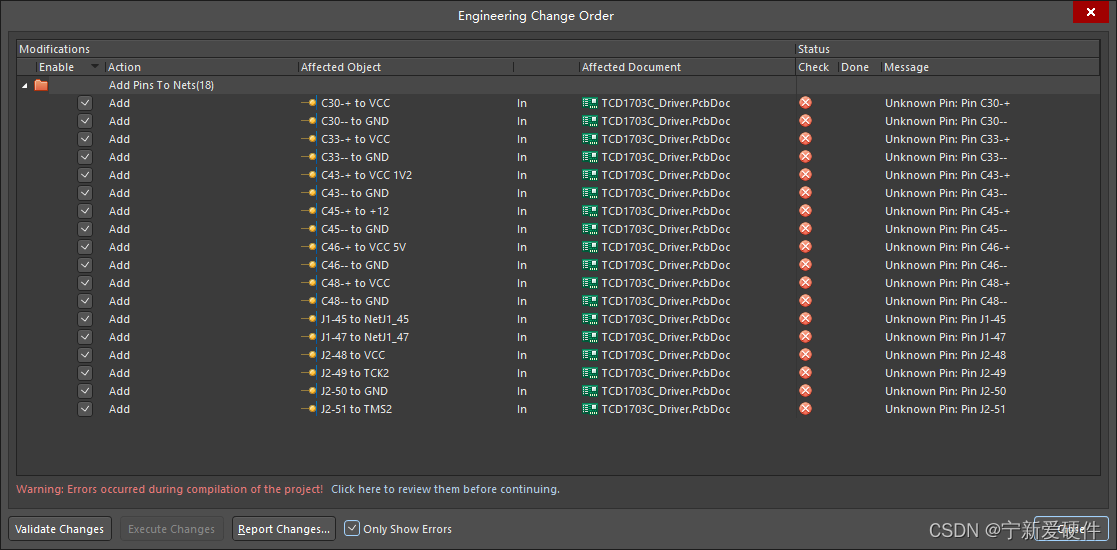

在更新的过程中,当Report Changes…时会出现很多错误,需要我们进行改正(可以点击Only Show Errors,只显示错误),例如

Fig 2

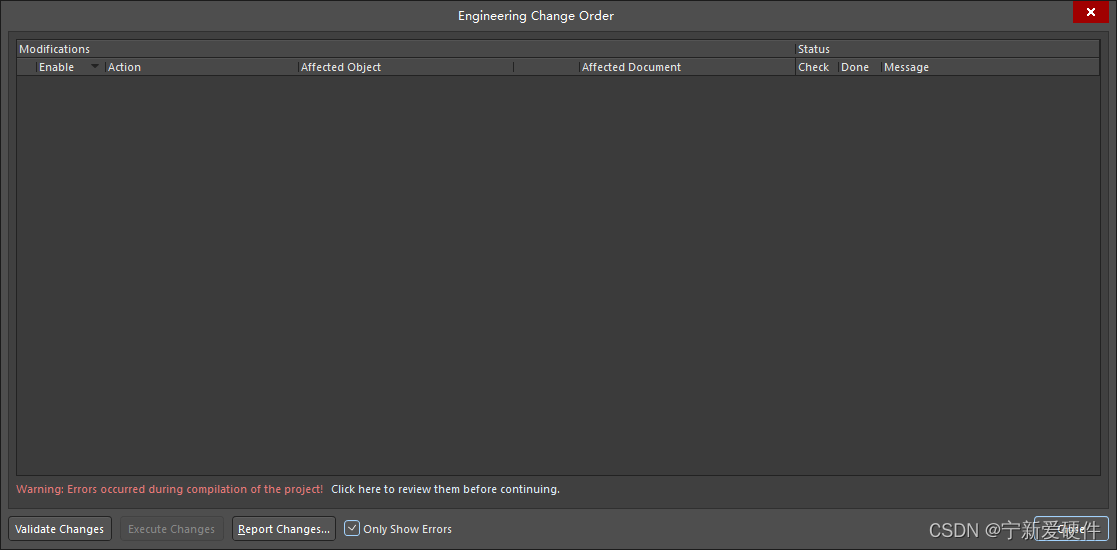

Massage中的信息会告诉我们错误的原因,对于Unknown Pin这类错误,一般有下面几点原因:(1)原理图元件没有添加封装;(2)原理图和封装引脚数个数不一致;(3)原理图引脚和封装的引脚代表字符不匹配(原理图的引脚是数字1,2,3…,而封装是字母A,B,C…),因此我们需要查看我们的封装和原理图,问题解决后,在信息栏是没有显示错误的(导入之后存在报错,取消不常用的DRC检测选项,DRC检查选项过多导致PCB设计布局布线的时候存在卡顿现象,可以只剩下电气性能的检查选项)。

Fig 3

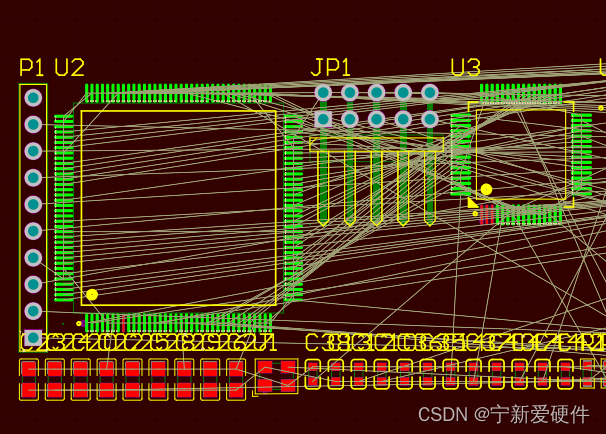

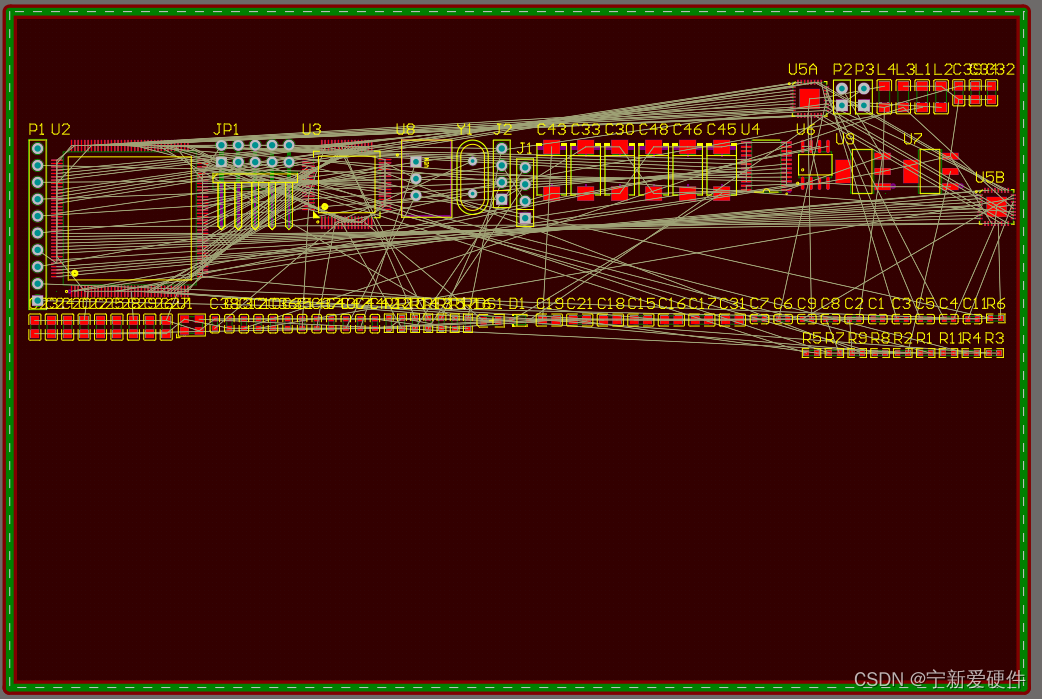

成功导入PCB后,可以在Tools中Component Placement选择适合自己的排列方式,在此次排版中选择Arrange Within Rectangle,最终的形式是这样的。

Fig 4

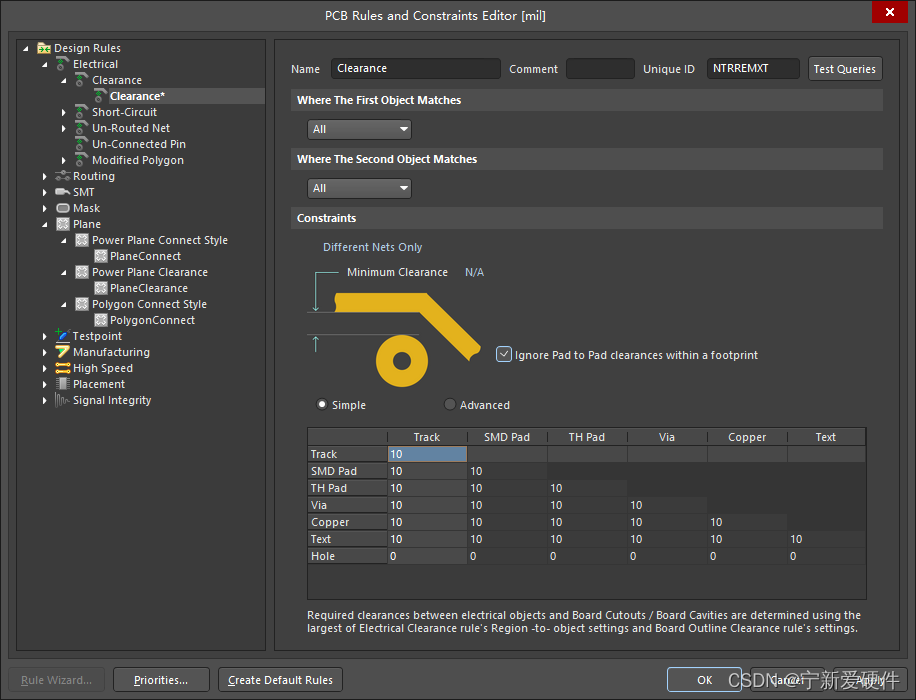

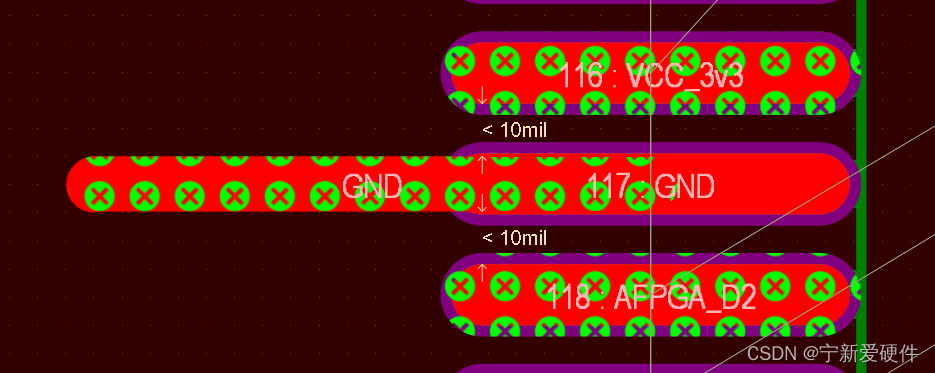

但是会出现图4这种情况(芯片引脚会有很多绿色的叉,标注引脚间距小于10mil),有些博主的解决办法是在Design中Rules做修改,将Design Rules中的Silk to Silk Clearance和Silk To Solder Mask Clearance取消勾选,但是问题并没有得到解决,最后通过查阅资料,发现在Electrical下Clearance中选择将Ignore pad to pad clearances within a footprint勾选,这种问题就会解决。

Fig 5

2、叠层设置

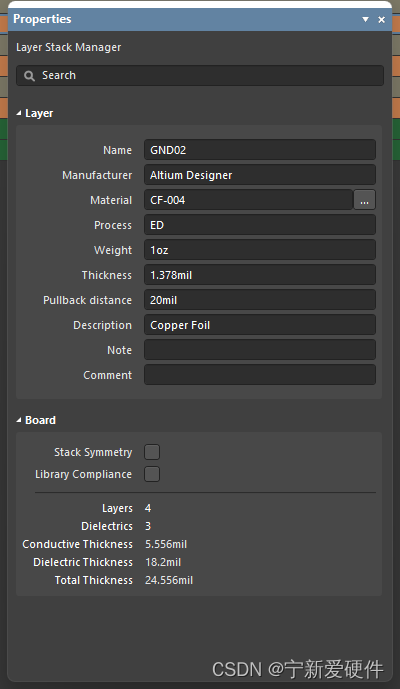

然后进行叠层设置,在Design中选择Layer Stack Manager…。点击Top Layer右键选择Plane,添加中间层,添加成功以后,命名是按照自己的习惯进行设置,为了降低平面边缘的辐射效应,在电源层和地层间要尽量满足20mil原则,因此点击Pullback distance,右键弹出Select columns,将里面的Pullback distance选项设置为可见并确定退出。继续在Properties中将自己命名的中间层的Pullback distance设置为2-3倍关系(电源层和地线层)。

Fig 6

设置完成后,我们可以看到会有自己命名的层。

Fig 7

3、封装间隙设置

有时候,导入的PCB会出现以下这种情况

Fig 8

对于这种情况是因为元件封装的间距小于10mil,但是在工程中设置的是10mil,因此需要在Design中的Rules做修改,如图所示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1045

1045

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?