以半加器为例,记录一下使用ISE仿真的步骤。

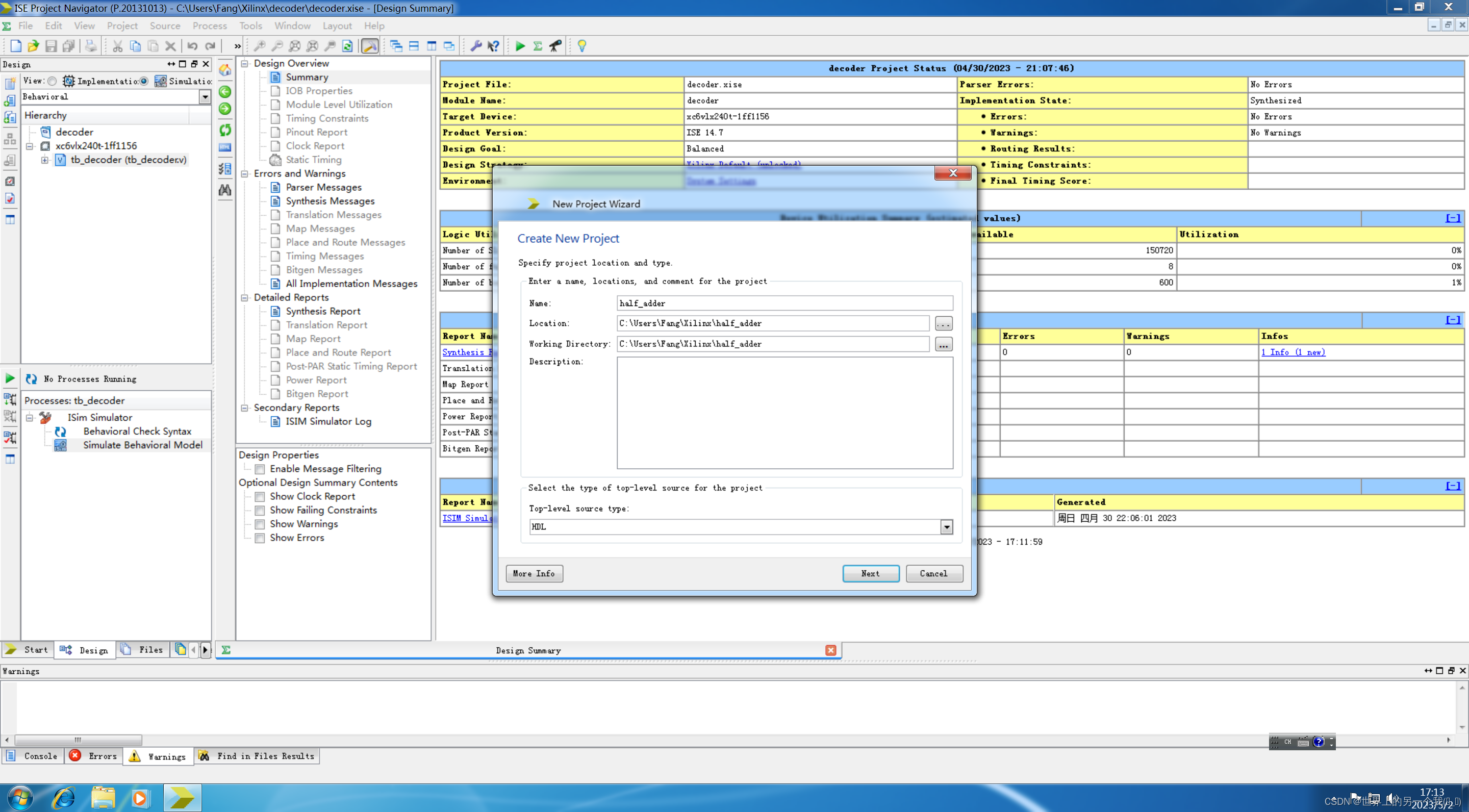

1、新建工程

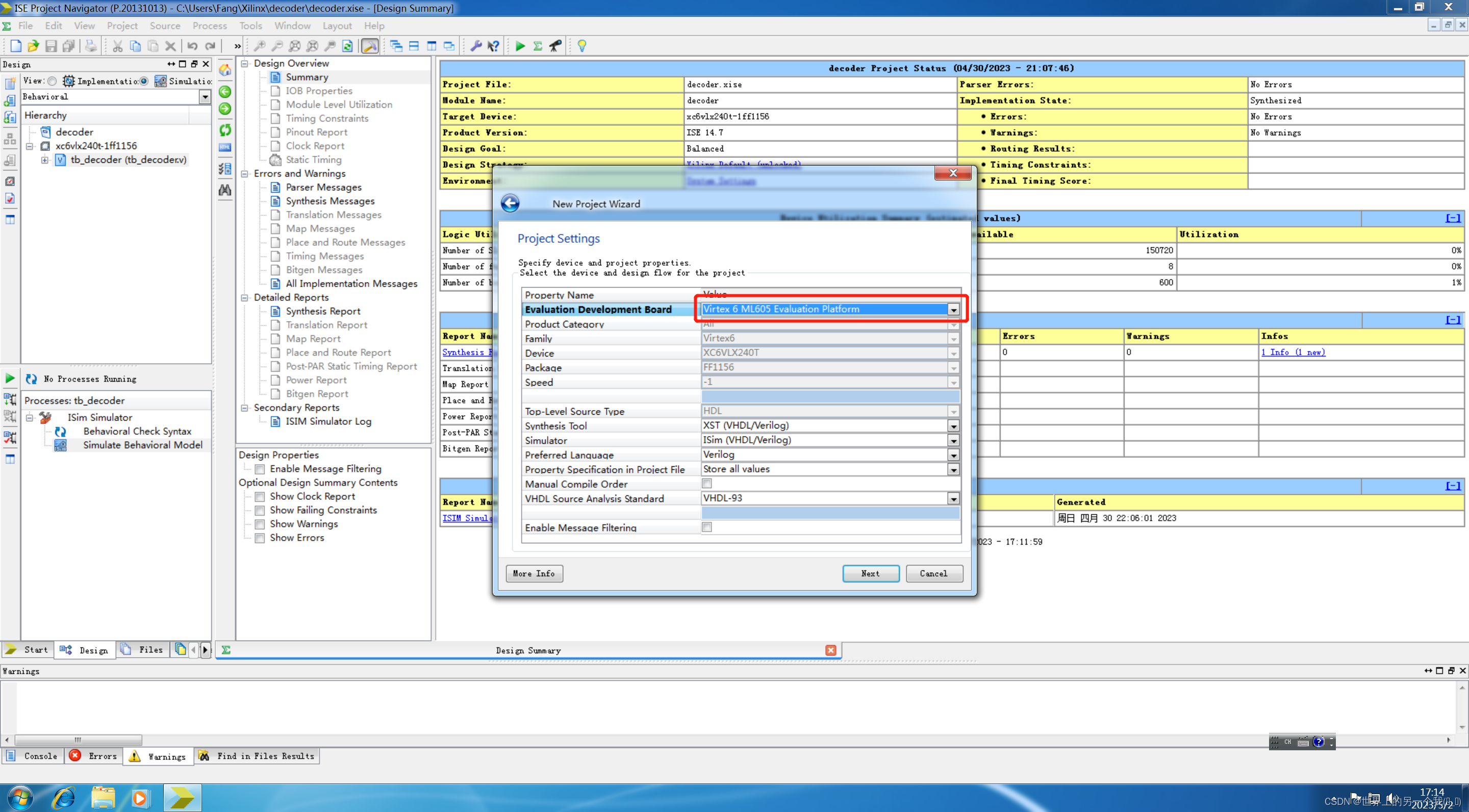

2、选择开发板型号,综合工具选择XST,仿真工具选为Isim

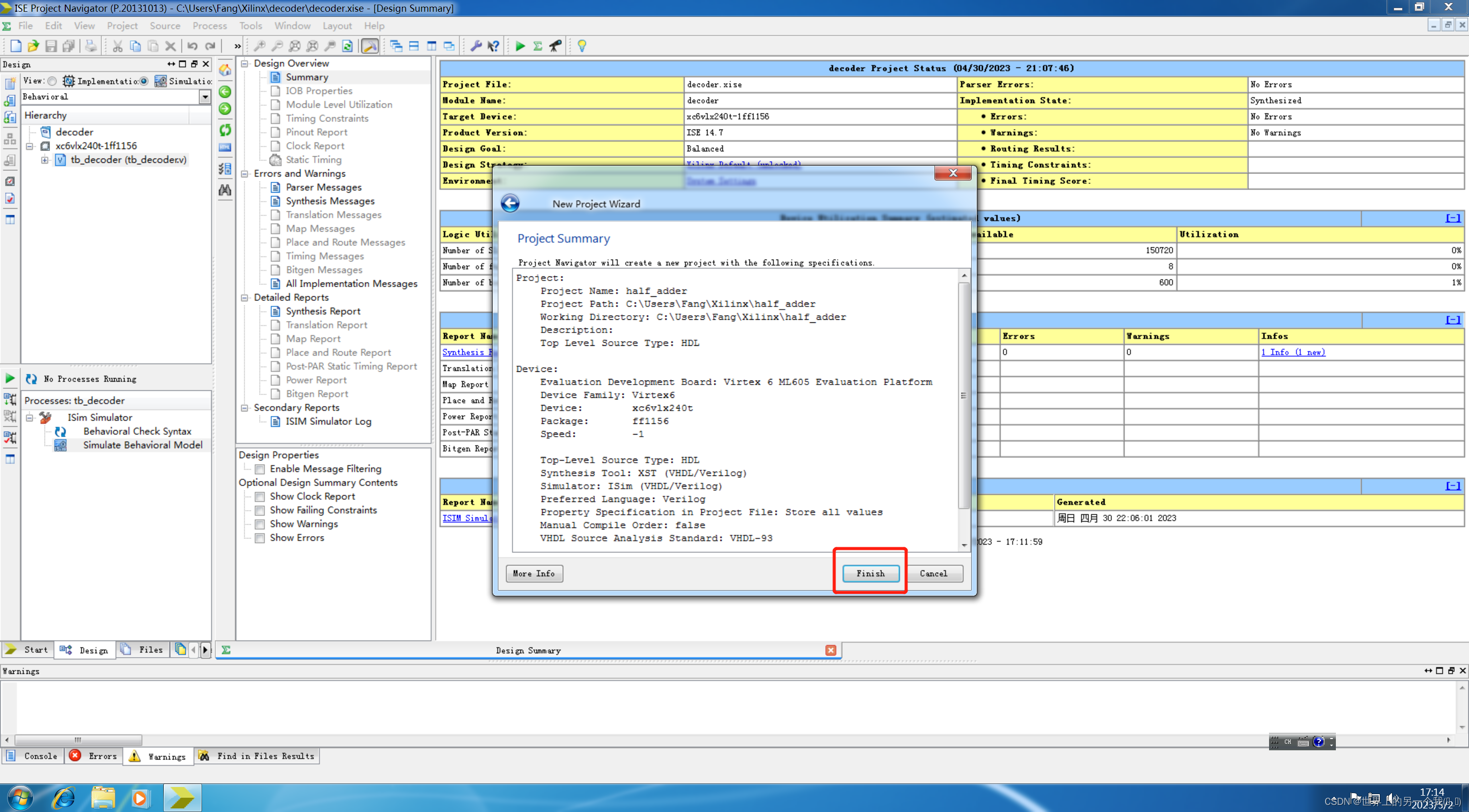

3、检查信息,没有问题点击finish

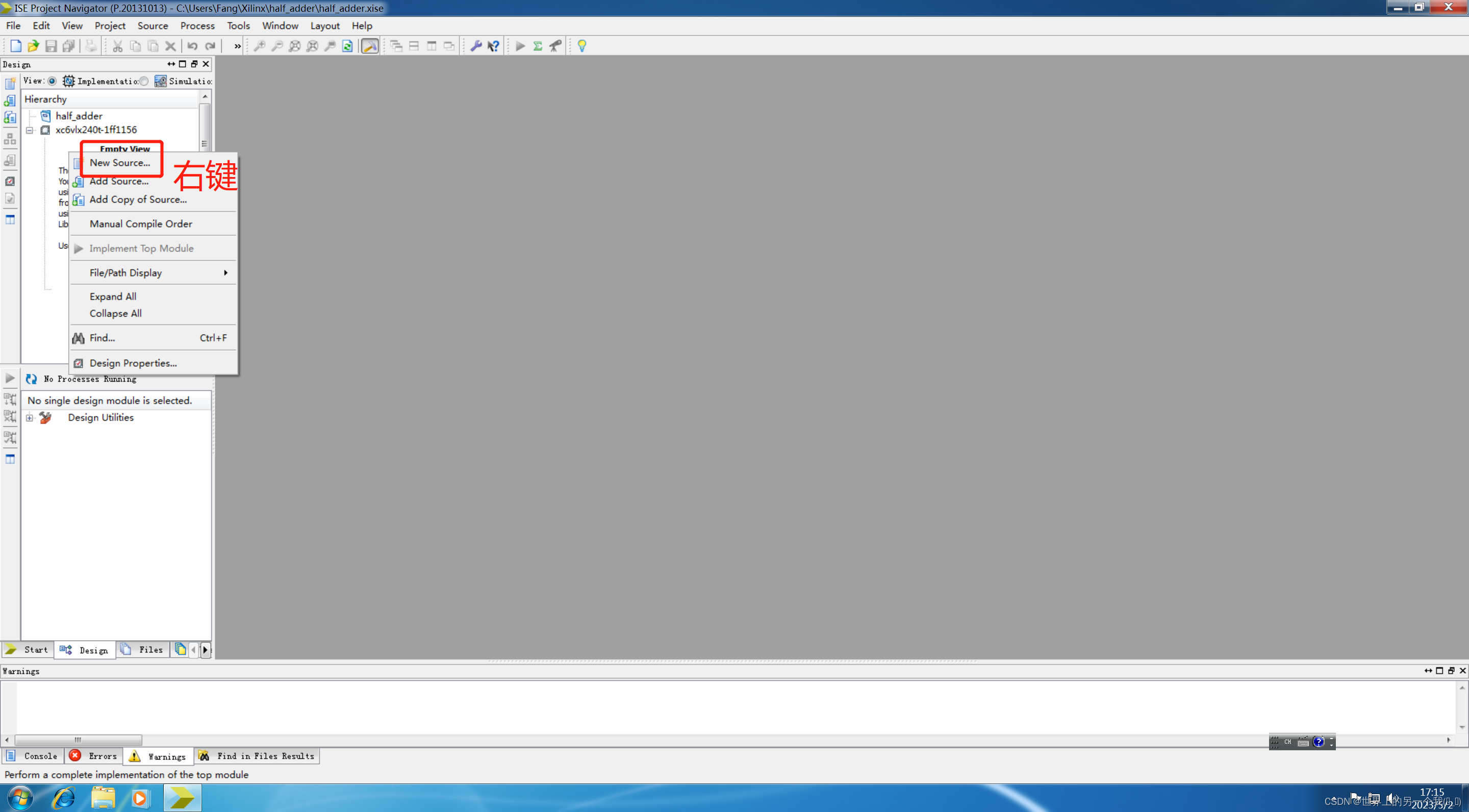

4、在代码管理区任意位置单击鼠标右键,选中new source

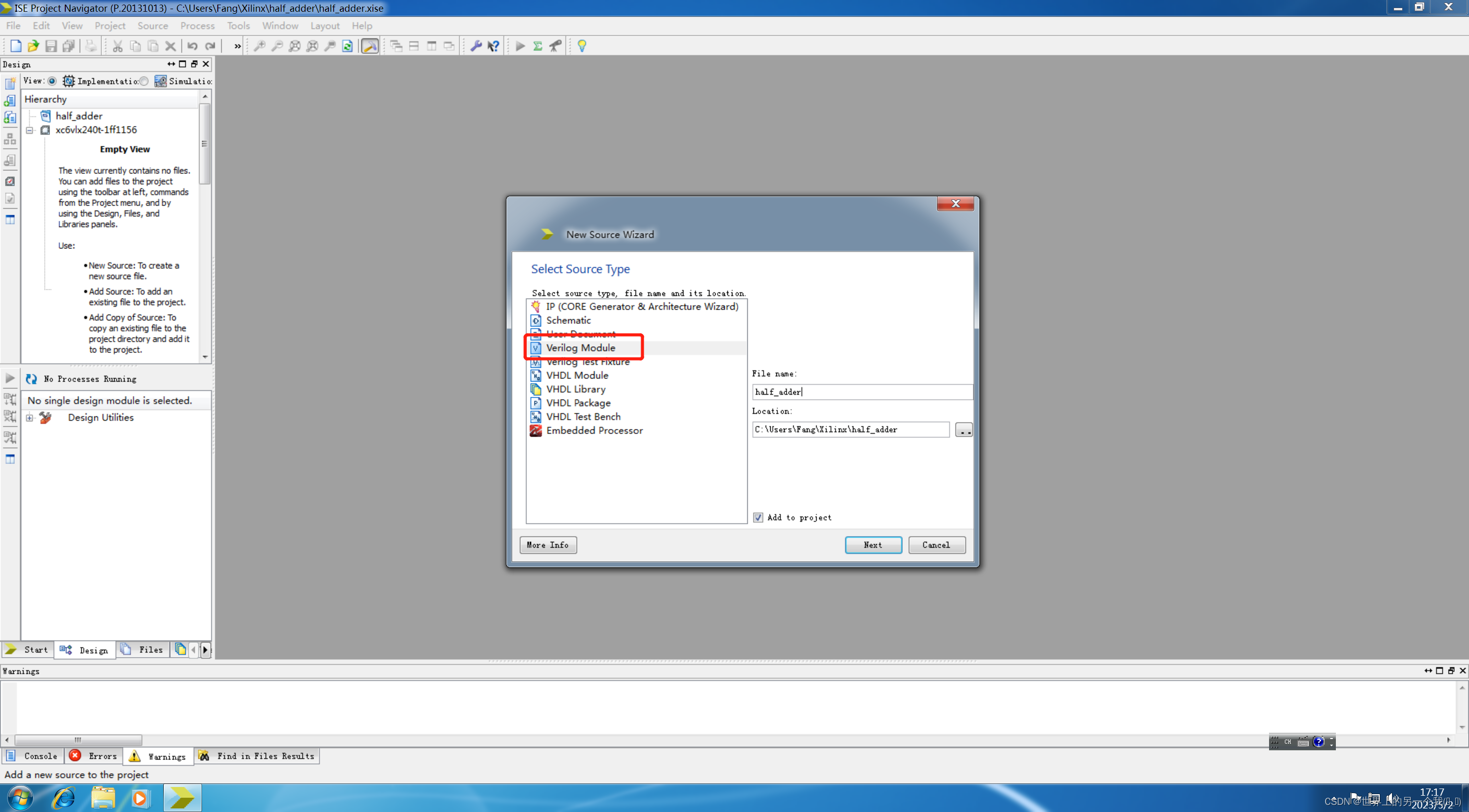

5、代码类型选择verilog Module,输入文件名称

5、代码类型选择verilog Module,输入文件名称

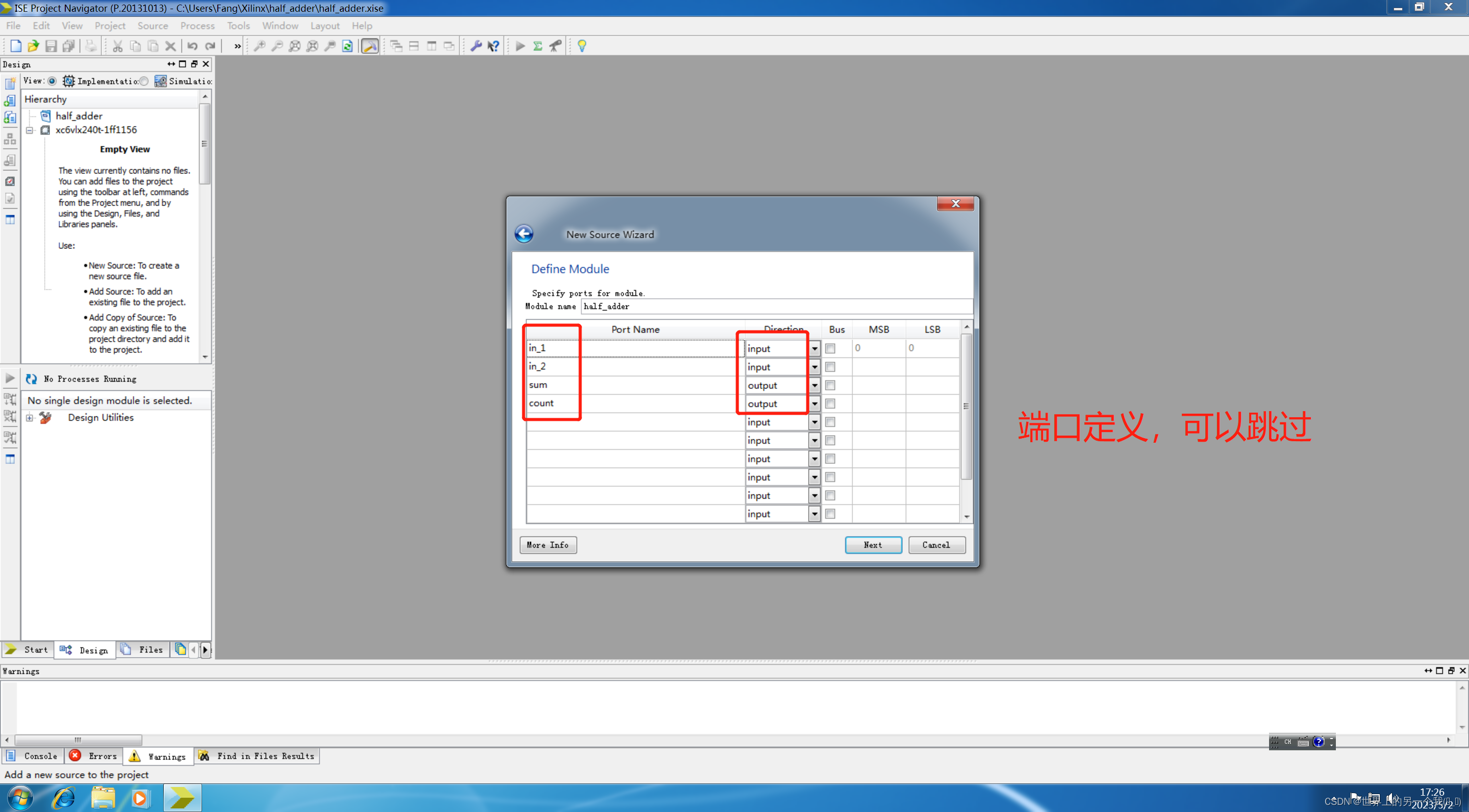

6、端口定义,"port name"表示端口名称,Direction表示端口方向,MSB表示信号最高位,LSB表示最低位,对于单位信号MSB和LSB可以不用写。

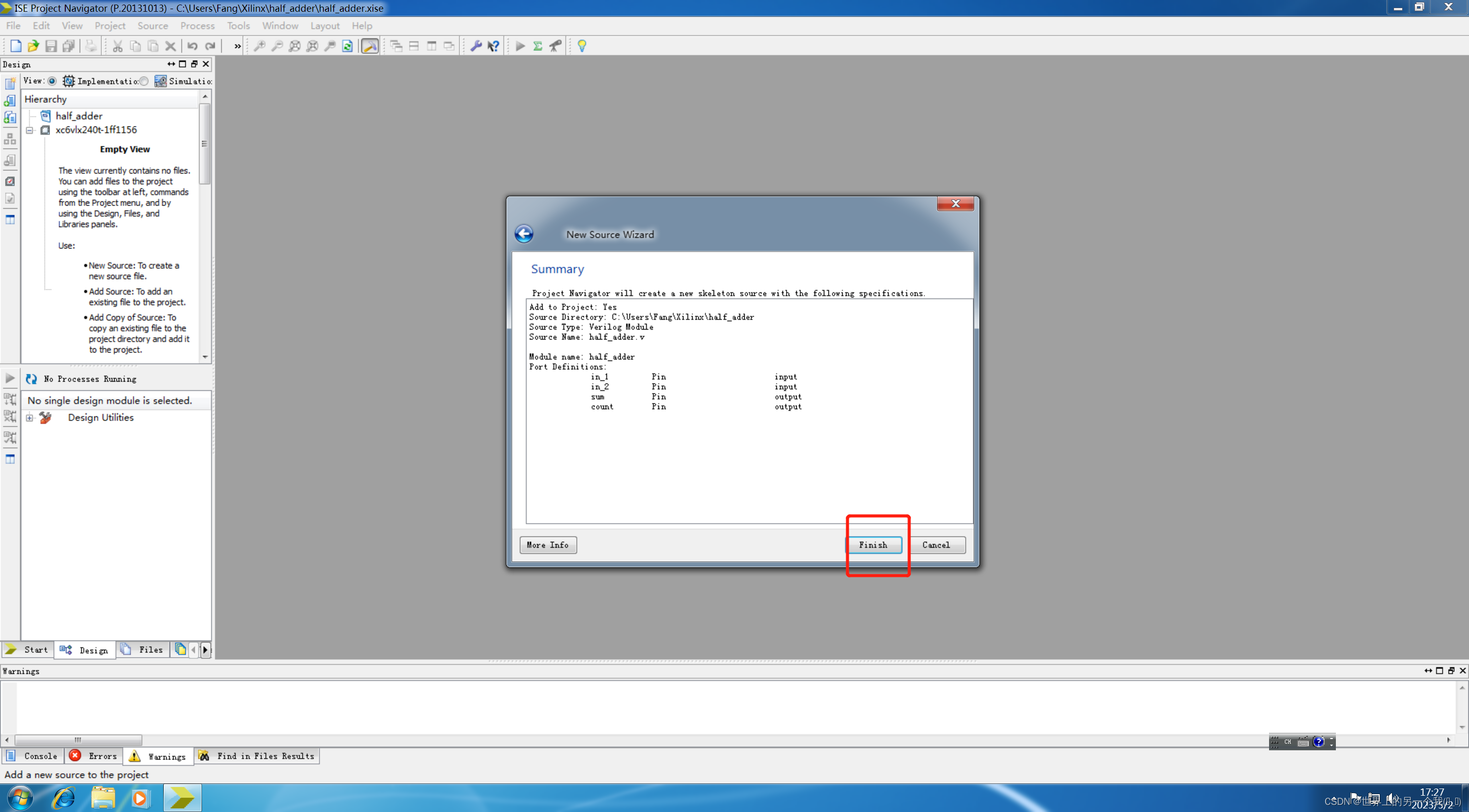

7、检查信息,没有问题点击finish

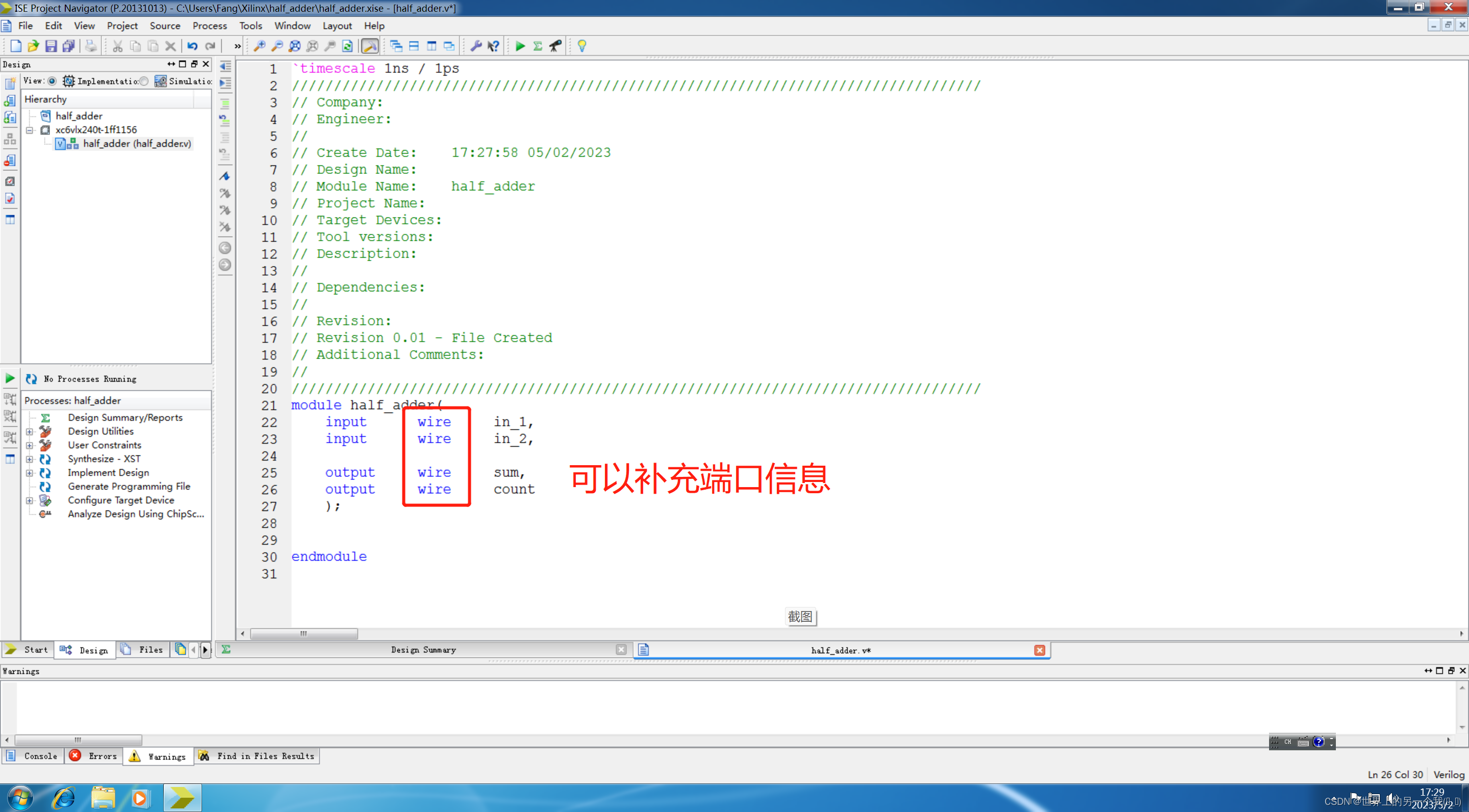

8、模块和端口定义会自动生成,对于未定义的端口信息可以修改或者补充

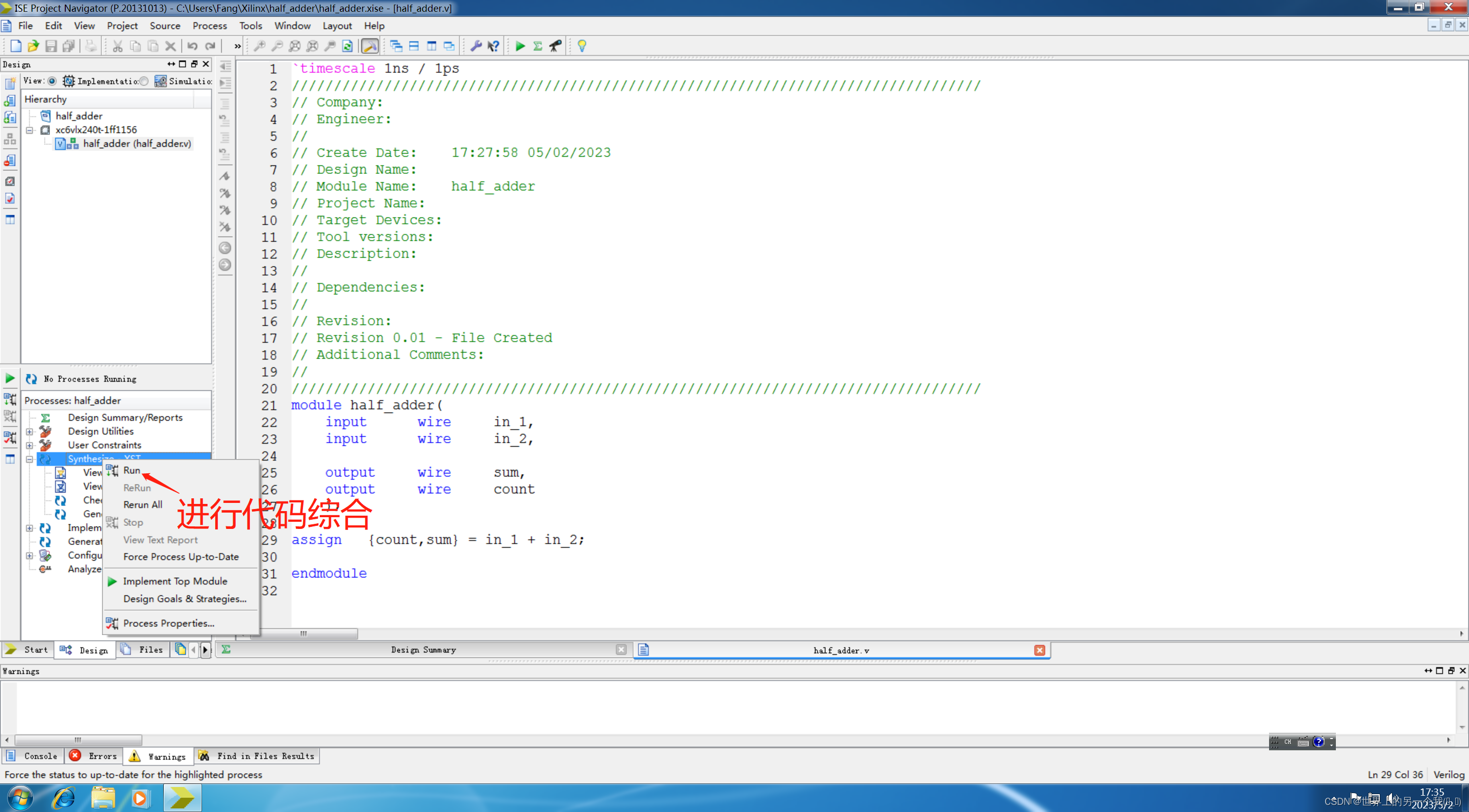

9、代码编写完毕,使用综合工具XST,点击如图所示位置进行代码综合

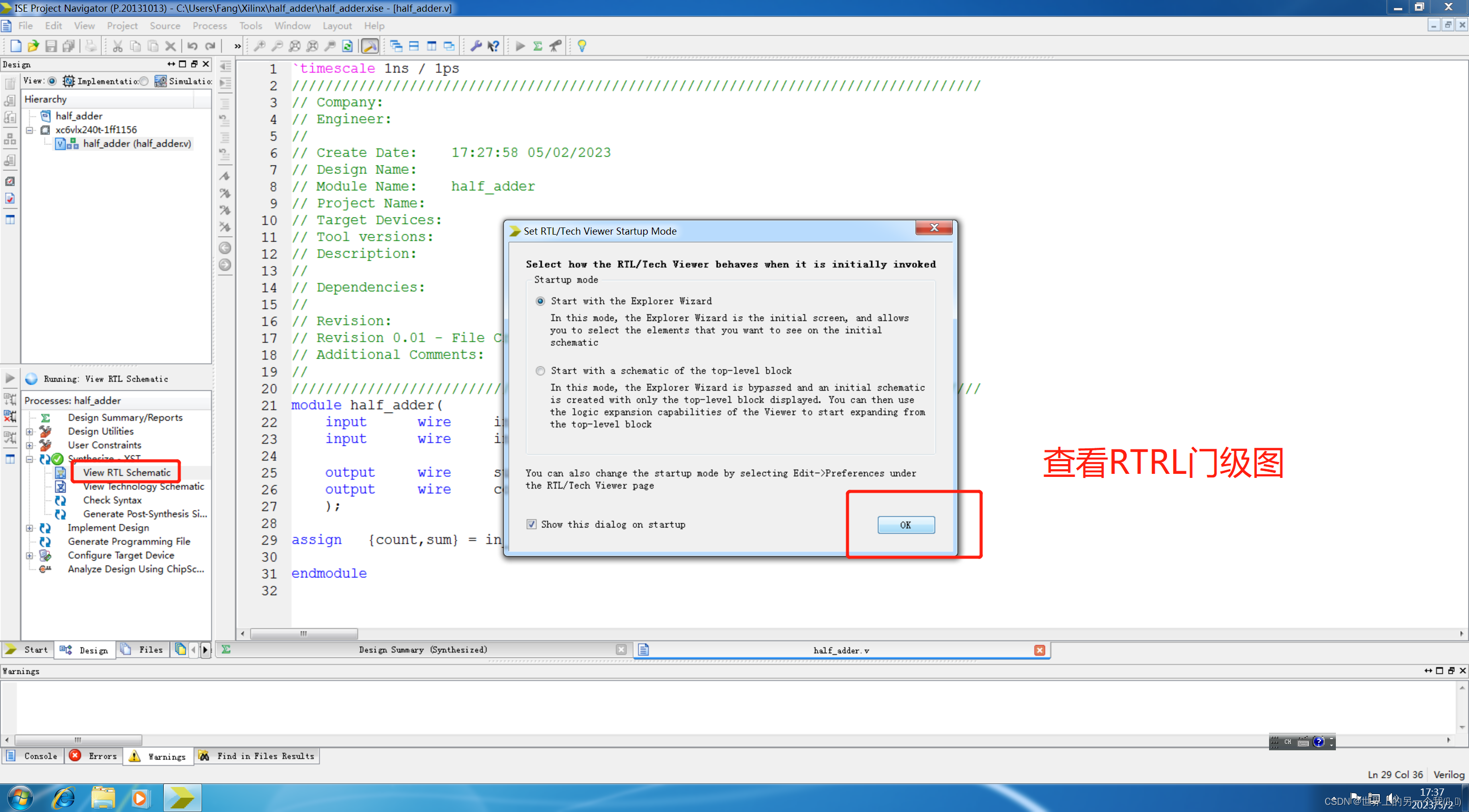

10、直接点OK

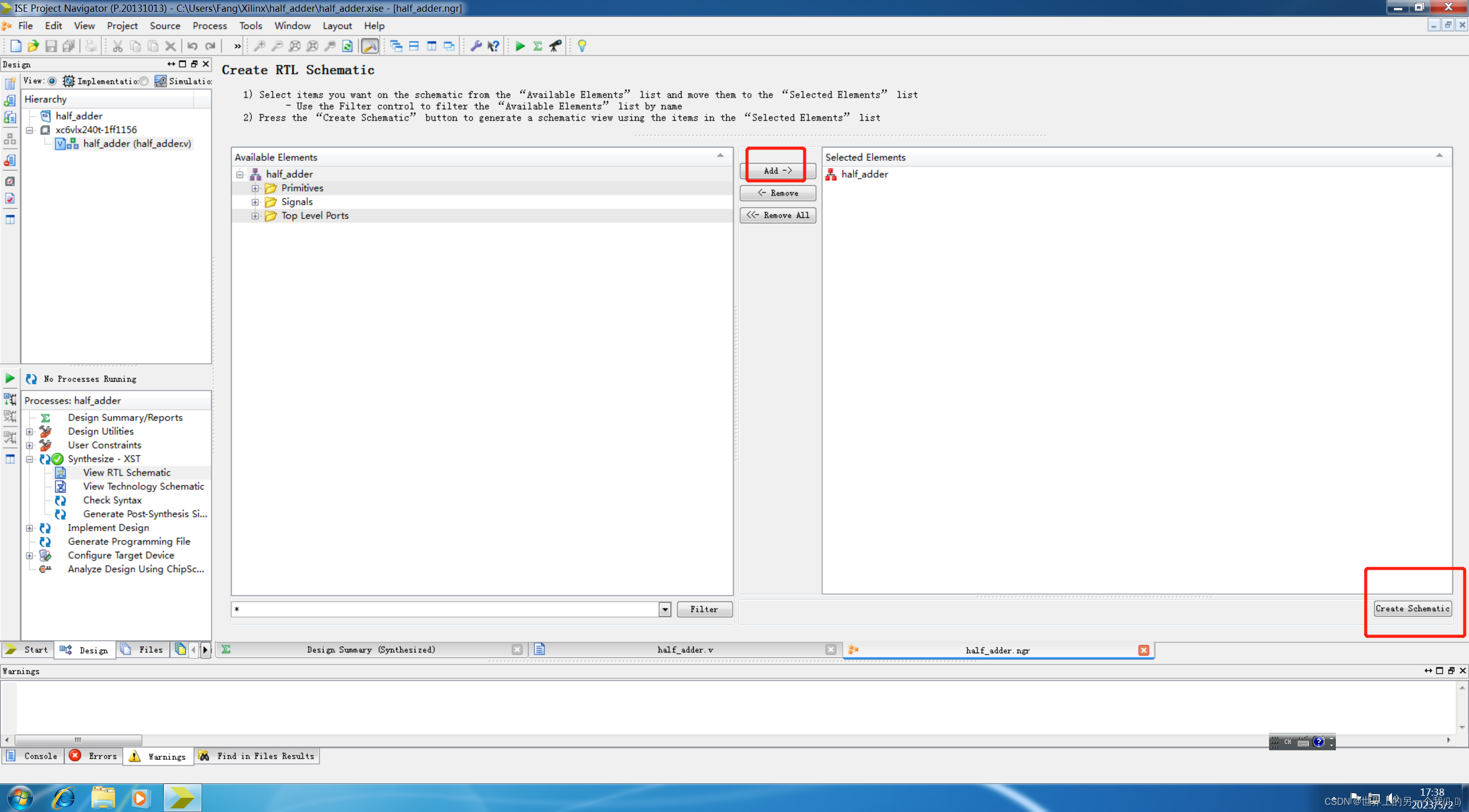

11、添加工程,然后点击创建原理图

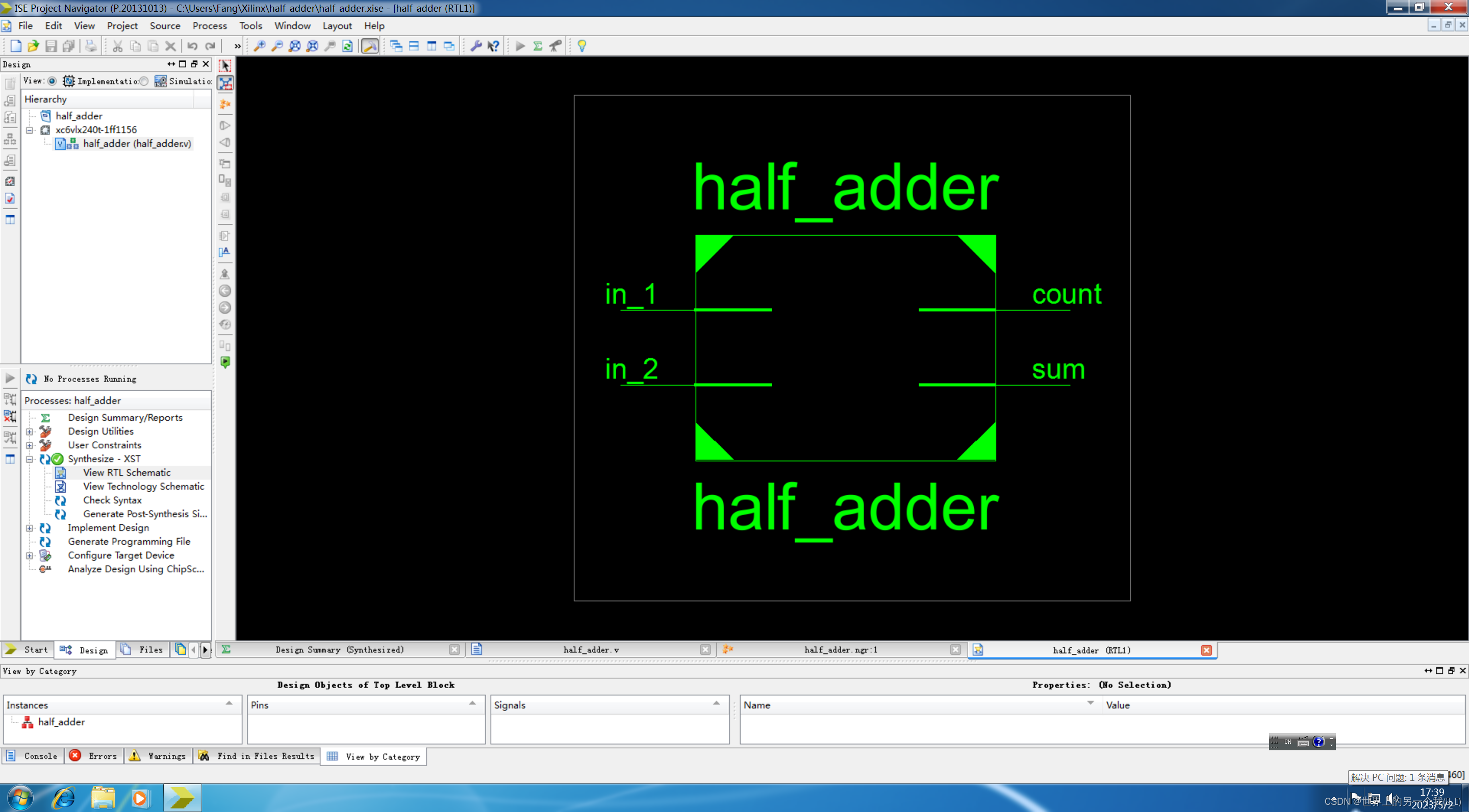

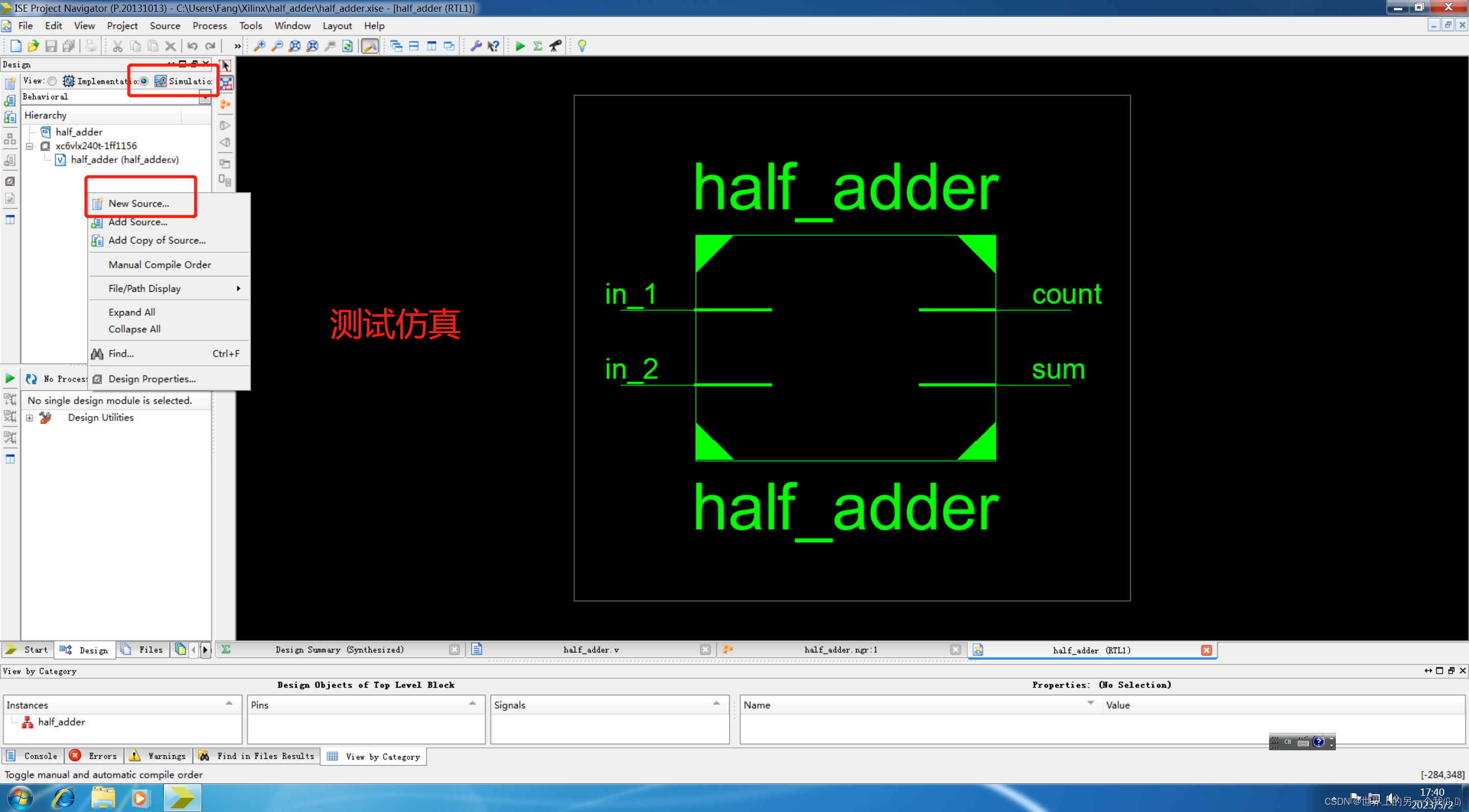

12、经过综合后的RTL级结构图

13、接下来进行仿真测试。在源码管理区将View设置成Behavioral Simulation,在任意位置单击鼠标右键,选择new source

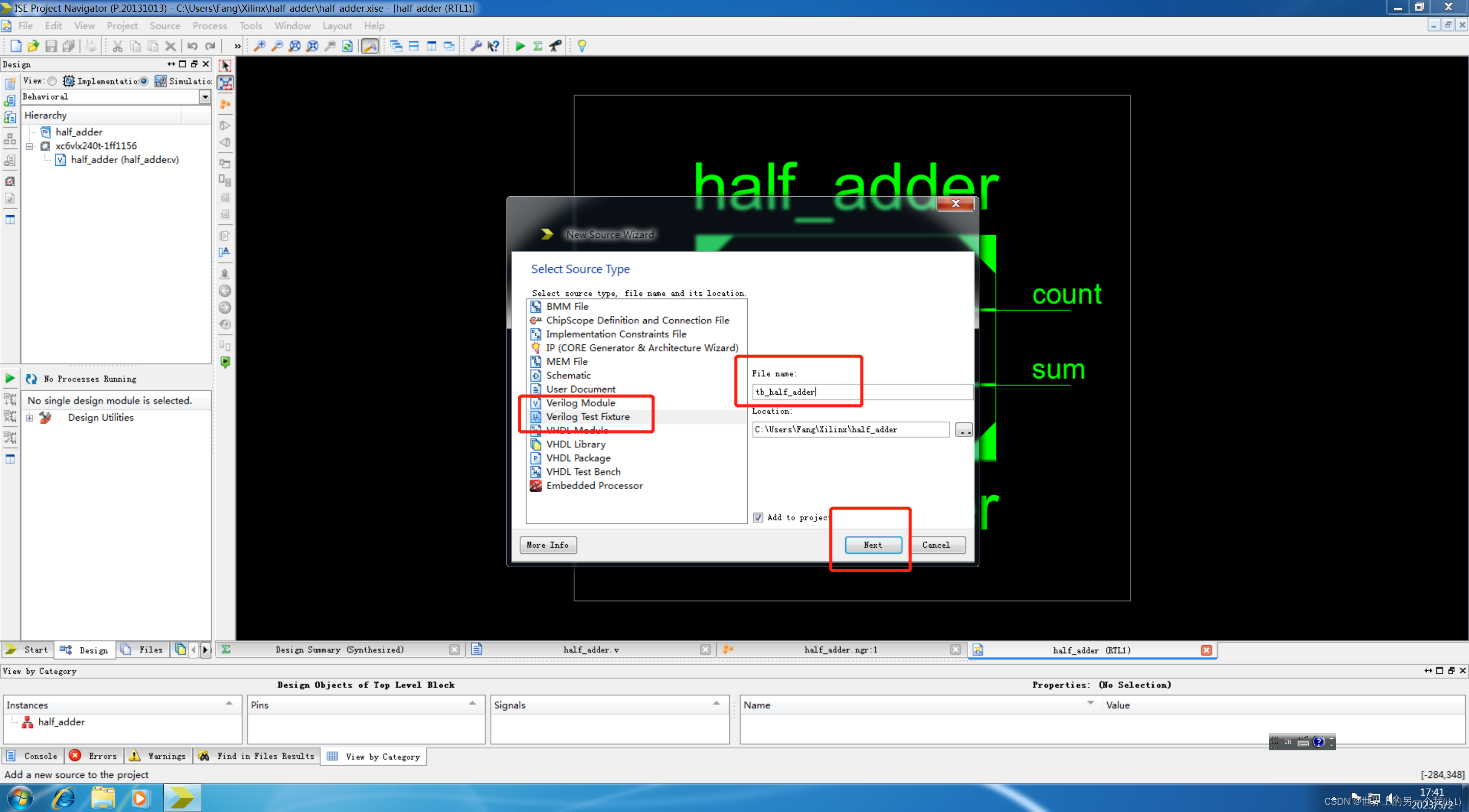

14、选择verilog test fixture,输入文件名

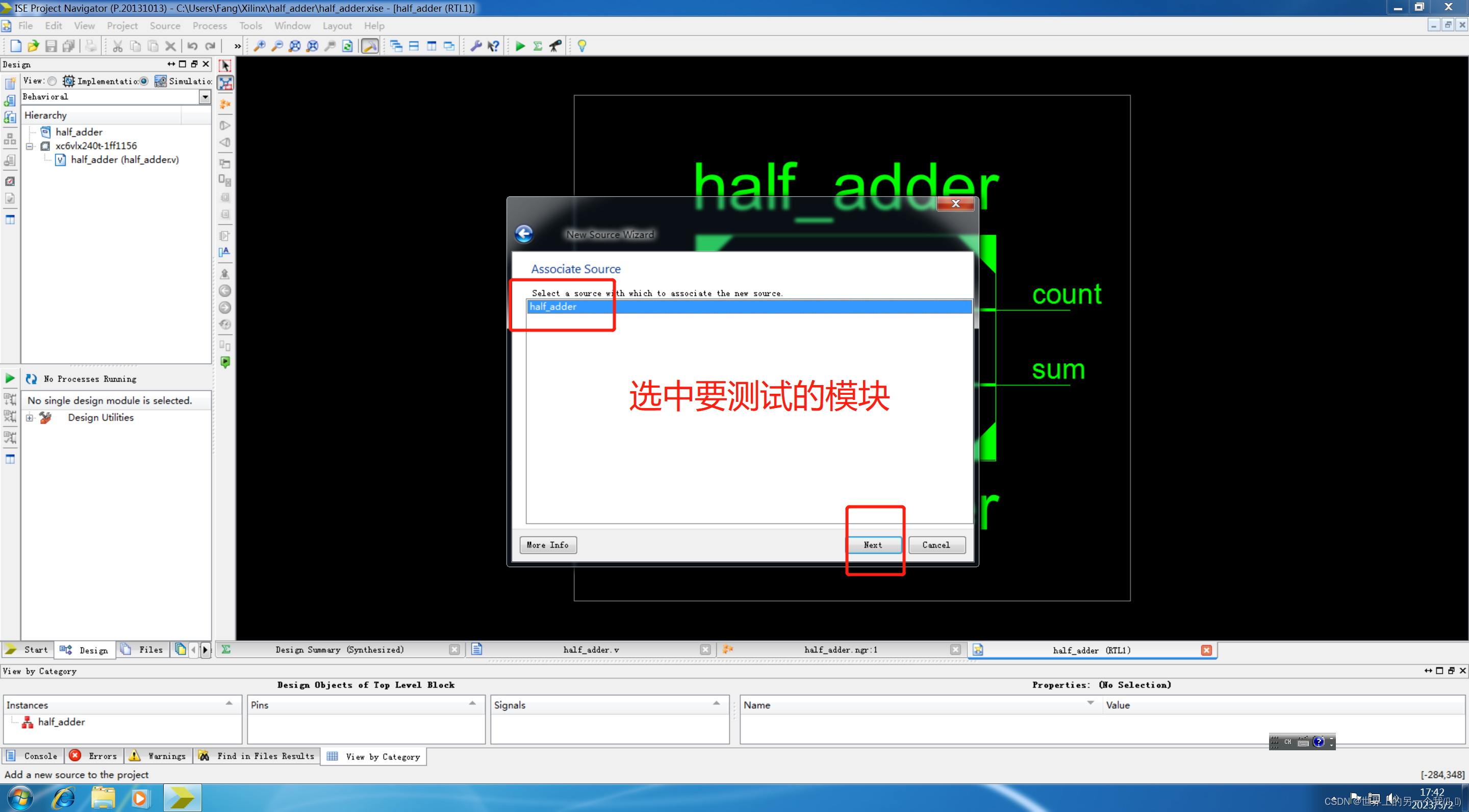

15、选中要测试的模块

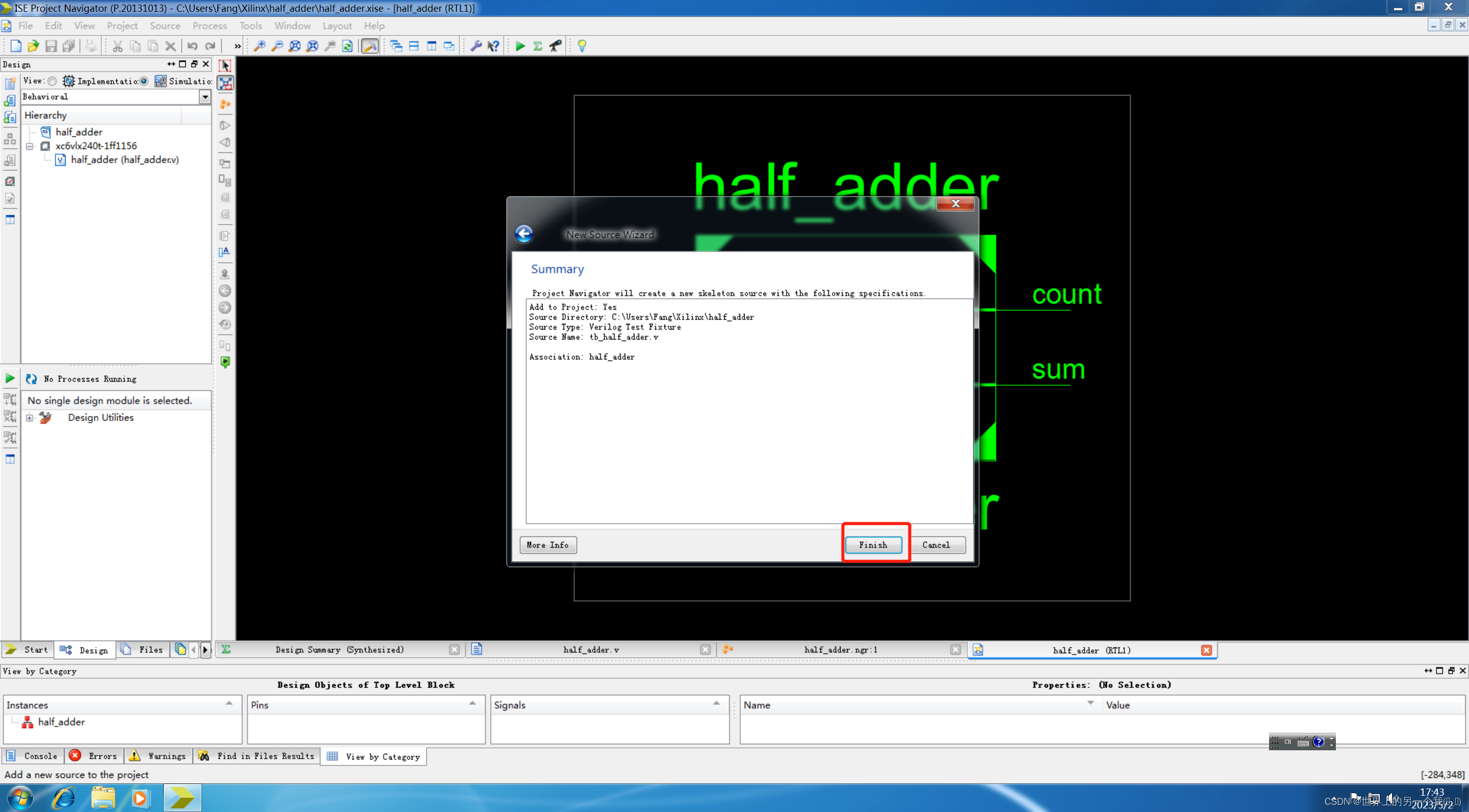

16、检查信息,没有问题点击finish

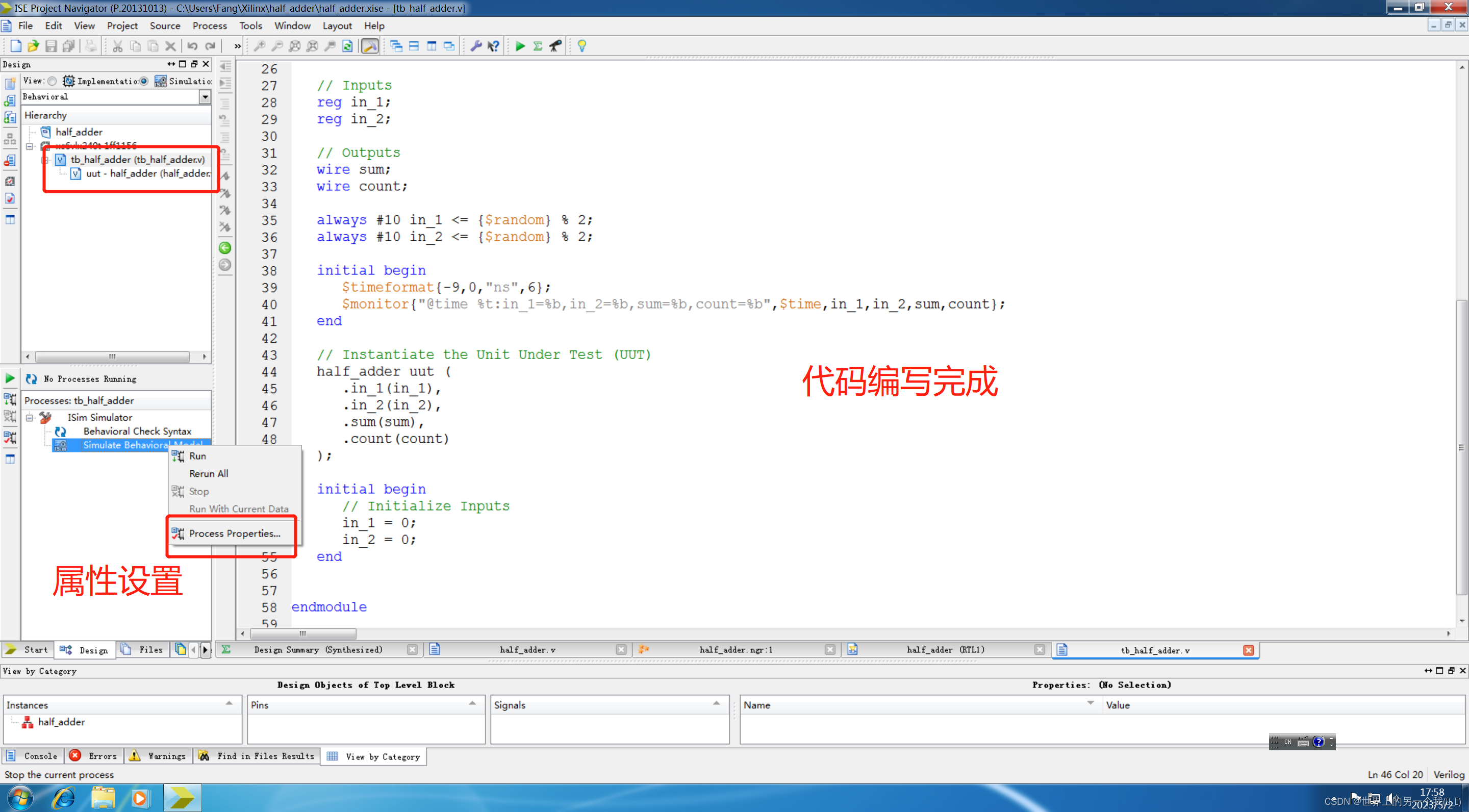

17、编写测试代码,完成后选中tb文件,设置仿真属性

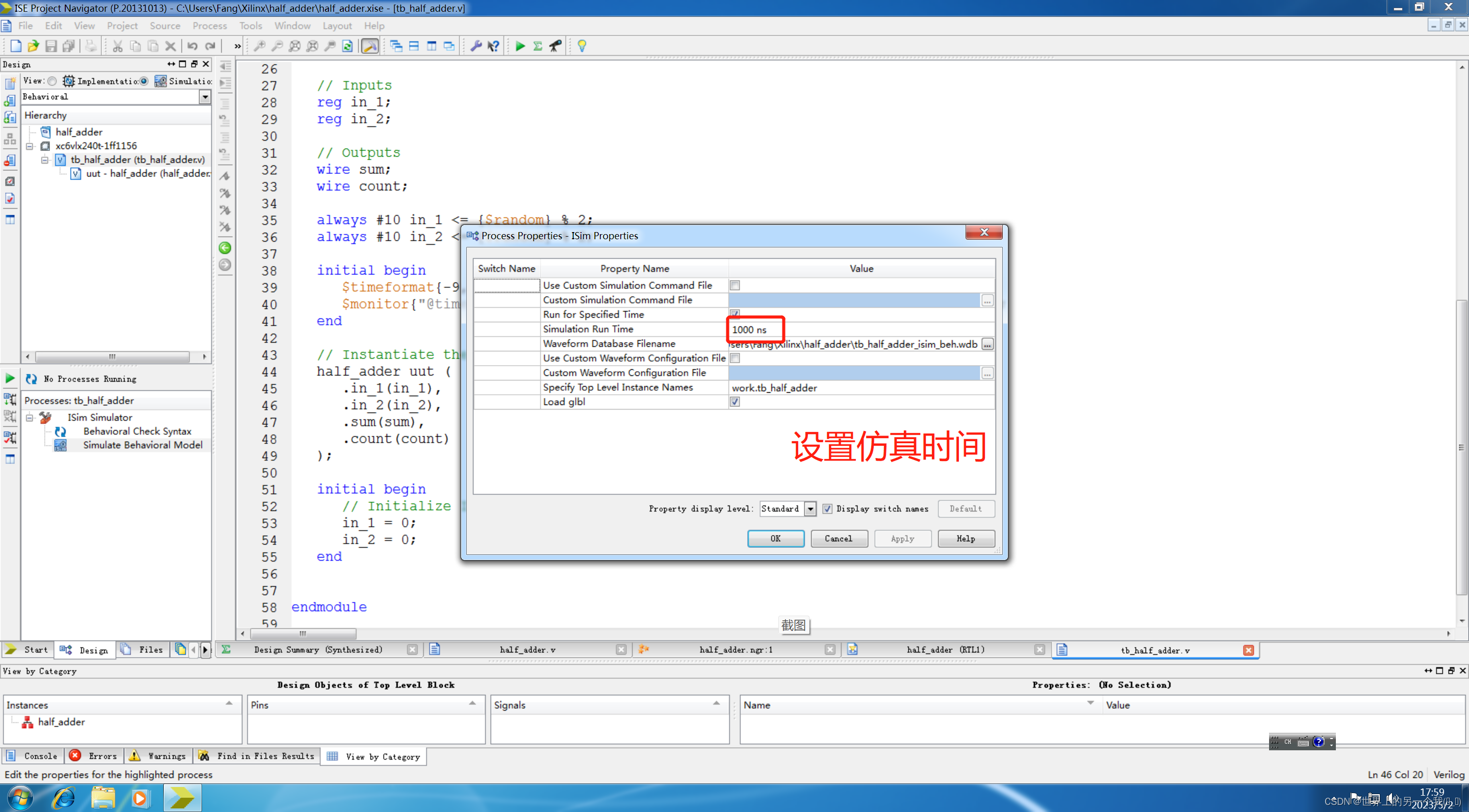

18、可以在属性设置中设置仿真时间

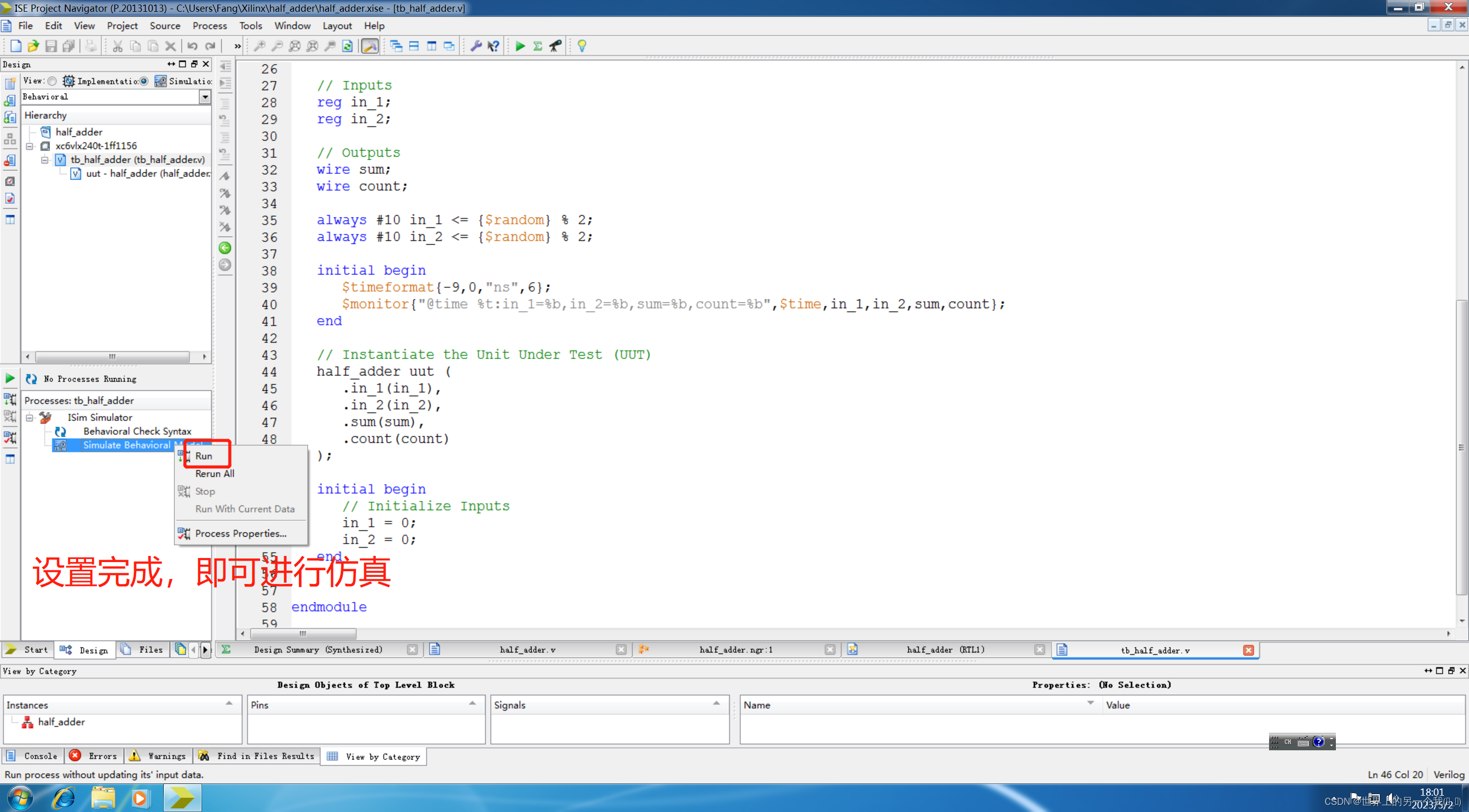

19、设置完成即可进行仿真

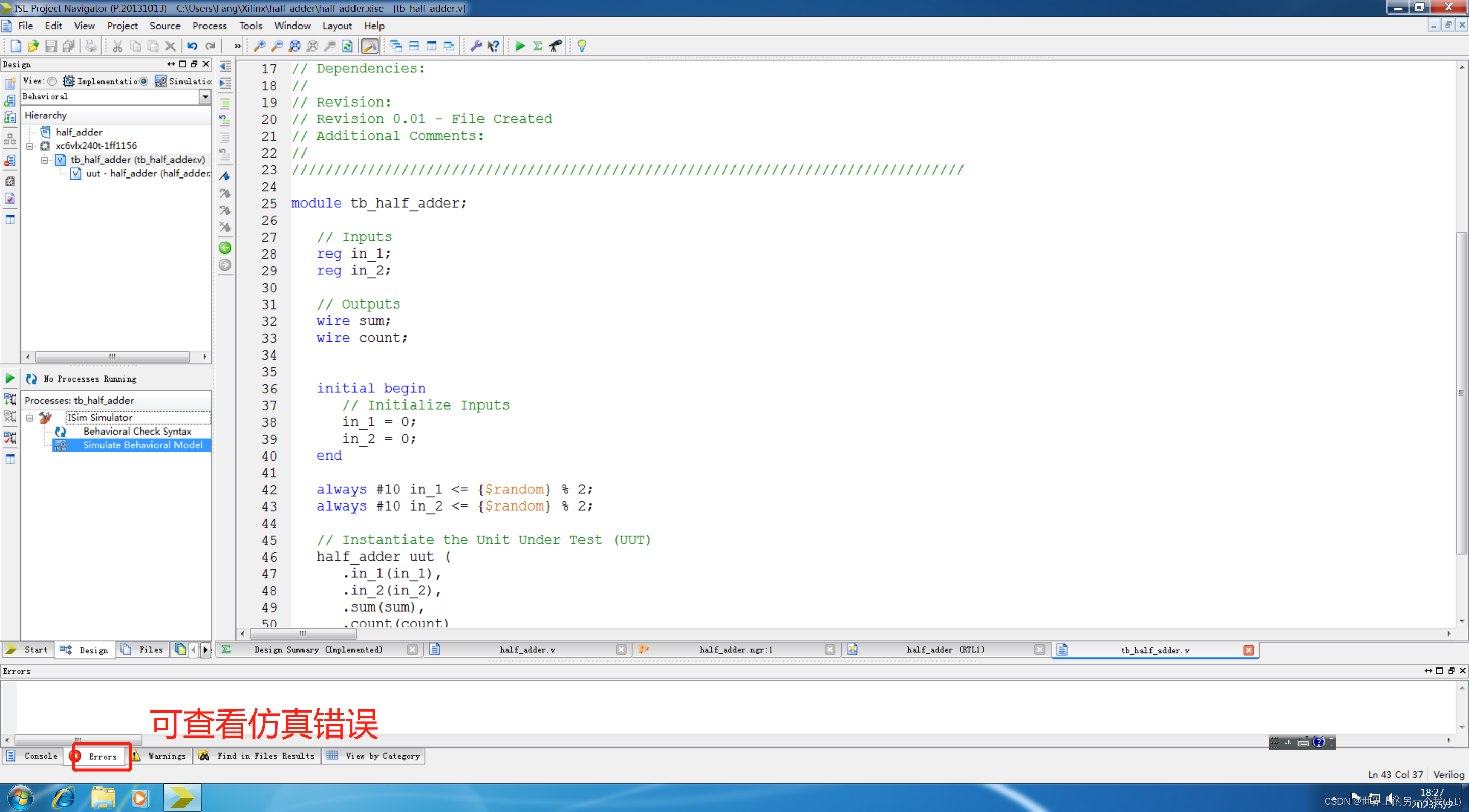

20、如果仿真不通过,可以在下方点击error查看仿真错误并修改代码

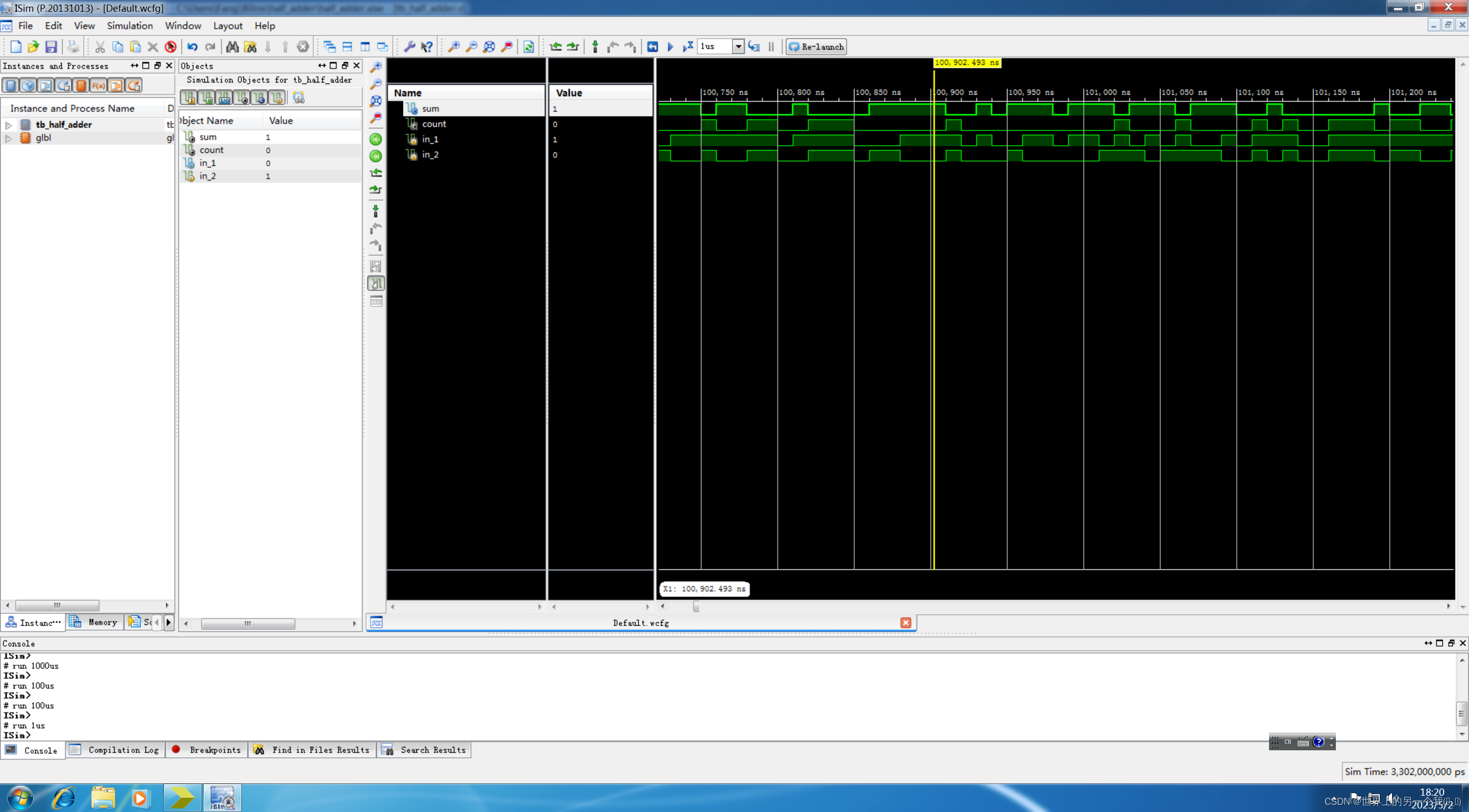

21、代码无误,会自动启动ISE Simulator软件,并得到如图所示的仿真结果。

1146

1146

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?