1 AXI总线是什么

AXI(Advanced eXtensible Interface)是一种总线协议,该协议并非Xilinx公司提出的,而是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分。最新的AXI4总线于2010年在AMBA4.0版本中发布。

2 AXI分为几种类型

AXI4总线协议存在3中类型的接口分别为:

(1)AXI4:标准型AXI4总线类型,是一种面向地址映射的接口,支持突发传输数据,最大允许256个时钟周期的数据突发长度。该接口主要面向高性能地址映射通信的需求。

(2)AXI4-Lite:属于轻量级的地址映射单次传输接口,每次仅支持单次的数据传输,由于功能较少,所以占用的资源也较少,该协议适应于吞吐量较小的地址映射通信总线。

(3)AXI4-Stream:顾名思义,属于流媒体传输形式,该协议去掉了地址传输功能,允许无限制的数据突发传输,而无需进行地址映射的考虑,主要面向于高速数据传输。

| 通道名称 | 通道功能 | 数据流向 |

|---|---|---|

| read address | 读地址通道 | 主机——>从机 |

| read data | 读数据通道(包括数据通道和读相应通道) | 从机——>主机 |

| write address | 写地址通道 | 主机——>从机 |

| write data | 写数据通道(包括数据通道和每8bit一个byte的写数据有效信号) | 主机——>从机 |

| write response | 写相应通道 | 从机——>主机 |

3 AXI的工作模式

3.1 AXI通道说明

AXI总线共分为5个通道,分别为读地址通道、读数据通道、写地址通道、写数据通道和写应答通道。

(1)读地址通道(AR channel):包含ARVALID,ARADDR,ARREADY信号;

(2)读数据通道(R channel):包含RVALID, RDATA,RREADY,RRESP信号;

(3)写地址通道(AW channel):包含AWVALID,AWADDR,AWREADY信号;

(4)写数据通道(W channel):包含WVALID,WDATA,WSTRB, WREADY信号;

(5)写应答通道(B channel):包含BVALID,BRESP,BREADY信号;

由于AXI4-Stream无需通过地址进行映射,所以AXI4-Stream总线的接口组成有:

(1)ACLK信号:总线时钟,上升沿有效;

(2)ARESETN信号:总线复位,低电平有效;

(3)TVALID信号:主机告诉从机数据本次传输有效;

(4)TREADY信号:从机告诉主机做好传输准备;需要注意的是,只有当TVAILD和TREADY信号同时为高电平时,此时握手成功,才传输数据。

(5) TLAST信号:主机告诉从机该次传输为突发传输的结尾;当TLAST为高时,表明当前数据是最后一次传输。

(6)TDATA信号:数据,可选宽度32、64、128、256bit;

(7)TKEEP信号:类似于字节修饰符,表示数据是有效的。

(8) TSTRB信号:每bit对应TDATA的一个有效字节,宽度为TDATA/8;

(9)TUSER信号:用户定义信号,宽度为128bit。

3.2 AXI总线数据传输实现过程

3.2.1 读数据实现过程

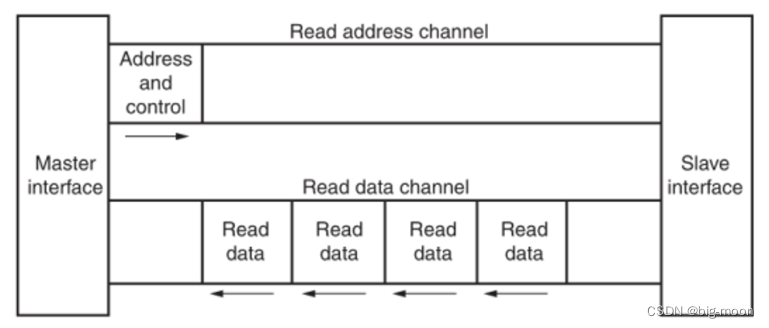

下图为读数据的流程框图示意图,从上述内容中是否存在疑惑为何读数据没有读反馈信号,从这个示意图中可以得出结论。在主机向从机发送地址,从机向主机发送数据的同时其实已经包含了反馈信号。

主机在读地址通道上给出要读取的数据的地址和控制信息(当突发读取多个数据时,给出数据存储的首地址和突发长度),从机收到后在将数据通过读数据通道发送给主机。

3.2.2 写数据实现过程

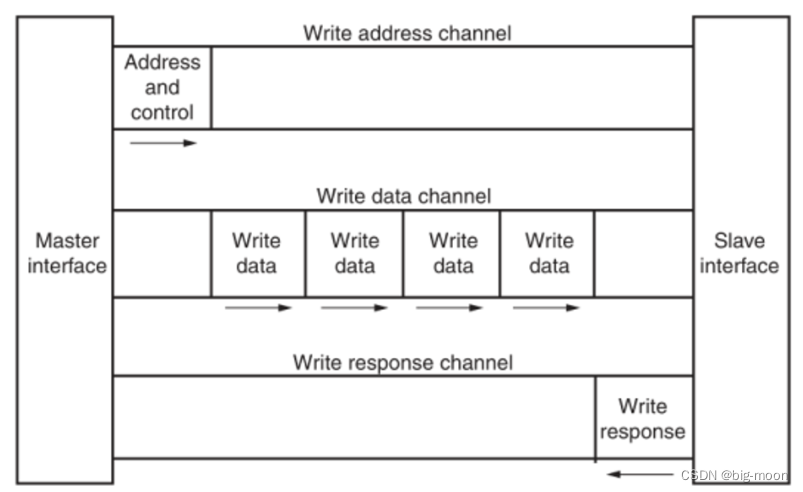

下图所示为写事务使用写地址、写数据和写响应通道的方式,主机首先向发送写控制,然后发送要写入的数据,从机在收完本次写事务的数据后给出写响应信号代表接收完成。

3.2.3 AXI4握手机制

握手机制中有三种情况valid信号先到,ready信号先到以及两个信号同时到。下面对这三种情况进行具体分析:

VALID信号先到

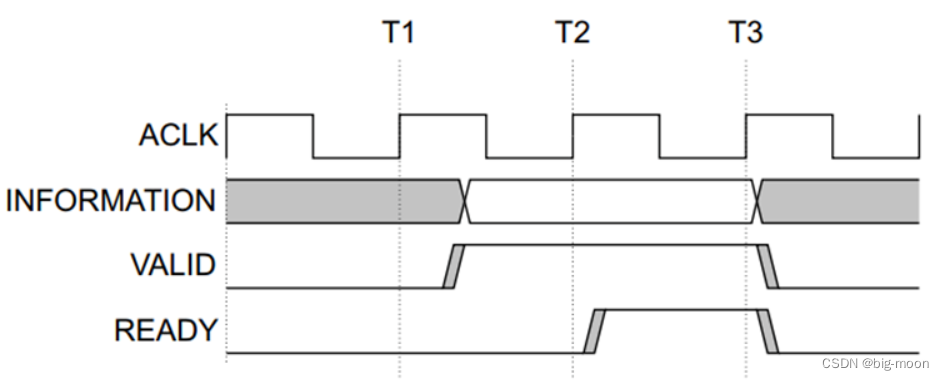

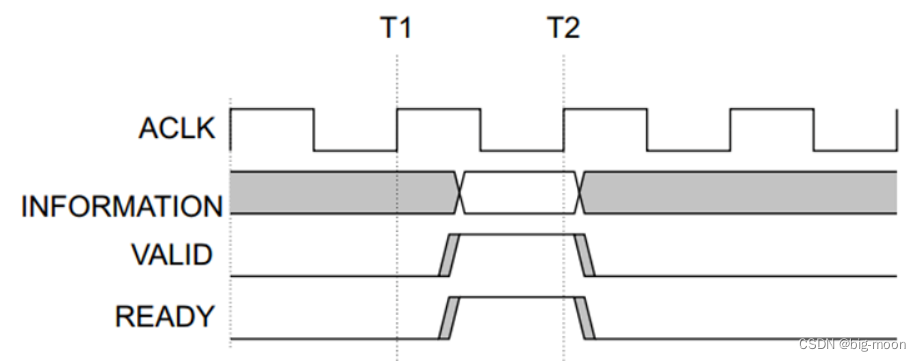

时序图如下图所示:

源设备在T1时刻之后给出地址、数据或控制信息(白色表示有用),在T1时刻之后VALID信号开始有用。在 T2时刻时钟上升沿处,系统知道了信息有效。目标设备在T2时刻之后才发送ready信号,错过了T2时刻上升沿,所以源设备必须保持它携带的信息稳定直到T3时刻,此时握手信号都为高电平,信息开始传输,真正发生传输的是在T3时刻上升沿。

源端必须在令VALID信号有效之后等待READY信号有效,一旦VALID有效,源端必须等待握手发生,即在保持VALID不变的情况下,等待目的端的READY信号有效。VALID高低电平,不由READY信号决定,仅仅由信息的有用性决定。

READY信号先到

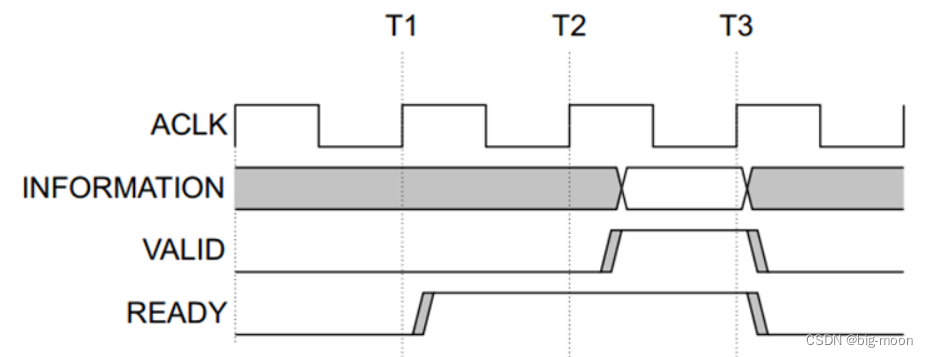

时序图如下图所示:

此时T1时刻之后READY信号开始拉高,到了T2系统开始知道目标设备准备好了。T2之后给出地址、数据或控制信息,VALID开始有效,T3时刻到后握手完成,开始进行数据传输。这里我们可以看见目标设备其实可以一直把这个READY信号拉高,因为只要目标设备寄存器有空间就行。这个可以和第一种情况区分一下,第一种情况说的是,VALID信号高低也好其实完全是取决于信号是否有用,这时候如果VALID先高,则必须完成握手后,才能拉回去。但是这种情况,在VALID有效前,即使READY已经有效,也可以再次令READY无效。 READY拉高拉低标准取决于目标设备,和VALID无关。

两个信号同时到

时序图如下图所示:

在这种情况下,两端的VALID/READY信号同时有效,则传输立刻在下一个时钟周期开始。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?