本文章基于模拟项目开发的流程,假设当前接收到一个高速PCB开发的任务,我们如何开展PCB设计与仿真分析。以下案例是采用软件Cadence 2023和Sigrity 2023版本。

1、规划准备

分析PCB设计相关的设计需求,制定PCB设计计划,按如下清单顺序进行检查。

●分析需求:按项目和主导工程师的要求,要开展PCB绘制以及仿真,包括前仿真,后仿真,SI/PI应进行的分析点,都进行一次分析。

●得到网表:已接收到一份网表,已导入Allegro。

●评估开发周期:PCB设计周期评估,不包含后仿真的时间。如图1-1所示(以下表格评估无参考意义)。

图1-1 PCB设计周期评估

●制定计划:按耗时评估制定PCB设计计划

●约束管理器规则准备:在约束管理器中建立好 bus、XNET、DPR等的线组。

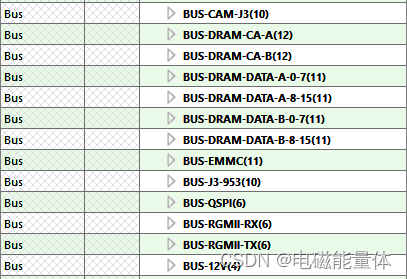

○Bus:主电源信号(12V)、RGMII-RX、RGMII-TX、QSPI、MIPI-953、eMMc、MIPI-CAM、DRAM-CA-A、DRAM-CA-B、DRAM-DATA-A-0-7、DRAM-DATA-A-8-15、DRAM-DATA-B-0-7、DRAM-DATA-B-8-15,共13组。如图1-2所示。

图1-2 建立Bus

○Xnet:Xnet数量多,完成创建。如图1-3所示。

图1-3 部分Xnet网络

○DPr:共23对差分对,完成创建。如图1-4所示。

图1-4 差分对建立

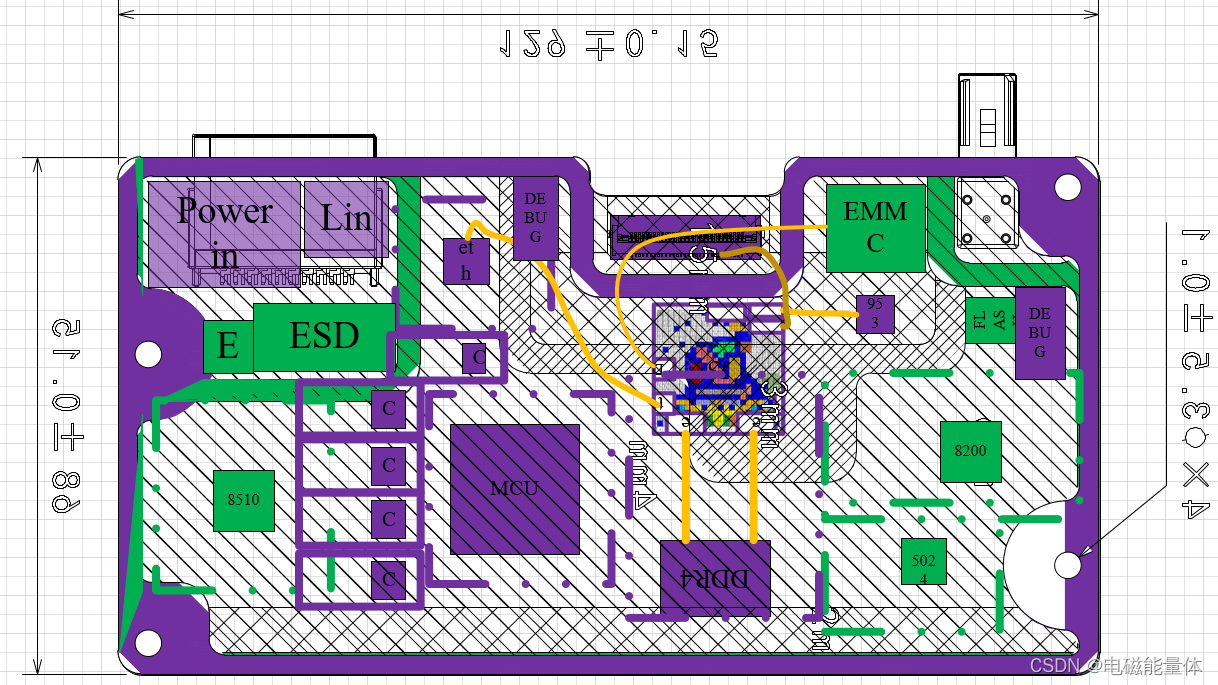

●结构布局评估:在结构评估及原理图方案制定阶段,应该进行首次的大致布局评估,可以基于VISIO,进行大概评估。如图1-5所示。

图1-5 项目的结构评估布局图

布局评估小结:

① 热分析:综合项目前期的准备的热仿真数据。进行分析,eMMc的位置尽量离SOC远些, eMMc容易被热传递,容易超过温度上限,放在SOC的不同面可以减少热传递影响。 此处需要进行一次热仿真分析。

② EMC分析:ESD靠近各接口。eMMc靠近板边缘,在RE和RI测试时,比其它模块风险高些,但考虑金属外壳密闭性的情况下,评估试验可PASS。

③ 布局合理性:CAN的走线比较别扭。MCU附近空间太密。SOC必须放在底层的原因是顶层的位置有摄像头模组,无法做金属散热凸台。

④ 高速走线方向的合理性:LPDDR4走线方向合理,eMMc有些绕,MIPI-953合理,RGMII合理,MIPI-CAM太绕。

●禁布图:经过大致评估,目前结构尺寸限高等可接受,禁布图PASS。

综合以上的评估,经主导工程师的讨论,确定初布局图可行,准备阶段完成。

进入下一阶段(仿真模型的获取与验证)。

本文详细描述了接收到高速PCB开发任务后,如何通过需求分析、网表处理、周期评估、约束管理器设置、结构布局评估以及热/EMC分析来规划PCB设计。最终确认初步布局并进入仿真模型获取与验证阶段。

本文详细描述了接收到高速PCB开发任务后,如何通过需求分析、网表处理、周期评估、约束管理器设置、结构布局评估以及热/EMC分析来规划PCB设计。最终确认初步布局并进入仿真模型获取与验证阶段。

1223

1223

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?