1. DDR的基础知识

1.1 ROM和RAM

RAM:随机存取存储器。与CPU直接进行数据交互的内部存储器,随时读/写,常常作为操作系统或程序的临时数据存储,掉电不保留数据。常见有:SRAM、SDRAM、DRAM、DDR。

其中,SRAM是静态存储器,不需要刷新电路来保存内部数据;DRAM是动态随机存储器,需要不断的刷新电路来保存数据。

ROM:只读存储器。事先写好的,里面的数据不可更改,只能进行读操作,不能进行写操作,掉电后其中的数据也不会改变。常见的有SSD、HDD、flash。

1.2 DDR3的特点

DDR3全称是第三代双倍速率同步动态存储器。

特点:①掉电无法保存数据,需要周期的刷新;②双沿传输:时钟上升沿河下降沿都会传输数据;③突发传输,突发长度 Brust Length 一般为8。

1.3 DDR3的寻址方式

DDR3的存储:Bank地址、行地址、列地址。

DDR寻址的流程是先指定Bank地址,再指定行地址,然后指列地址。可以理解为一个好多页表格的本子,先确定要读/写哪个表格(Bank group),然后看表格中的哪一行(Row),选择哪一列(Column)。

1.4 DDR3容量

容量计算:Bank数量 x 行数量 x 列数量 x 存储单元的容量。

举个列子:假如Bank位宽为[2:0],也就是8个BANK,行地址位宽[13:0],;列地址位宽[2:0],存储单元容量为16bit,那么,DDR3的容量为:2^3 x 2^14 x 2^3 x 16bit。

1.5 DDR3带宽

带宽:2*DDR3_CLK*DATA_WIDTH

由于是DDR方式传输数据(上升和下降沿都传输),所以芯片的一根数据线上的传输速率 = 2*800Mhz = 1600MT/s。其实就是1600Mbit/s;

带宽就是16根数据线同时传输的数据速率 = 1600Mbit/s x 16 = 25600Mbit/s = 3200Mbyte/s = 3.125GByte/s

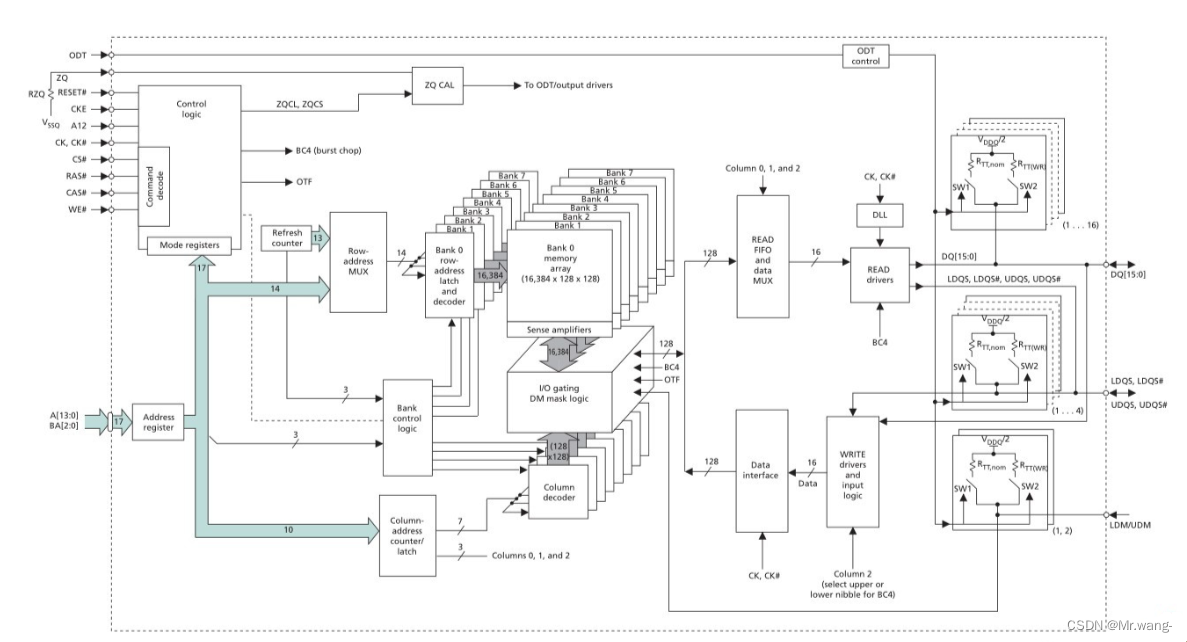

2. DDR3结构

2.1 DDR3结构框图

以下这个DDR3是BANK地址位宽为BA[2:0];数据位宽配置为[15:0];行地址A[13:0],列地址[9:0],则 2^3 x 2^14 x 2^10 =128M,128M x 16bit = 256M Byte。

2.2 接口描述

| 接口 | 类型 | 功能描述 |

| A[14:0] | 输入 | 地址输入: 在激活时提供Row地址,在读/写命令时提供Column地址A10,在加载模式寄存器命令时提供op-code。 Row地址:A[14:0] Column地址:A[9:0] A12/BC#:当在模式寄存器中是能后,A12在读取/写入命令时决定是否执行突发突变(brust chop)功能 |

| BA[2:0] | 输入 | BANK地址输入: 在激活、读取、写入、预充电命令操作时,提供BANK地址; 在加载模式寄存器命令时,决定设置哪种模式寄存器 |

| CK、CK# | 输入 | 差分时钟输入: 所有地址和命令输入信号,在CK的上升沿和CK#的下降沿交叉点锁存; 输出数据DQ、DQS、DQS#参考CK和CK#的交叉点 |

| CKE | 输入 | 时钟使能输入: CKE为高时,使能时钟正常工作; CKE为低时,使能Power-down模式或自刷新功能 |

| CS# | 输入 | 芯片选择使能: CS#为高时,芯片不使能,屏蔽外部所有命令; CS#为低时,芯片使能,响应外部命令 |

| LDM、UDM | 输入 | 写数据掩码: 在写操作时,如果DM信号为高,则写入数据就会被屏蔽;如果DM信号为低,则写入数据就会正常锁存。 LDM控制DQ~DQ7,UDM控制DQ8~DQ15 |

| ODT | 输入 | 终结电阻控制: ODT使能DDR3内部的终结电阻,为高时有效,优化DQ/DM/DQS的信号质量 |

| RAS#、CAS#、WE# | 输入 | 命令输入: RAS#、CAS#、WE#定义DDR3芯片的操作命令 |

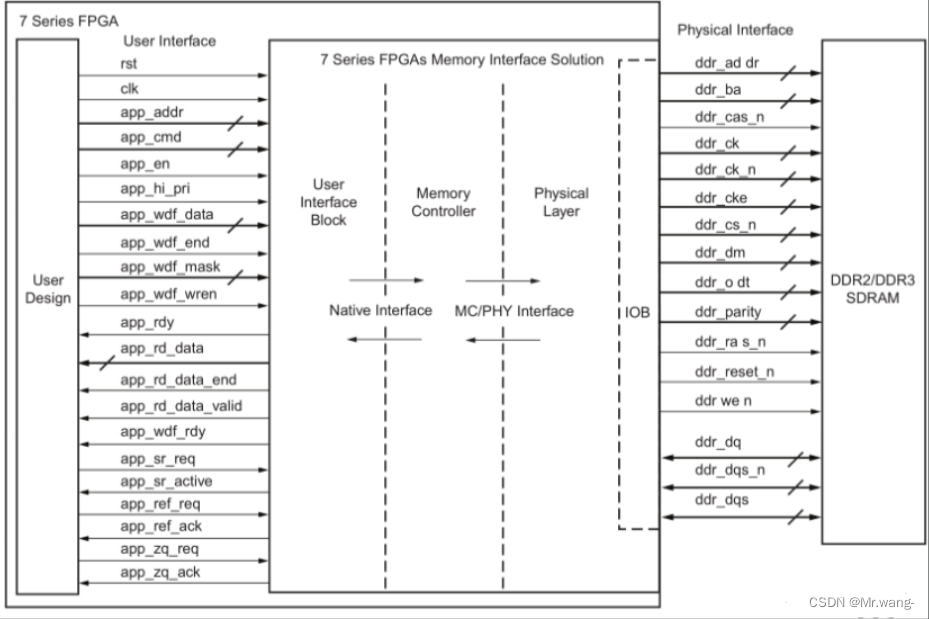

3. MIG IP核

3.1 基本结构(native接口)

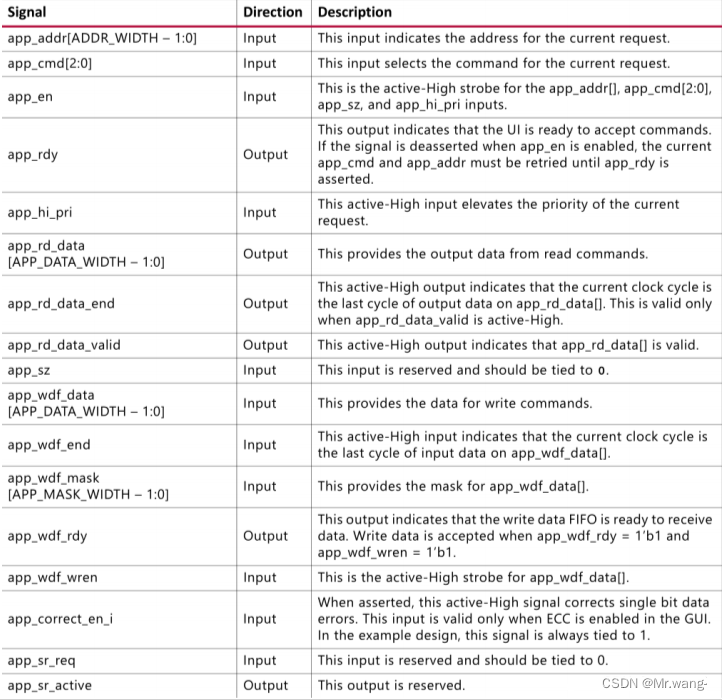

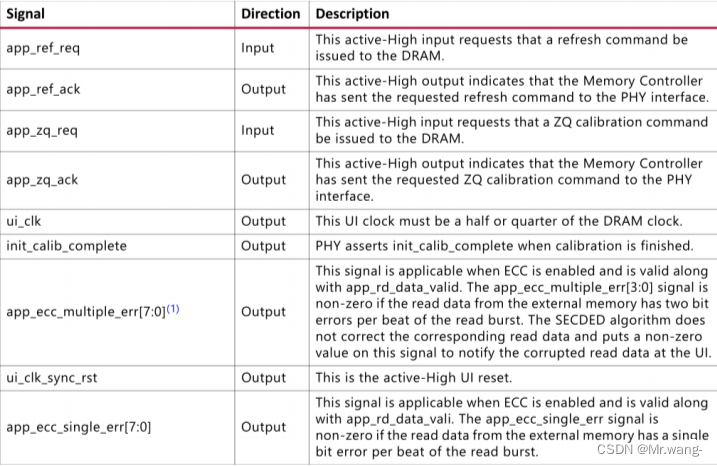

3.2 接口描述

4. 时序

4.1 写入数据时序图

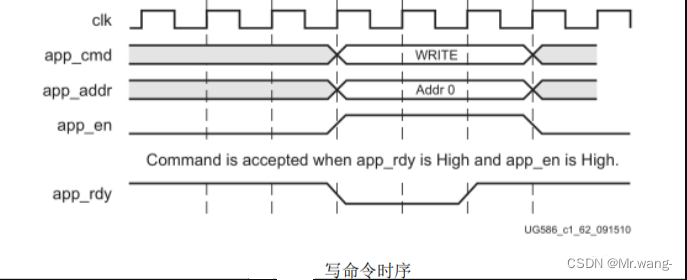

DDR3 的读或者写都包含写命令操作,其中写操作命令(app_cmd)的值等于 0,读操作 app_cmd 的值等于 1。

根据写命令时序,首先检查 app_rdy,为高则表明此时 IP 核命令接收处于准备好状态,可以接收用户命令,在当前将时钟拉高 app_en,同时发送命令(app_cmd)和地址(app_addr),此时命令和地址被写入。

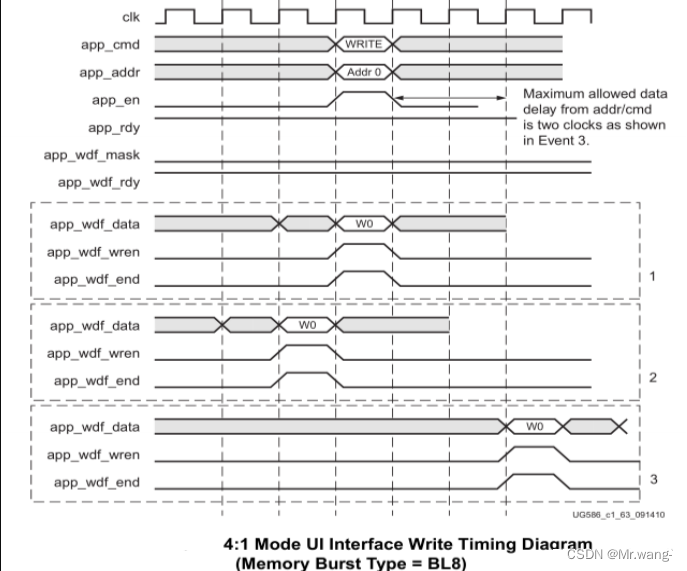

由时序图可以看出,写入数据有三种情形可正确写入DDR3:①写数据时序和写命令时序发生在同一拍;②写数据时序比写命令时序提前一拍;③写数据时序比写命令时序至多延迟晚两拍。

当写入数据时,首先需要检查 app_wdf_rdy,该信号为高表明此时 IP 核数据接收处于准备完成状态,可以接收用户发过来的数据,在当前时钟拉高写使能(app_wdf_wren),给出写数据(app_wdf_data)。发起的写命令操作就可以成功向 IP 核写入数据。app_wdf_mask用来屏蔽写入数据,该信号为高则屏蔽相应的字节,为 0 不屏蔽任何字节。

4.2 读取数据时序图

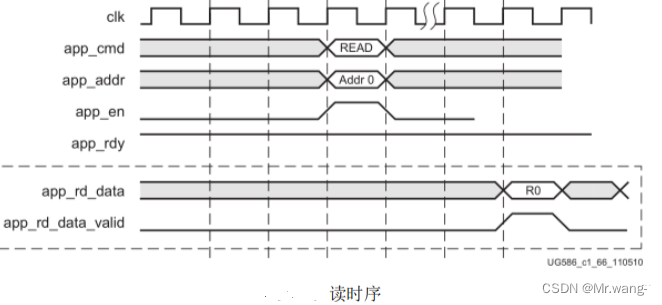

由用户发送读命令后,必须等待数据有效信号(app_rd_data_valid)拉高。当该信号处于高电平时,表示此时数据总线上的数据是有效的返回数据。在发送读命令后,有效的读取数据将会在一段时间延迟后才会在数据总线上出现。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?